1 多周期路径(Multicycle path)

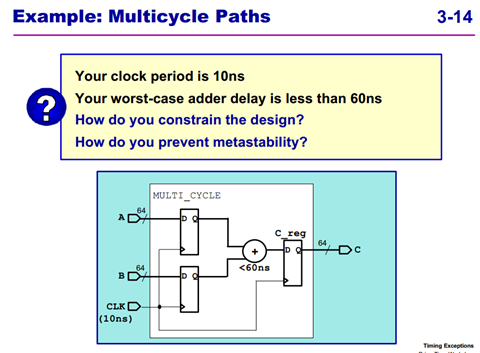

使用场景

默认情况下PT的行为

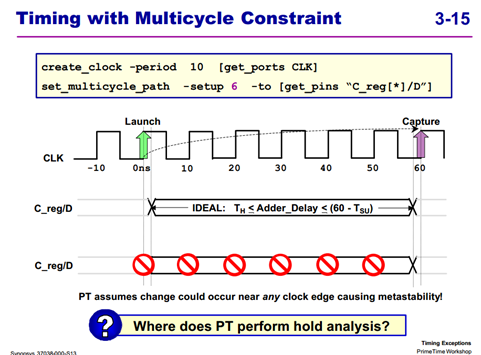

可以看到,setup的检查是在60ns位置,符合预期,而hold的检查发生在50ns的位置,显然不是我们想要的。

上例给出了一个6个周期的路径,理想情况下希望Th<Addre Delay<60-Tsetup,但是默认情况下Hold的检查

是在检查Set up时钟沿的上一个时钟沿,这显然不是我们预期的,因此需要通过命令设置正确的Hold Constraint,

此例为 set_multicycle_path -hold 5 -to ……

通过命令修改hold的检查,Mh=Ms-1

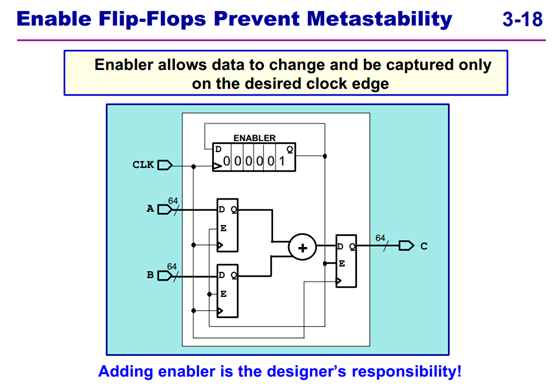

解决亚稳态问题

PT会假定在任何一个时钟沿的跳变都会产生亚稳态,避免亚稳态的方法是添加使能逻辑控制capture clock的采样,

也就是控制它在第6个时钟沿才采样,其他时钟沿不采样。

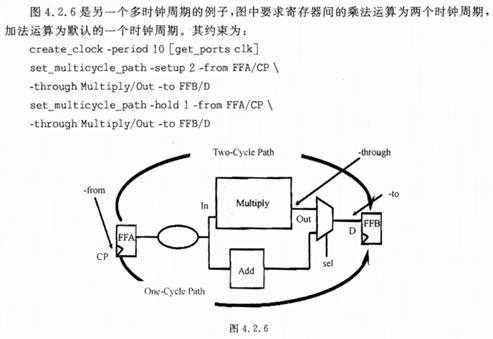

one more example

2 虚假路径(False path)

定义

false pth就是我们进行综合分析时,不希望综合工具分析的那些路径

set_false_path -from

它只移除确认的路径约束。

使用场景

- 从逻辑上考虑,与电路正常工作不相关的那些路径,比如测试逻辑,静态逻辑等

- 从时序上考虑,我们在综合时不需要分析的那些路径,比如跨越异步时钟域的路径

需要注意的几个点

(1)当定义虚假路径时避免使用通配符,否则导致PT生成大量的虚假路径。

例如:set_false_path -from ififo_reg*/CP -to ofifo_reg*/D,如果这两个寄存器为16bit,

则会生成大量不必要的虚假路径

(2)避免对多个虚假路径使用-through选项,尽量找到一组确认的虚假路径所共享的共同单元,

通过set_disable_timing命令禁止这个单元的时序弧。

(3)不要为属于单独的异步时钟域的寄存器定义虚假路径。

例如:set_false_path -from [all_registers -clock CLK1] -to [all_registers

-clock CLK2],该命令迫使PT枚举设计中的每个寄存器。推荐的方法是:

set_false_path -from [get_clocks CLK1] -to [get_clocks CLK2]

3 屏蔽时序弧(Disable timing)

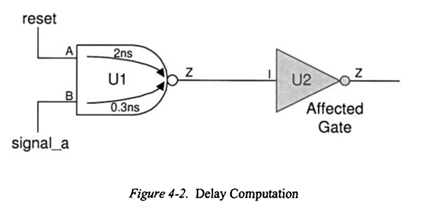

(1)分别禁止时序弧

由于PT使用产生最长延迟的时序弧来计算某一单元的延迟,这有时会产生不需要的虚

假延迟值,可以禁止某个单元的时序弧以阻止PT在计算路径时使用这个弧。如下图,由于

reset信号的转换时间比signal_a更长,因此2ns将被用于U2的输入转换时间,可采用以下

命令禁止U1单元A到Z的时序弧:set_disable_timing U1 -from A -to Z。

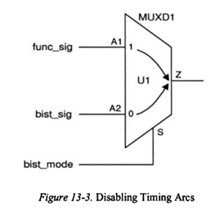

禁止个别单元时序弧的另一个原因是防止PT选择错误的时序路径,如下如所示:

当进行STA检查功能模式下的时序时,PT可能会选择错误的路径(由A2到Z),可用

如下命令禁止:set_disable_timing -from A2 -to Z {U1}

(2)情况分析

上述情形的另一个解决方案是对设计进行情况分析,通过给bist_mode信号设置一个逻

辑值,禁止/使能与bist_mode信号相关的所有时序弧,可用如下命令实现:

set_case_analysis 1 bist_mode。bist_mode=1迫使PT禁止由A2到Z的时序弧,

并使func_sig信号能够传播。与set_disable_timing想比,set_case_analysis的解决方案更好,

原因在于一个命令可以用于分析在正常模式或测试模式下的整个设计。