遇到各种各样的客户,就会遇到各种各样的问题----这是FAE这个岗位性质决定的。

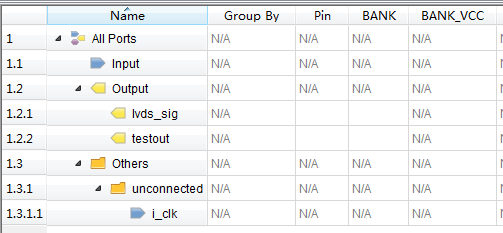

客户用diamond3.7,一直给我抱怨说你们的lattice的东西怎么那么烂,连管脚都没法绑定。具体问题描述如下图1,他的时钟脚一直处于unconnected状态(ERROR - Port 'i_clk' is unconnected.),时钟都进不来那还玩什么?

接着把简化的代码在altera的平台上也试了一下,报的也是一个非常严重的警告,如图2所示。在Xilinx平台上测试也是一样的效果。所以说不是我们lattice平台的问题,只是说我们lattice为了防止后续的设计出现问题,在综合阶段就告知客户这是一个错误(其他几家平台报的是警告),好让客户早点修改。

但是我们还没有找到问题的根源,所以我拿到出问题的代码查看了底层,看综合的结果,如图3所示。综合的结果很显然了,输出的值为固定值1,那么尽然是固定的值,我时钟还有啥意思,所以自然就无法绑定了。

接下来我们分析下这段出问题的代码(部分代码)

module test(

input wire i_clk,

output wire lvds_sig,

output wire testout

);

assign lvds_sig = r_lvds_sig ;

always@(posedge i_clk)

cnt <= cnt + 1;

always@(posedge i_clk)

if(cnt == 18'h1ff)

r_lvds_sig <= 1;

always@(posedge i_clk )

if(cnt == 18'h1f0)

add_num <= 1;

assign testout = |cnt ||add_num ;

对于按规则办事的工程师来说,一看,怎么都没有复位呢?实际上问题就出在没有复位。因为没有复位,综合工具就默认为add_num初始值是1,

always@(posedge i_clk )

if(cnt == 18'h1f0)

add_num <= 1;

等价于

always@(posedge i_clk )

if(cnt == 18'h1f0)

add_num <= 1;

else

add_num <= add_num;

也就是说add_num 固定为1,那么输出testout 也固定为1,类似的也可以推到出lvds_sig 也固定为1,既然所以输出的值都固定为1,那么还有我的时钟有何意义,所以三家FPGA厂商自然就报个错误或者警告提醒你一下。所以在设计的时候,一定要加上复位,不管你是同步还是异步复位。加了复位输出的值就会产生变化,就不会出现这样的错误了。

以上解释应该很清楚了,如有疑问请联系扣扣:825972925

图1 图2

图3