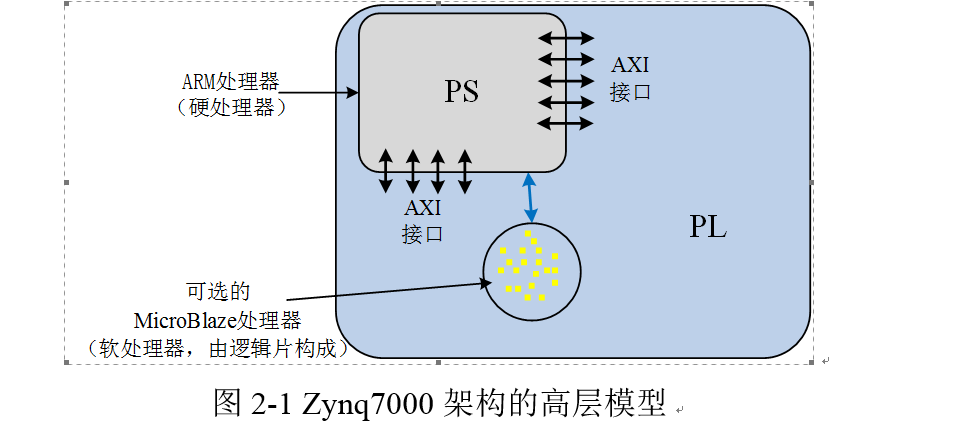

Zynq7000系列是基于APSOC的可拓展处理平台,它的本质特征是将一个双核ARM Cortex-A9处理器和一个可编程的FPGA芯片集成到一个片上系统中。在进行Zynq7000的详细说明前,本节首先对架构的高层模型进行介绍,如图2-1所示。

通常将ARM处理器和各种存储外设资源称为处理系统(Processor System,PS),.将FPGA部分称为可编程逻辑(Programmable Logic,PL)。ARM Cortex-A9是一个应用级处理器,支持类似Linux操作系统的运行。FPGA采用的Xilinx7架构实现了工业标准的AXI接口,该接口在ARM和FPGA之间形成高效耦合,减少了分立芯片产生的额外功耗,不仅实现了高带宽、低延迟的连接,同时带来了物理尺寸和生产成本的降低.

值得一提的是,Zynq7000的PL部分可以配置一个软处理器MicroBlaze。Micro-Blaze是由可编程逻辑部分的单元组合而成[19],也就是一个MicroBlaze的实现和部署与FPGA中一个普通IP核是等价的。软处理器可以和ARM协同工作,负责协调特定底层功能和系统之间的配合,将一些要求不高的任务从ARM Cortex-A9处理器上脱离出来,提升系统的性能。

Zynq7000的PL部分用来实现高速逻辑运算和并行数据流处理的子系统是非常理想的,PS部分支持软件控制或者操作系统。这意味着基于此平台,大多数系统的设计都可以根据功能进行软件和硬件的划分,使得PS和PL都可以发挥各自的优势,从而让整个系统呈现出最佳性能。Zynq7000片上系统的内部架构如图2-2所示

PS部分的资源主要包括[14][16][20]:

(1)应用处理单元(APU):双核ARM Cortex-A9处理器,最高工作频率可达1GHz。两核中任意一核均包含一个一级cache(分为数据和指令两个部分,每个都是32KB)、一个内存管理单元(MMU,在虚拟地址和物理地址之间做翻译)。另外,两个核共用了一个512KB 的二级cache来存放指令和数据。其他的系统资源还包括NEONTM媒体处理引擎和浮点单元(FPU)、片上存储器(OCM)、一致性控制单元(SCU)、中断控制器等。其中SCU在ARM核和二级cache及OCM存储器之间形成了桥连接,还部分负责与PL对接。

(2)AXI接口,Zynq里的PS和PL部分之间的主要连接形式是AXI接口,下文会做详细阐述。

(3)存储器接口,支持16位/32位宽的DDR3、DDR2以及四线SPI控制器等。

(4)I/O外设接口,包括复用输入/输出引脚(MIO)、扩展MIO(EMIO,通过共用PL的I/O资源实现)、标准通信接口和通用输入/输出引脚(GPIO)。此外,还有以太网控制器(支持10Mbps、100Mbps和1Gbps模式)、USB控制器、SD/SDIO控制器、基于4线的SPI控制器、CAN控制器、UART控制器和I2C控制器等。

PL部分的资源主要包括[21-23]:

(1)通用FPGA逻辑部分。主要包括逻辑片和可配置逻辑块,另外还有用于接口的输入/输出块。FPGA逻辑部分及其组成单元如图2-3所示。

(2)XADC块。这是一个专用的模拟-数字转换器(Analogue to Digital Converter,ADC)混合信号硬件,具有两个独立的12位ADC,每个可以以1Msps的采样频率对外部输入的模拟信号进行采样。对XADC的控制是用位于PS内的PS-XADC接口控制块实现的,而且PS-XADC控制块本身可以由APU进行编程控制。

(3)时钟:PL接收来自PS的四个独立的时钟输入,另外还能产生和分发它自己的与PS无关的时钟信号。这个独立的PL资源与7系列FPGA里的是等价的。