一、什么是亚稳态

首先康康百度怎么解释亚稳态的:亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。

根据百科解释,可以提炼以下特点:

1)亚稳态违背了时序,无法在规定时间成为稳态。

2)亚稳态输出不确定,但是会传给后一级触发器。这会导致后级电路出错。所以亚稳态危害很大。

3)亚稳态最终都会稳定下来,但需要较长的时间。

二、亚稳态是怎么产生的

根据1.1,我们知道亚稳态是由于违背了触发器的建立(Tsu)和保持时间(Th)而产生的。

首先解释几个基本概念:

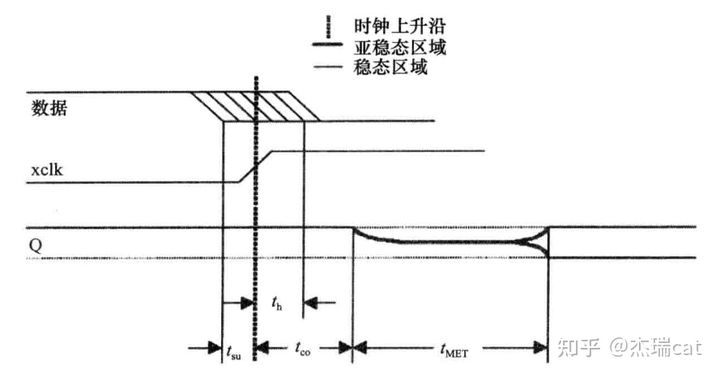

Tsu为建立时间:是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被稳定的打入触发器,Tsu就是指这个最小的稳定时间。

Th为保持时间:是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被稳定的打入触发器,Th就是指这个最小的保持时间。

Tco为输出时间:是触发器在clk时钟上升沿到来之后需多长的时间才能稳定输出的的时间。

Tmet:亚稳态输出恢复到稳定状态所需的超出Tco的额外时间称为稳定时间,即经过这段时间,亚稳态变成稳态了。

如果数据传输中不满足触发器的Tsu和Th,就会造成数据不稳定,从而导致亚稳态。

其核心在于:数据不稳定

三、如何避免亚稳态

如果规定一个特定时间长度,数据在这个时间长度内还不能稳定,则会造成亚稳态。那么定义这个时间长度为亚稳态窗口。

如上面所述,只要满足了建立时间和保持时间,就能避免亚稳态。对于亚稳态窗口来说,窗口越大,进入亚稳态的概率也越大。

在FPGA/IC设计当中,异步信号、跨时钟域信号都是亚稳态高发区。

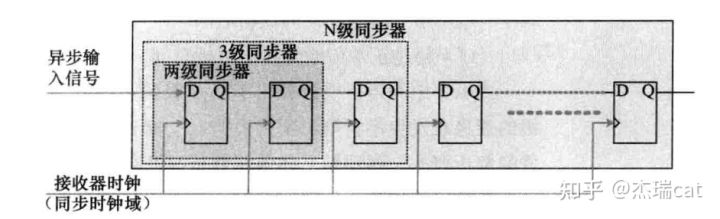

对于异步信号,一般采用多级同步器,可以避免亚稳态的发生。

相当于拉长了整体的Tsu和Th,让数据有足够的时间稳定下来。

对于跨时钟域信号,采用FIFO对跨时钟域数据进行缓冲,让信号在FIFO中稳定后再输出。

特别注意的是,上述方法只能降低亚稳态发生的概率,如果亚稳态还是发生了,那么上述方法并不能阻止亚稳态传输给后级电路。