https://blog.csdn.net/u010580016/article/details/80430138?utm_source=blogxgwz1

开发环境:window10, vivado 2017.1, ubuntu 16.04, Eclipse+cdt

硬件环境:米尔科技zturn board,zynq7z010

本笔记详细介绍了开发ZYNQ7000系列的基础软件系统构建,介绍了Vivado的使用以及IP核的配置,最后搭建能让ZYNQ运行arm linux系统的软件环境,在今后的开发过程中将在此基础上进行。在完整搭建好本系统之后建议保存为模板工程。

首先简单介绍一下ZYNQ开发linux的基本流程:ZYNQ的开发也是先硬件后软件的方法。具体流程如下:

在Vivado中新建工程,增加一个嵌入式的源文件。

在Vivado里添加和配置PS和PL部分基本的外设,或需要添加自定义的外设。

在Vivado里生成顶层HDL文件,并添加约束文件。再编译生成比特流文件system.bit。

导出到SDK软件开发环境,在SDK环境里可以编写一些调试软件验证硬件和软件,结合比特流文件单独调试ZYNQ系统

在SDK里生成FSBL文件。

在VMware虚拟机里生成u-boot.elf bootloader镜像。

在SDK里通过FSBL文件, 比特流文件system.bit和u-boot.elf文件生成一个boot.bin文件。

在VMware里生成Linux的内核镜像文件zImage和Linux的文件系统ramdisk。另外还需要对FPGA自定义的IP编写驱动。

把boot.bin,zimage和ramdisk三个文件放入到SD卡的FAT分区中,启动开发板电源,Linux操作系统会从SD卡里启动。

一. 准备Linux系统的内核、uboot、文件系统、设备树等文件

1.1 编译uboot

在工作空间建立uboot目录,进入uboot目录,解压uboot源码

<workdir>$ cd uboot

uboot$ tar -jxvf u-boot-xlnx.tar.bz2

uboot$ cd u-boot-xlnx

编译uboot:

u-boot-xlnx$ make ARCH=arm CROSS_COMPILE=arm-xilinx-linux-gnueabi- distclean

u-boot-xlnx$ make ARCH=arm CROSS_COMPILE=arm-xilinx-linux-gnueabi- zynq_zturn_config

u-boot-xlnx$ make ARCH=arm CROSS_COMPILE=arm-xilinx-linux-gnueabi-

编译完成后,在当前目录下会生成"u-boot"ELF文件,将其重命名为"u-boot.elf"。

1.2 编译linux内核

在工作空间建立kernel目录,进入kernel目录,解压内核源码:

<workdir>$ cd kernel

kernel$ tar -xvjf linux-xlnx.tar.bz2

kernel$ cd linux-xlnx

开始编译:

linux-xlnx$ make ARCH=arm CROSS_COMPILE=arm-xilinx-linux-gnueabi- distclean

linux-xlnx$ make ARCH=arm CROSS_COMPILE=arm-xilinx-linux-gnueabi- zynq_zturn_defconfig

linux-xlnx$ make ARCH=arm CROSS_COMPILE=arm-xilinx-linux-gnueabi- uImage

linux-xlnx$ make ARCH=arm CROSS_COMPILE=arm-xilinx-linux-gnueabi- dtbs

编译完成后,在arch/arm/boot目录下生成uImage文件,在/arch/arm/boot.dts/生成zynq_zturn.dtb文件。

1.3 制作randisk

在工作空间建立filesystem目录,进入filesystem目录,将uramdisk.image.gz拷贝至该目录。

<workdir>$ cd filesystem

filesystem$ mkdir -p rootfs

去掉mkimage生成的64bytes文件头,生成新的ramdisk.image.gz

filesystem$ dd if=uramdisk.image.gz of=ramdisk.image.gz bs=64 skip=1

gunzip解压ramdisk.image.gz生成ramdisk.image

filesystem$ gunzip ramdisk.image.gz

将ramdisk.image挂在在rootfs目录

filesystem$ sudo mount -o loop,rw ramdisk.image rootfs

进入rootfs目录,根据需要做修改。

经笔者实验发现,米尔科技的开发板Zturn board在直接使用光盘文件时,以太网不能正常运行,经调试发现其ramdisk文件系统中关于网络的配置文件不完整,在ramdisk文件目录中,打开/etc/network/interfaces文件,发现其中没有关于eth0的配置,因此添加网络配置如下:

auto eth0

iface eth0 inet dhcp

重新生成ramdisk, 同步文件系统并卸载ramdisk

filesystem$ sync

filesystem$ umount rootfs

用gzip压缩ramdisk.image,生成ramdisk.image.gz

filesystem$ gzip -9 ramdisk.image

用mkimage添加头文件,生成新的uramdisk.image.gz供u-boot使用。

filesystem$ mkimage -A arm -T ramdisk -C gzip -n Ramdisk -d ramdisk.image.gz uramdisk.image.gz

至此,我们已经得到了u-boot.elf, uImage, devicetree.dtb, uramdisk.image.gz文件。

二. 在Vivado中建立硬件系统

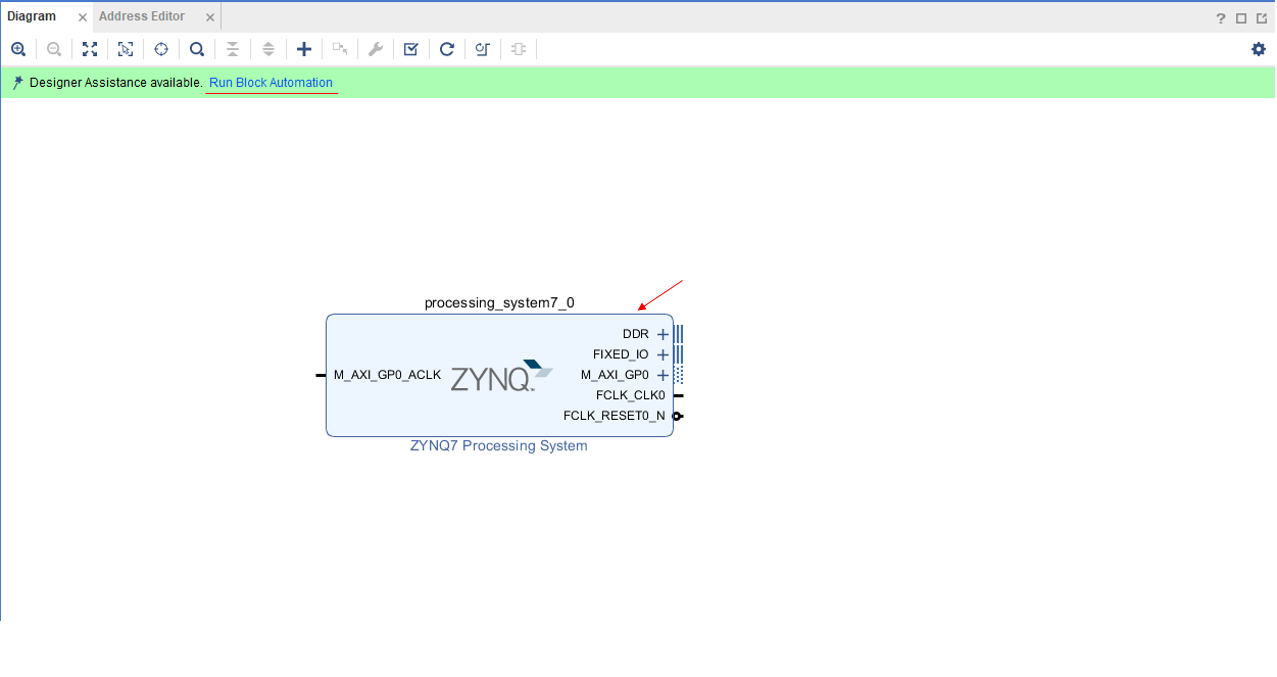

2.1 新建一个空白vivado工程,选择ZYNQ7010对应的芯片型号,点击左侧的Create Block Design,添加一个ZYNQ7的IP核。

点击Run Block Automation, 弹出的对话框直接点OK,双击ZYNQ IP核,配置参数。

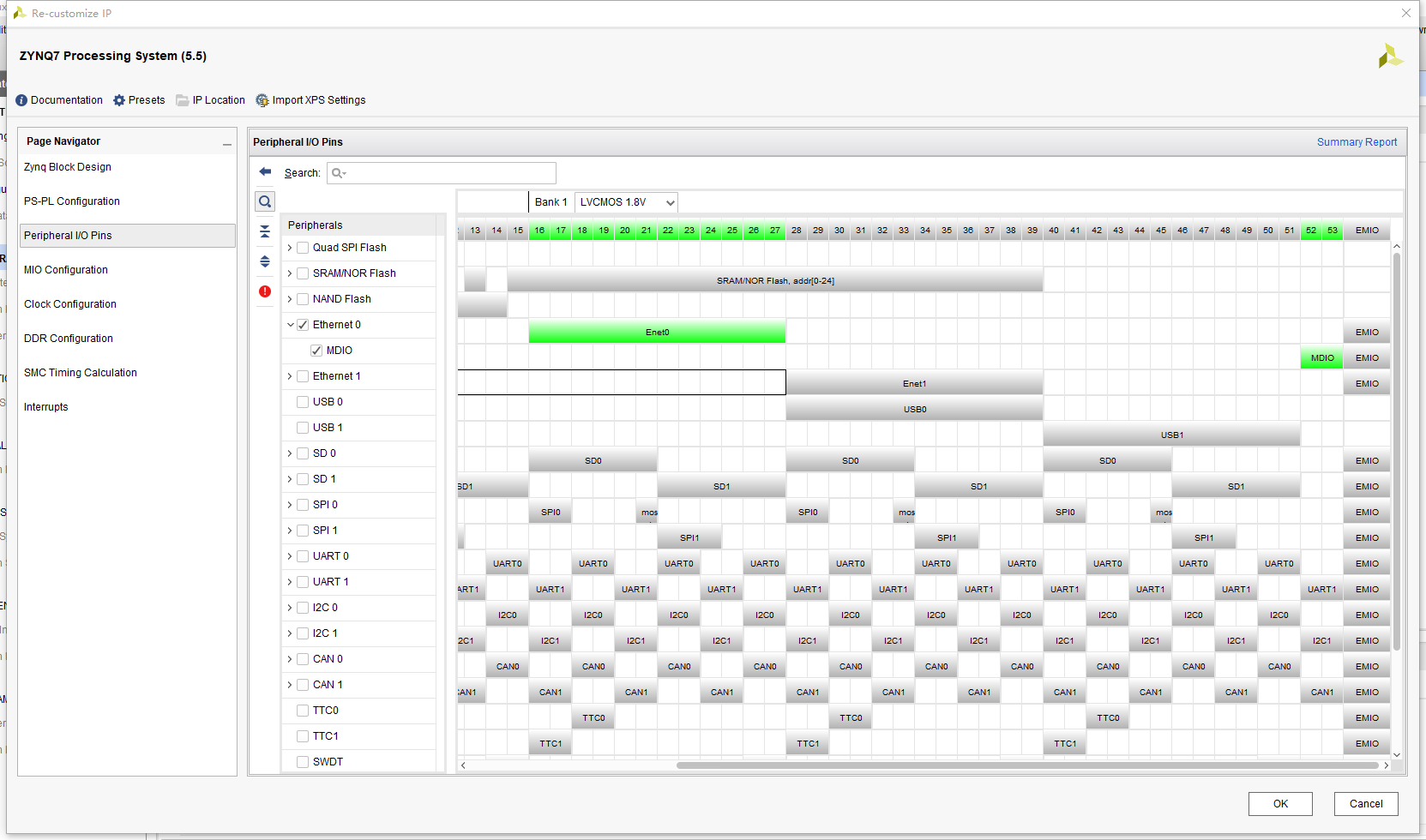

2.2 Peripheral I/O Pins配置

Bank 1选择LVCMOS 1.8V

勾选Quad SPI Flash

勾选Ethernet 0 以及展开目录下的MDIO,点击右侧Enet0, 配置其使用PS的MIO16~27, MDIO选择PS的MIO52,53,注意这两个选项不手动选择对应的引脚则使用EMIO。

勾选USB0,使用PS的MIO28~39。

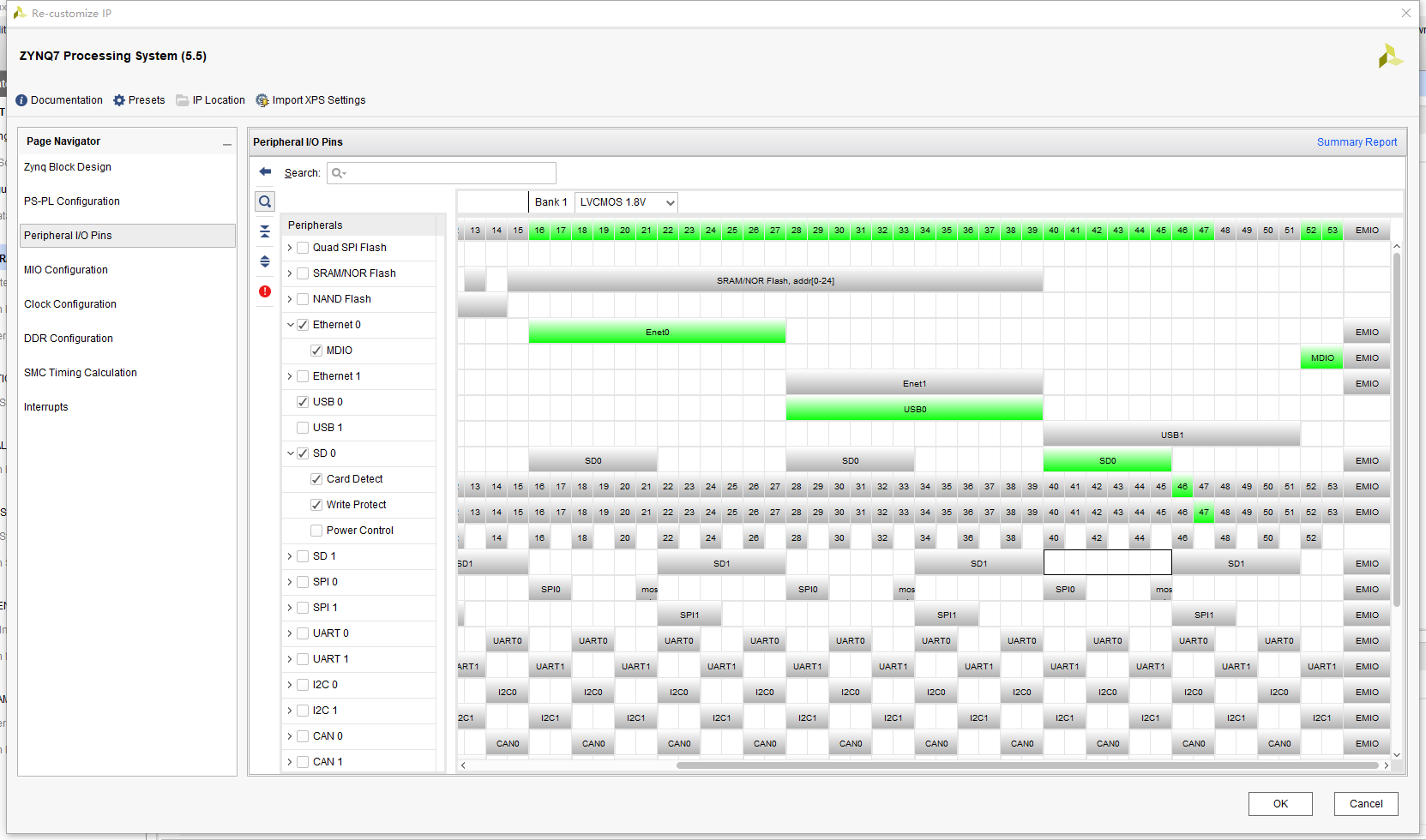

勾选SD0,使用PS的MIO40~45,展开SD0目录,使用选择Card Detect为MIO46, write Protect为MIO47.

勾选UART1, 使用PS的MIO48, 49.

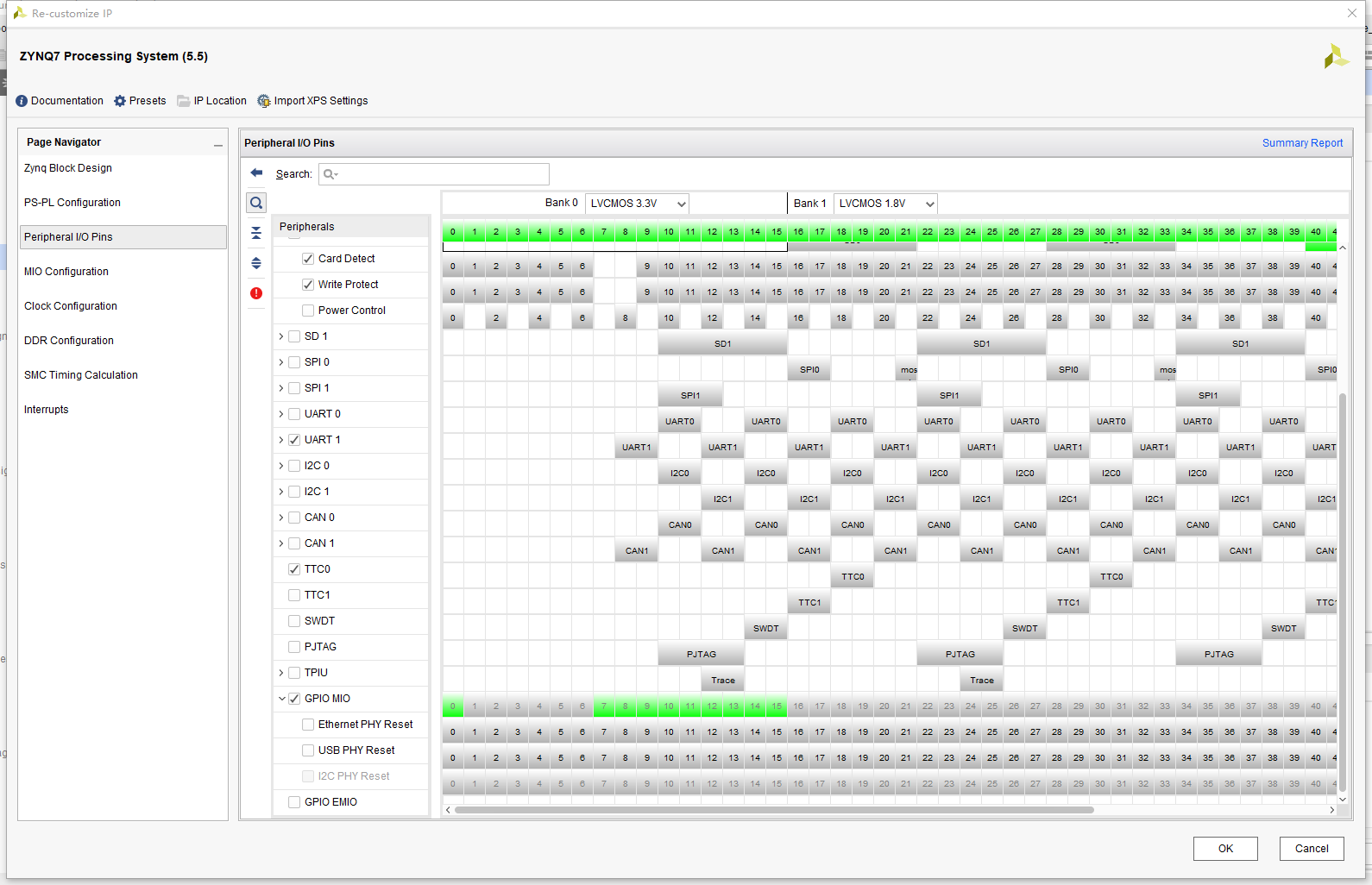

勾选TTC0, 使用EMIO。

勾选GPIO MIO,不用选择展开的选项。

最后所有的配置如下图所示

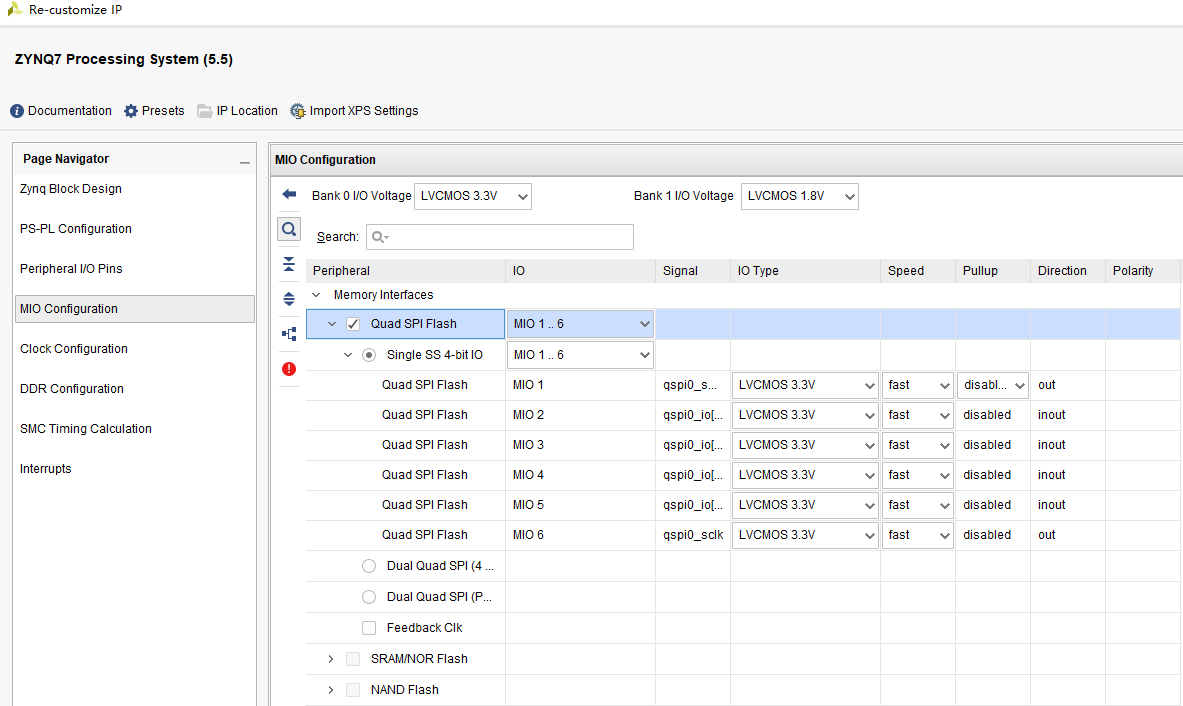

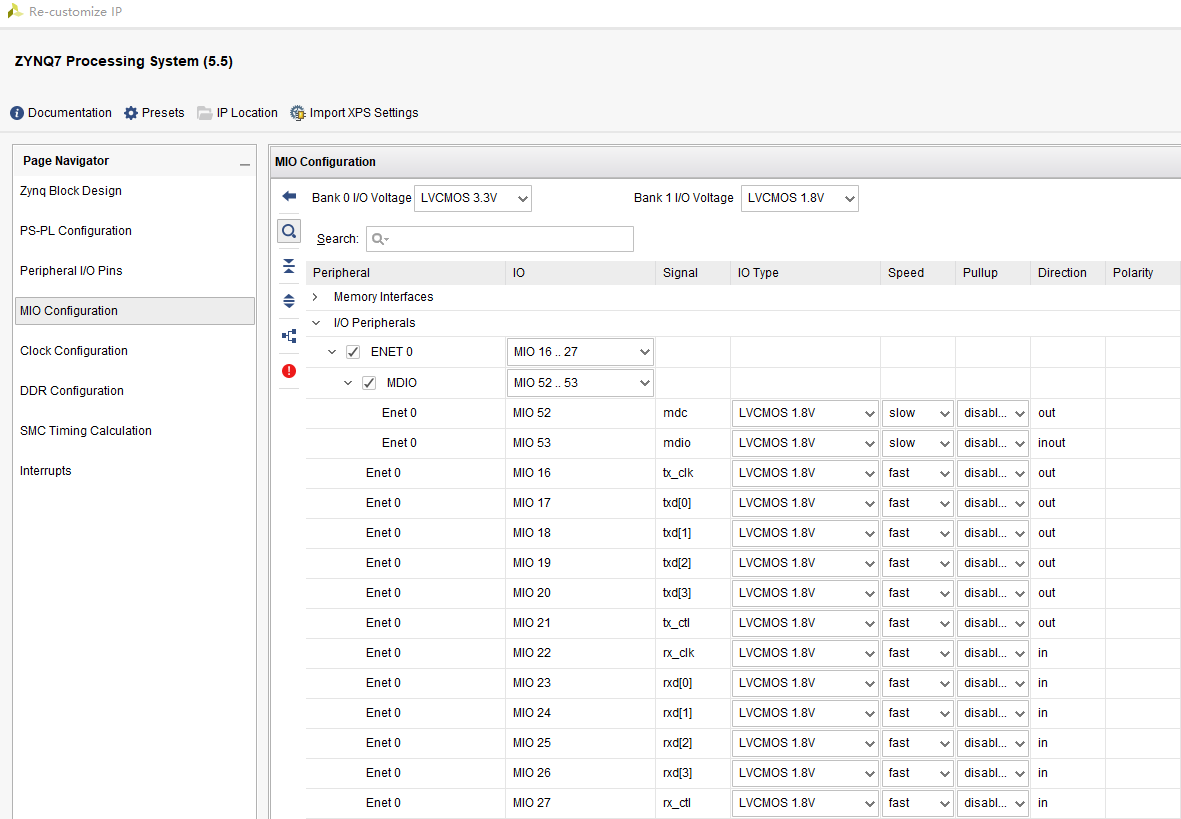

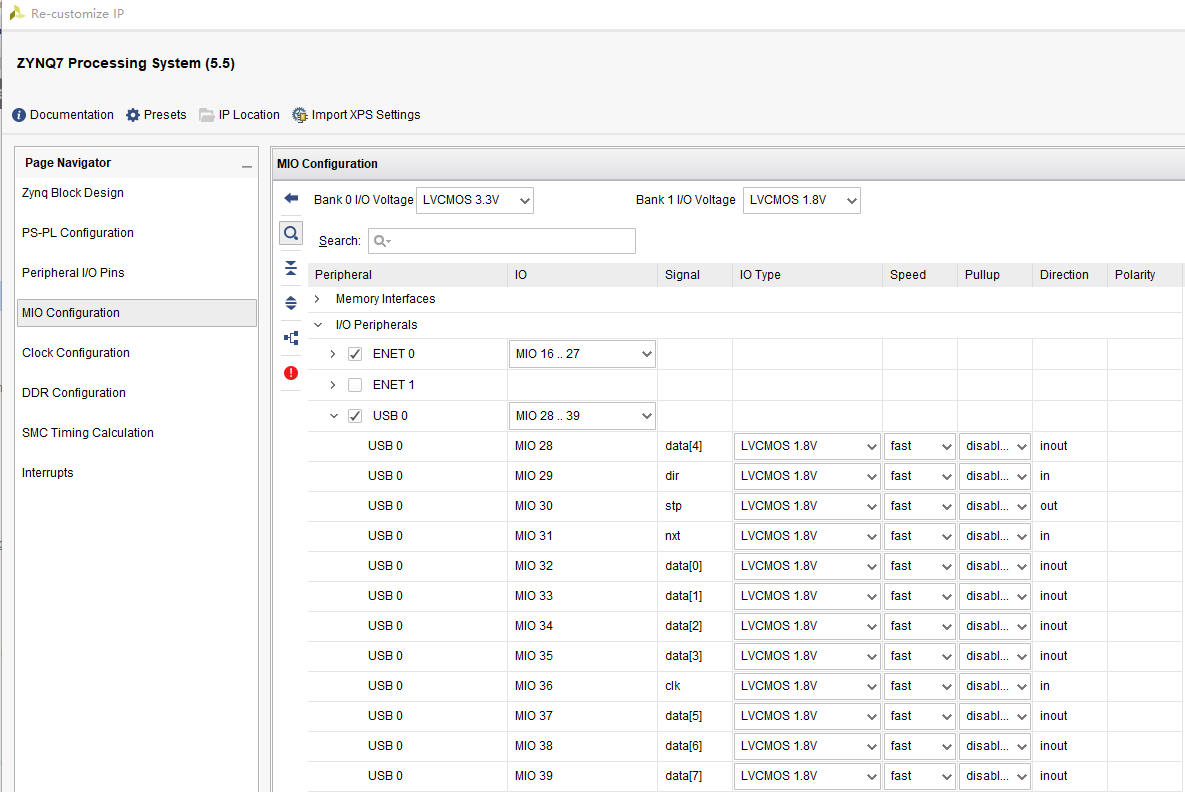

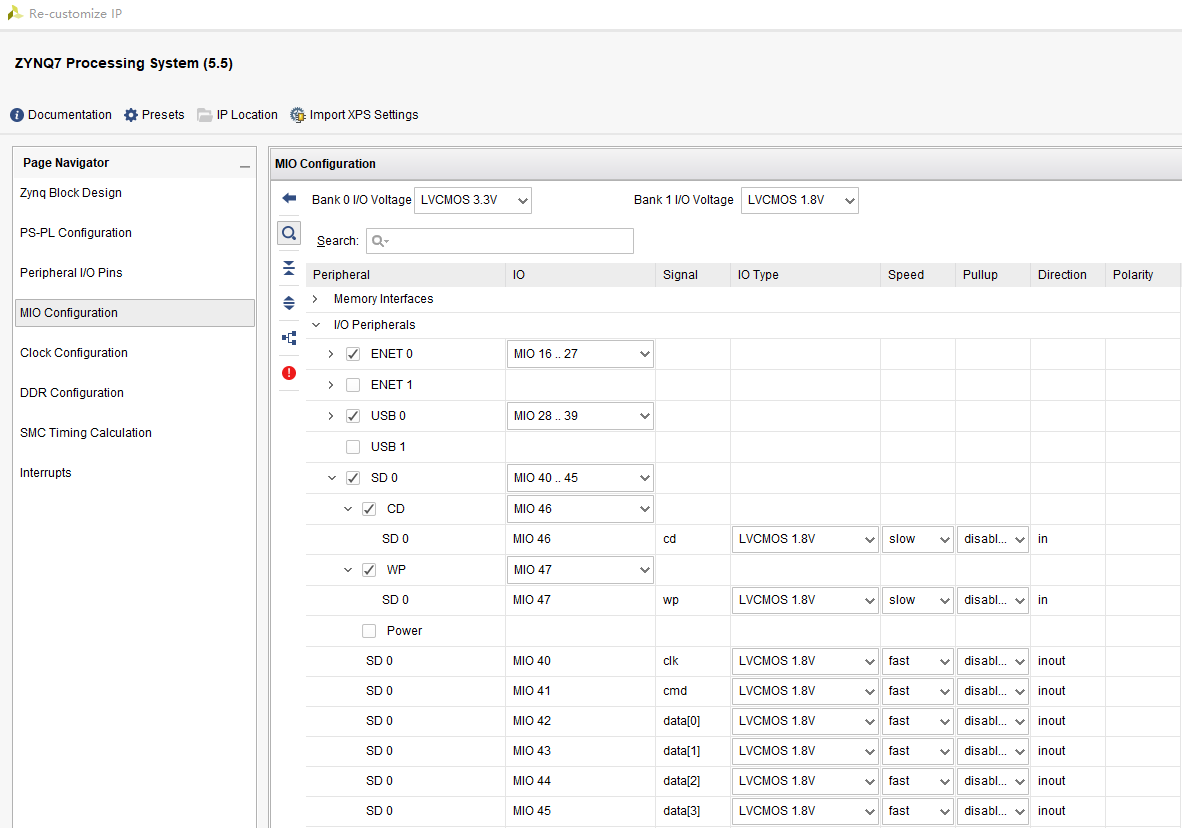

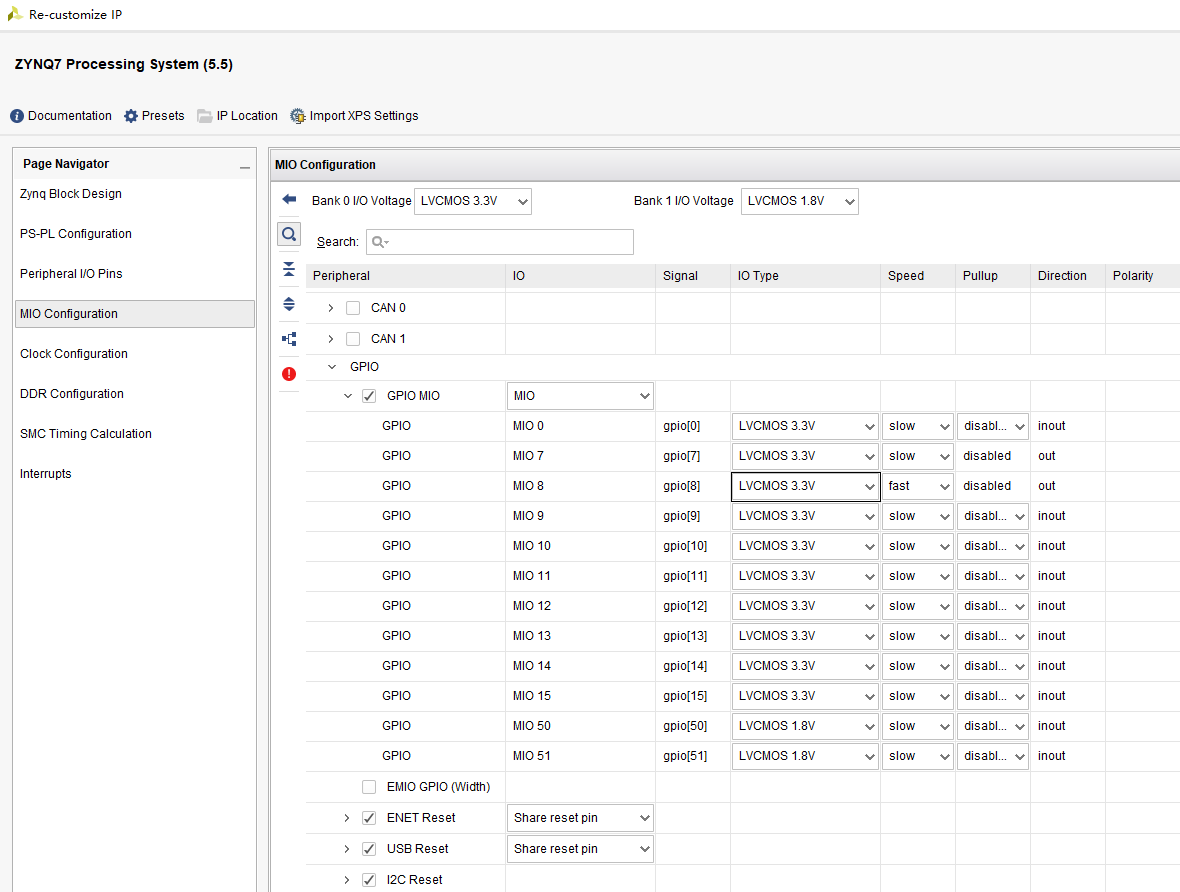

2.3 MIO Configurateion:

展开Memory Interfaces->Quad SPI Flash->Single SS 4-bit IO, 设置所有的引脚速度为"fast", MIO1选择disable;

展开I/O Peripherals所有项目,设置所有的引脚速度mdc和mdio为slow,其他为fast,所有引脚上拉设置为disable:

展开USB0选项,设置所有引脚速度为fast,上拉选disable:

展开SD0选项,设置如下:

展开GPIO,设置如下:

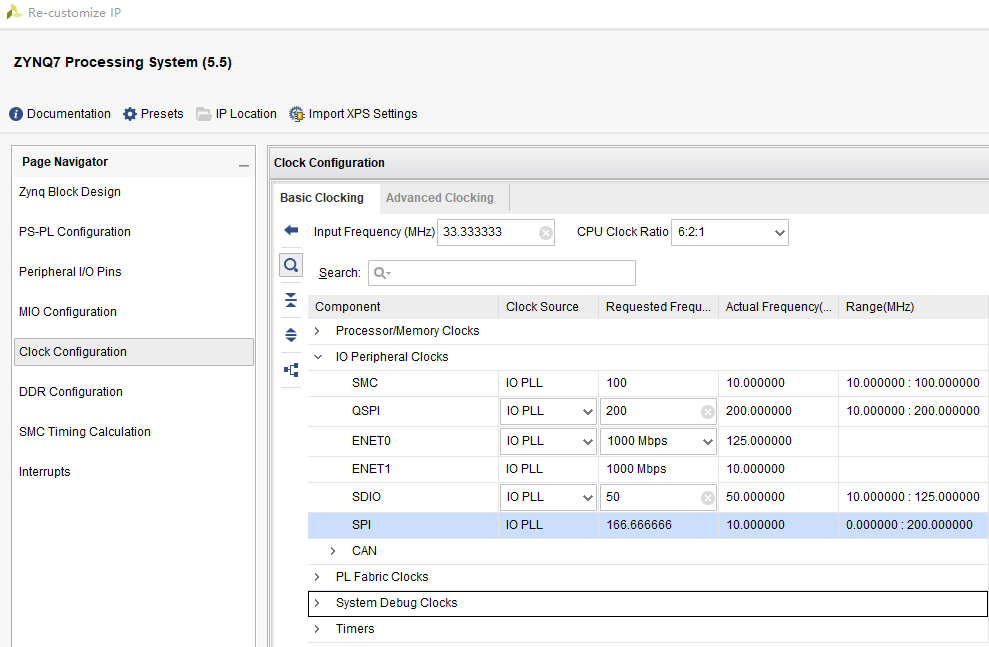

2.4 Clock Configuration,配置时钟频率如下图所示:

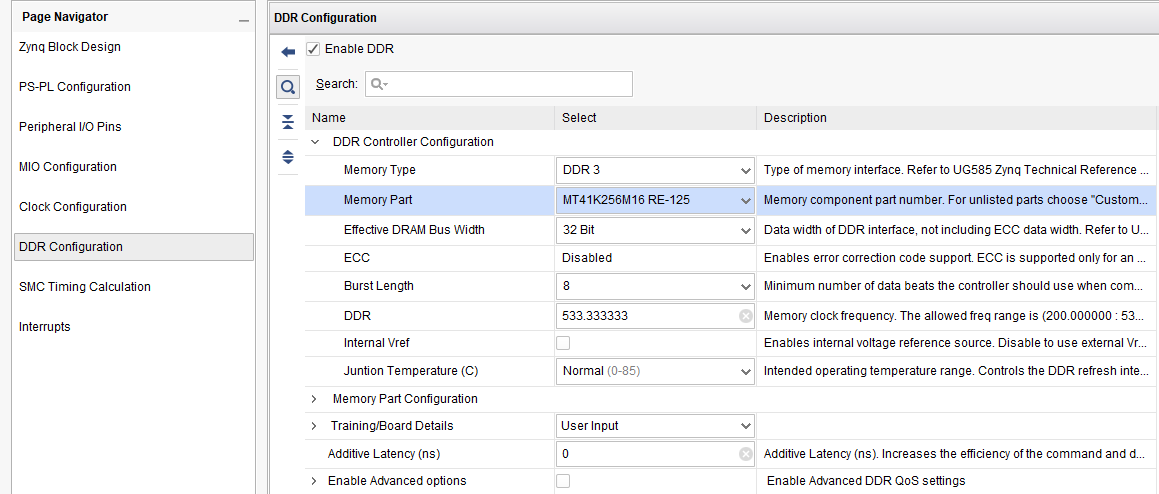

2.5 DDR Configuration

根据原理图,选择memory part为MT41K256M16 RE-125

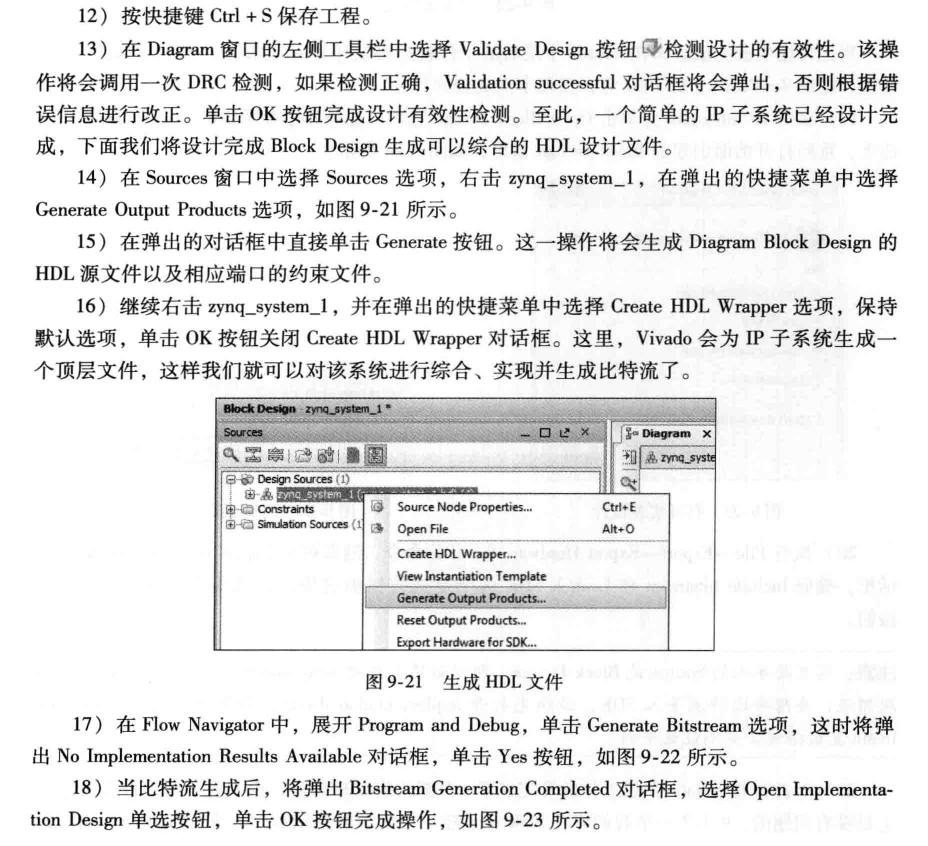

2.6 编译硬件系统

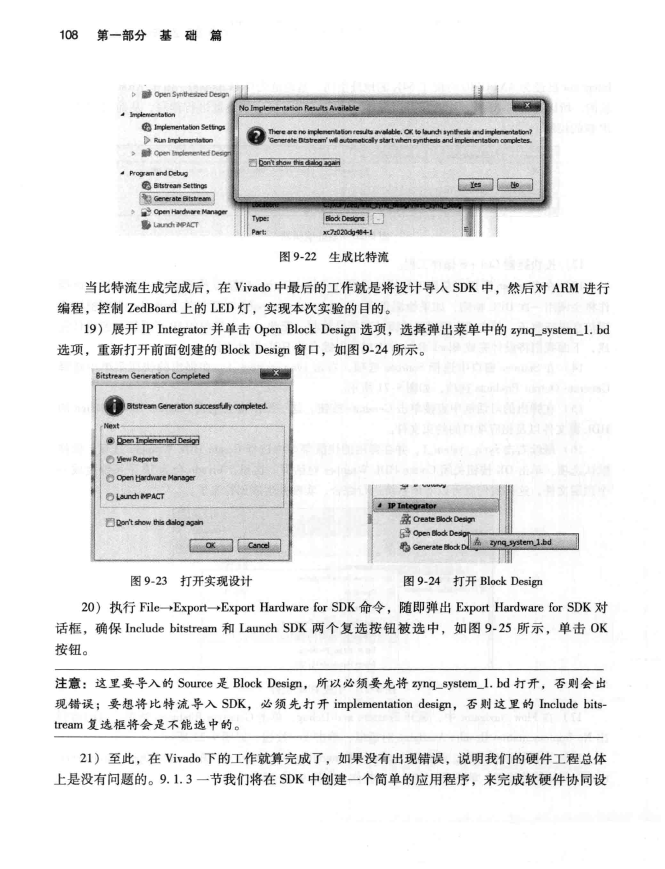

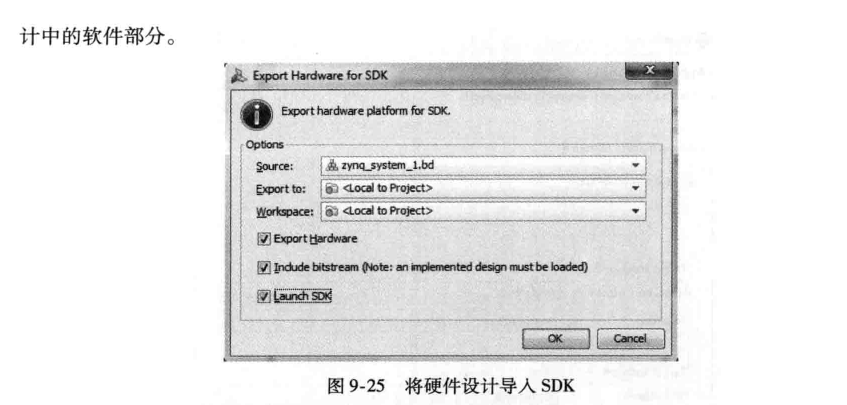

右键选择原理图文件(Source选项中), 选择generate output products...,接着Run Synthesis, 综合完成后点击Run Implementation,编译完成后点击Generate Bitstream,导出硬件设计File->Export->eexport hardware, 然后启动SDK设计软件:File->Launch SDK.

参考

在本次项目中并没有添加FPGA部分的设计代码,所有在整个流程没有关于FPGA的引脚约束,仿真等操作,这一部分将在后续介绍。

三. 在SDK中验证硬件设计并制作SD卡启动文件

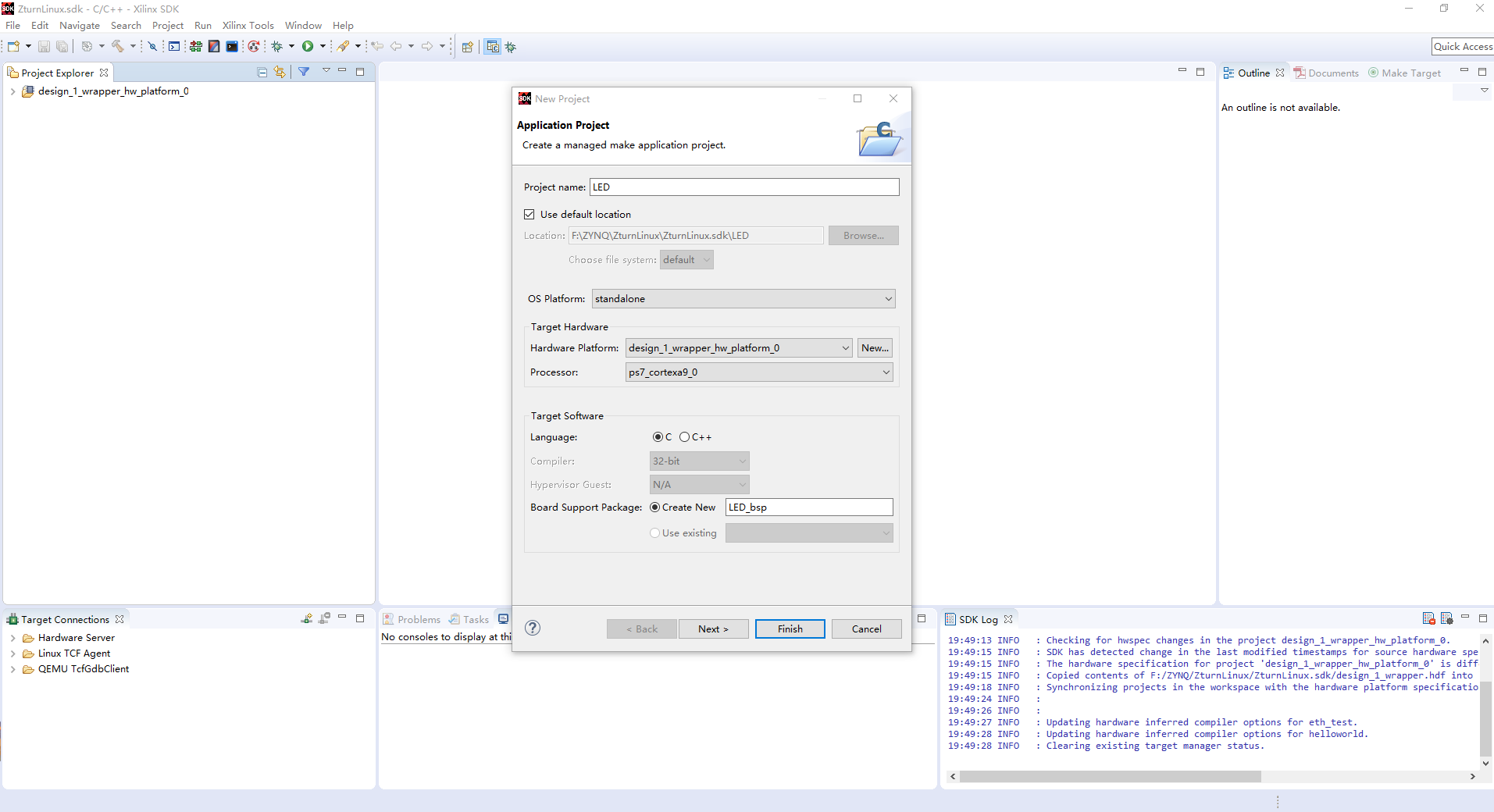

3.1 在SDK中新建应用程序,以Hello world为模板。

在Launch SDK之后,SDK软件一般会自动创建一个硬件平台(<project_hw_platform_0>),如果是在多次导出硬件设计过程中生成了多个platform_x文件,建议删除所有platform文件,重新导出。

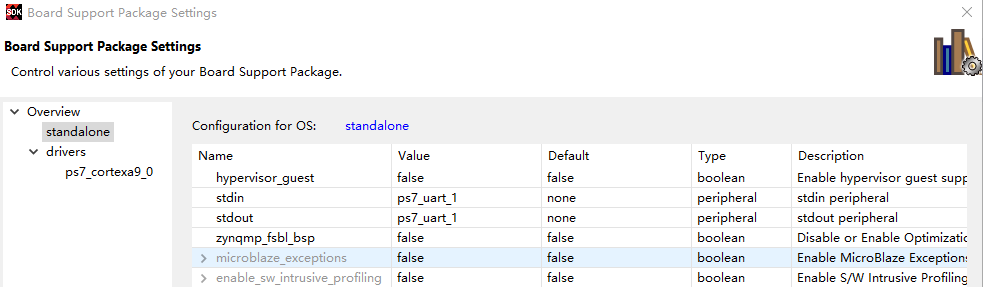

在生成的bsp工程上右键点击,Board Support Package Settings->Overview->standalone, 设置stdin和stdout为ps7_uart_1,因为在硬件设计中我们选择的是使用串口1作为终端串口输出,SDK在默认时时使用uart0, 因此如果在SDK中使用printf或xil_printf没有看到输出,则需要检查此处的设置。

3.2 连接仿真器,串口终端,电源,首先烧写FPGA程序(.bit文件), 然后运行helloworld工程,在终端上可以看到打印了一行hello world字符,说明基本硬件没有什么大问题。

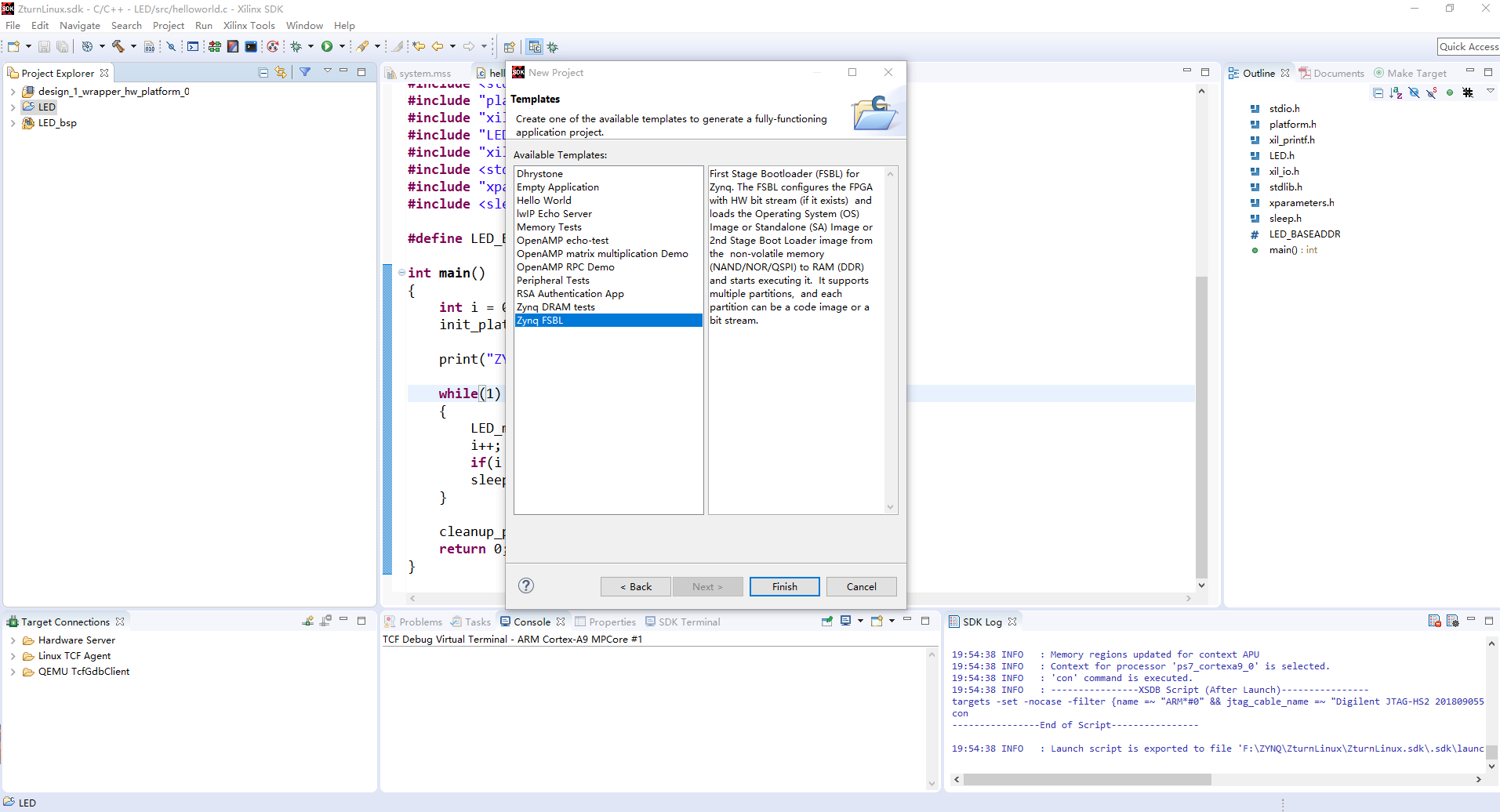

3.3 创建FSBL

FSBL是first stage boot loader的简称,它是ZYNQ启动第一阶段加载的程序,固化在芯片内的BOOT ROM首先加载FSBL程序,FSBL加载u-boot, uboot加载Linux。因此要运行Linux系统必须要制作FSBL。

新建应用程序,选择以Zynq FSBL为模板工程。

不用修改fsbl工程,直接编译生成的这个工程。

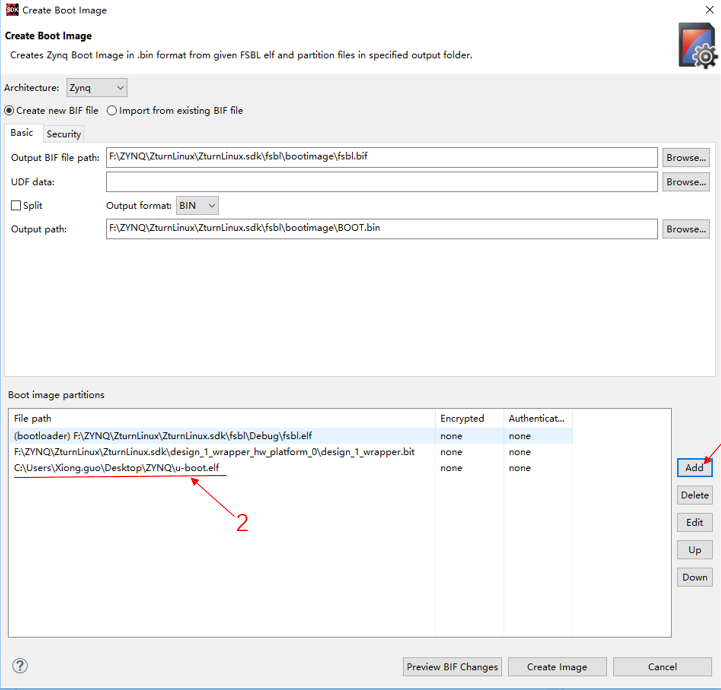

右键选择fsbl工程,选择Create Boot Image, 在Boot image partitions中已经添加了fsbl.elf, design_1_wrapper.bit,点击Add选择前面准备好的u-boot.elf文件,将三个文件一起生成BOOT.bin文件。

3.3 启动Linux系统

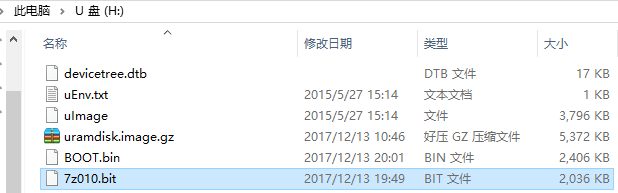

SD卡需要时FAT32格式,如果不是请格式化,将以上所有生成的文件放在SD卡的根目录下,如下图所示:

其中7z010.bit文件是有desig_1_wrapper.bit改名而来,如果不改需要在fsbl工程中去修改加载的.bit文件的名称,所以建议所有的工程生成后都重命名为7z010.bit,将SD卡插入开发板,上电启动。

事实上在本次设计中我们并没有设计关于FPGA部分的源文件,为什么还是要7z010.bit文件呢?在u-boot启动过程中如果没有检测到FPGA的配置文件u-boot将不启动Linux内核,所有无论有没有FPGA的设计都需要一个FPGA的配置文件,即使是空的配置。