本笔记不记录DMA的Scatter/Gather特性。DMA上有三种总线:AXI4-LIte(对寄存器进行配置),AXI4-Memory Map(用于与内存交互)和AXI4 Stream(用于与外设交互)。在寄存器模式下,寄存器分为两部分:MM2S和S2MM,每个部分包括Control Register, Status Register, Source Address, 和Transfer Length四个寄存器部分。

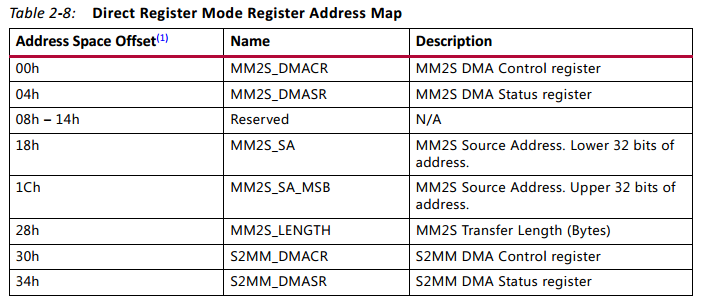

表:DMA在Direct Register模式下的Register Address Map

其中Soure Addresss和Destation Address指的是内存地址。

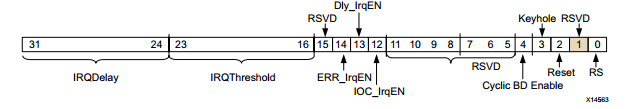

下图是控制寄存器MM2S_DMACR,bit0用来控制DMA的开启和关闭。

图:MM2S_DMACR

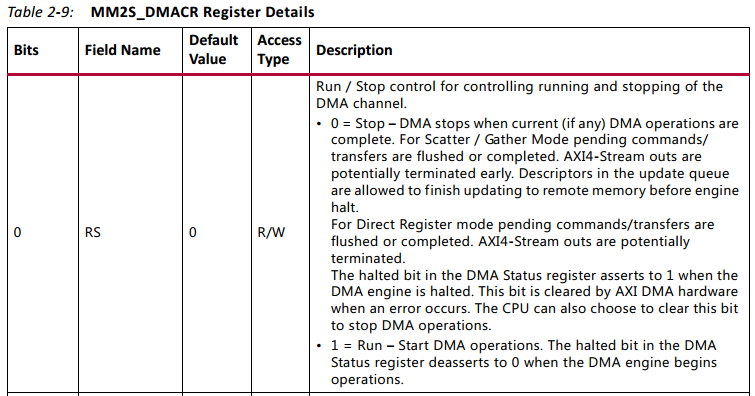

图:控制寄存器的bit0详细介绍

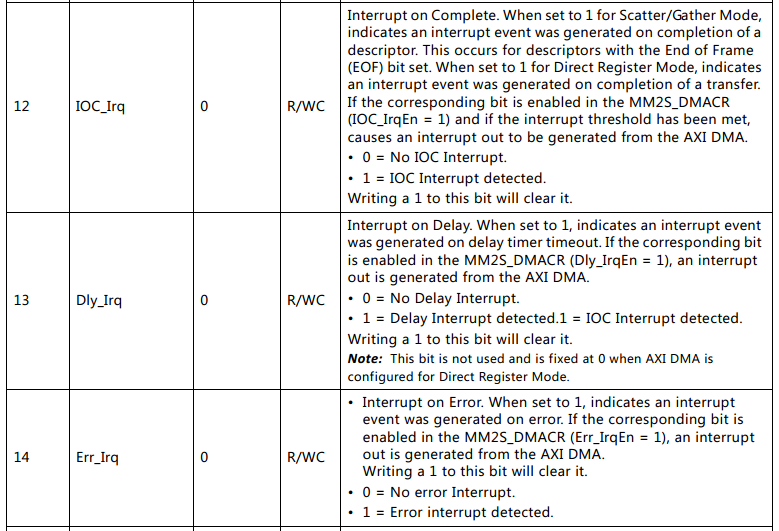

该控制寄存器的第12,13和14bit是有关中断设置的,分别是完成中断,延迟中断和错误中断。

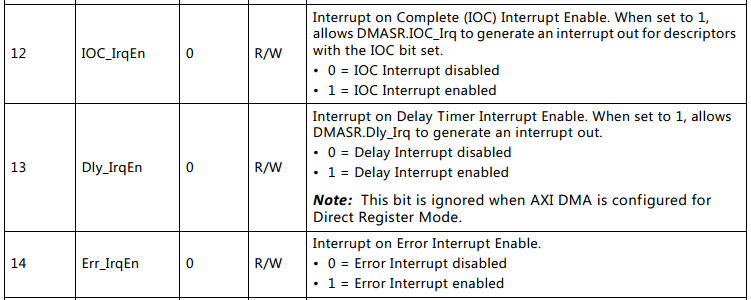

表:控制寄存器有关中断的bit位

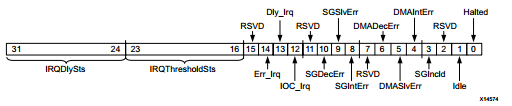

下一个比较重要的寄存为状态寄存器MM2S_DMASR,如下图所示。

图:DMA的状态寄存器(SR)

其中第12,13和14bit位表示中断的状态,写1可以清除中断。从表格可以看出,这三个寄存器分别与控制寄存器中的三个中断一一对应的。

表:DMA状态寄存器中用来表示中断状态的bit位

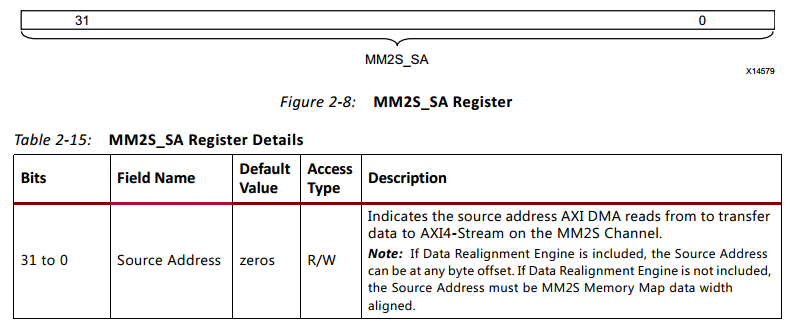

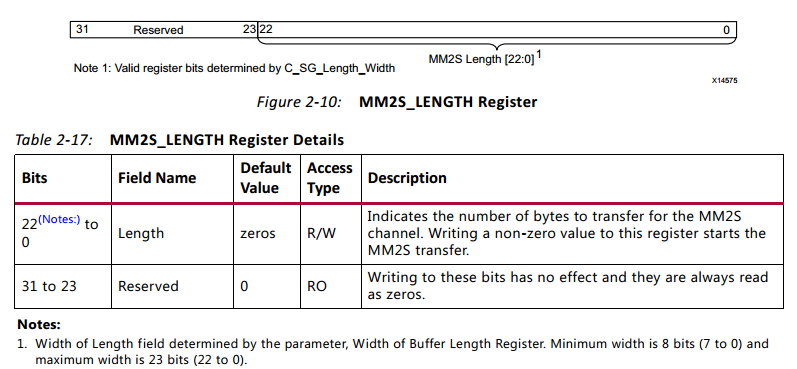

另外两个寄存器MM2S_SA和MM2S_LENGTH分别表示地址和长度,如下图所示。

在DMA的IP设置时,会设置Width of Buffer Length Register(8-23),默认的是14。这里设置的就是上面的MM2S_LENGTH Register,如果设置为23,那么最大传输就是2^23=8388608byte。