一、80286概述

INTEL 1982年推出80286芯片,该芯片相比8086和8088有了飞跃式发展,虽然它仍是16位结构,但在CPU内部含有13.4万个晶体管,时钟频率由最初6MHz逐步提高到20MHz。内部和外部数据总线皆为16位,地址总线24位,可寻址内存大小达到16Mb。80286兼容了8086所有功能,并且是8086的向上兼容的微处理器,使8086的汇编语言程序可以不做任何修改地在80286上运行。同时80286的推出也是实模式和保护模式CPU的分水岭。80286微处理器内部有4个功能部件,即地址部件AU,指令部件IU,执行部件EU和总线部件BU。这四个部件的并行操作,提高了吞吐率,加快了处理速度。

二、80286引脚及功能

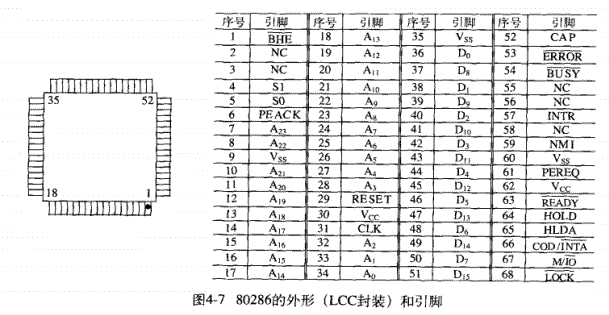

80286具有68条外部引脚,可封装程PGA或LCC两种形式,它的多数引脚与8086相同,对此不在重复,下面介绍那些功能不同的引脚

A0~A23-----24位地址

D0~D15-----16位数据线

S1、S0 --系统状态输出;COD/INTA 代码或中断响应,输出;M/IO 选择存储器或I/O端口

PEREQ 协处理器操作请求 PEACK 协处理器操作响应 BUSY 协处理器忙 ERROR 协处理器出错

CAP 滤波电容输入

VSS 系统的参考地

NC 内部没有连接

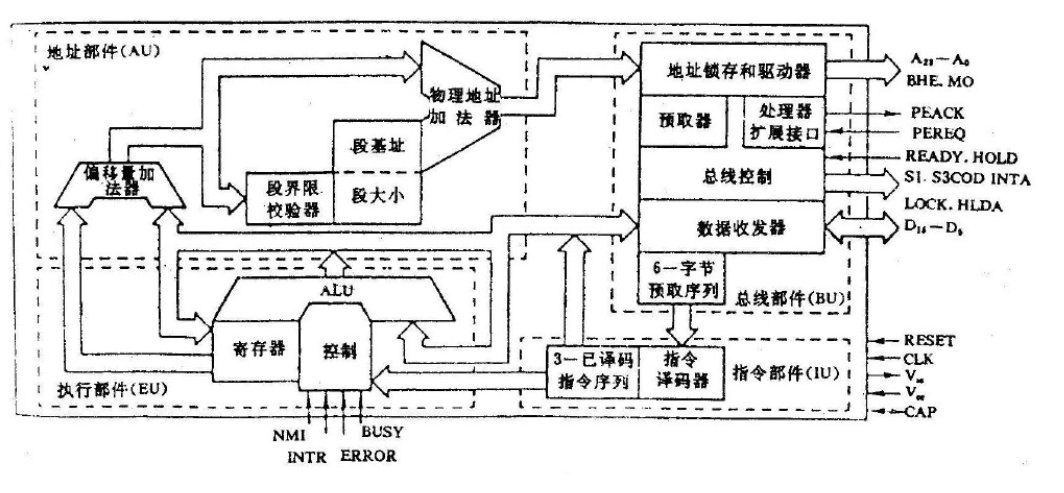

三、80286结构

8086内部由执行单元和总线接口单元两大部分组成。而80286恰好与此不同,它由总线单元、指令单元、执行单元及地址单元四大部分组成,这些打印可以同步地并行工作,实现流水线作业,避免传统的顺序处理方式,最大限度的发挥处理器性能。

地址单元

Adress Unit, AU 由地址偏移量加法器,段基址寄存器,段容量寄存器,段限检查器和物理地址加法器等组成。同是还增加了对方式操作时的存储器管理和保护机构。地址部件的职责是根据执行部件EU的请求,从EU的寄存器中取出寻址信息,根据寻址规则形成物理址,然后把物理地址送到总线部件BU的地址锁存器和驱动器中,所长生的地址是物理存储器地址或I/O设备的端口。在地址单元中,由偏移量加法器进行有效偏移地址计算时,要对其偏移量的段界限进行检查,并且还要对段存取检查,最后才进行从虚拟地址到物理地址的转换。

总线单元

总线单元(Bus Unit, BU)由地址存储器和驱动器、总线控制、数据收发器、预取器和指令预取队列以及协处理器借口等组成,他是由CPU与系统之间的一个高速接口,其任务是使CPU以最高速率从外部取代码和读/写数据。总线单元生成存储器及IO请求所必须的地址、数据、指令信号,并执行CPU的所有总线操作。

指令单元

指令单元(Instruction Unit, IU)由指令译码器和已被译码的指令队列组成,其功能是不断的从总线部件BU的预取代码队列中取出指令,译码后放倒已被译码的指令队列中,为执行部件EU执行指令做好准备。IU的引入进一步改善了流水操作,IU内部始终存放着3条已译码的指令,执行部件EU执行的就是这些已经译码指令。IU和EU的并行操作,缩短了执行指令的时间。

执行单元

执行单元(Execution Unit, EU)由算术逻辑部件ALU,控制器和微代码只读存储器构成,EU负责执行指令,所执行的指令时从IU中所取来的已译码的指令。

四、80286的工作模式

4.1. 实地址模式

系统开机CPU复位时,自动进入实地址模式,A23~A20自动置为0,以 A19~A0寻址1M的存储空间。也就是8086工作模式

4.2. 虚地址保护模式

当机器状态字MSW的PE位置1时,进入保护模式。该模式主要针对在多任务机制中的存储管理。 其有两个方面的含义:

虚地址 —— 应用程序可以寻址一个比实际物理地址空间(16M)大得多的虚存空间(1024M)。

保护 —— 对存储空间的(数据和程序的)保护,保障多任务机制。

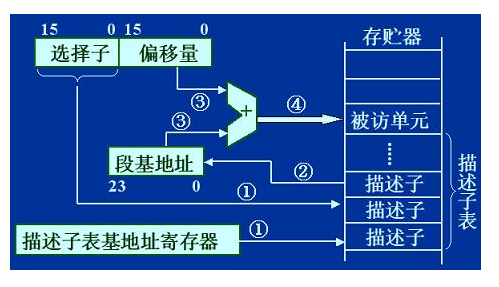

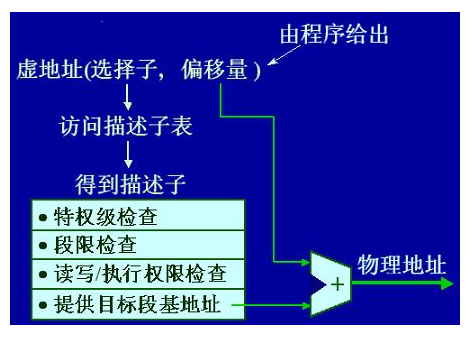

保护模式下的寻址过程:为实现“虚地址”和“保护”两大功能,系统必须提供一种“机制”或“平台”或一个“中间环节”来实施并完成上述两大功能。而这个所谓“中间平台”的核心部分,就是传说中的描述子 (Descriptor)。

描述子的作用:刻划存储段的属性(比如一个段的保护属性)并提供虚地址到实地址转化的信息。描述子的引入,使存储器的构成就由单一的存储段,转变成了若干存储段和若干存储段的描述子构成,因此存储器的组织形式就由实地址模式的单一的“存储段”变为两级结构,即:(1)一系列可变长的段(1 ~ 64K)、(2) 一系列的描述子。下图即为虚地址保护模式下寻址的顺序(从 ① 到 ④ )。

所有的描述子都有特定的功能,所有Intel对其划分成了若干类:

按描述子的作用范围:局部描述子和全局描述子。

◆ 局部描述子:刻划某一个任务所要访问代码段或数据段的描述子, 作用于该任务所要访问的范围。这些描述子的的组合构成一个描述子表, 称为局部描述子表LDT。每个任务都有一个LDT。

◆ 全局描述子:作用范围涉及系统中所有的代码段和数据段。所有这些描述子的组合构成一个全局描述子表GDT。整个系统只有一个GDT。

从描述子的功能来划分:

◆ 数据/代码段描述子:用于刻划一个存放数据或代码的存储段的各种属性。比如该段的特权级、段限、读写属性、并提供从虚地址到实地址转换的信息。

◆ 门描述子:实现不同任务间的转换和同一任务的不同代码段之间的转移。

◆ 任务状态段描述子:系统中每一个任务都有一个任务状态段(类似于操作系统中,进程相应的PCB),由于任务状态段也是一个段,因此也有一个对应的描述子,称为任务状态段描述子。(门描述子和任务状态段描述子统称为系统描述子)

4.3. 描述子和选择子

4.3.1、 数据/代码段描述子

描述子是一个位于内存的数据结构, 用于描述所对应的(或所描述的)那个存储段的访问属性。 这些属性包括:一个存储段可以被哪一特权级的任务访问、该段的大小、该段的读写/可执行权限、该段的基地址。如下:

BASE23~16 BASE15~0 : 描述子所描述的那个段的段基地址。

Limit (段限): 该段的最后一个字节的偏移量,指明了该段的大小。

A: 该段是否被访问,该段已被访问过,则 A←1;该段未被访问过,则 A←0。该位与操作系统的时钟相结合,可进行段淘汰算法。

S: 描述子类型,1 代表数据代码段描述子;0 代表系统描述子(如门描述子/任务状态段描述子)

DPL: 共两位,规定可以访问该描述子所描述的那个段的任务的最低特权级。

P: 0 表示该描述子所描述的段不在物理空间;1 表示该描述子所描述的段在物理空间。

TYPE:由三位构成,即数据段(E, ED, W) 或代码段(E, C, R)。这个TYPE对所描述的存储段的具体属性有着极其重要的意义。若该段为数据段,则 E=0,需要配合TYPE的ED和W。ED为0则段向上生长,所以要求偏移量小于Limit(段限);ED为1则段向下生长,所以要求偏移量大于Limit(段限);W为0则该数据段只能读,不能写;如果W为1则该数据段可读、可写。若该段为代码段,则E=1,需要配合TYPE的C和R(ED变成了C,W变成了R)。C为0则非一致性代码段访问和被访问代码段特权级相同;C为1则一致性代码段访问和被访问代码段特权级可以不同;R为0则代码段只能执行,不能读;R为1代码段可以执行,也可以读。

综上,根据描述子中的内容和定义, 将保护模式下的寻址过程描述为:

前面所叙述的局部描述子表LDT,全局描述子表GDT和中断描述子表IDT,每个表都作为一个特殊的段存放在主存中。CPU提供三个寄存器存放描述子表的基地址,称为描述子表基地址寄存器(24位),分别为:LDTR、GDTR、IDTR 寄存器。

4.3.2、选择子功能(程序给出)

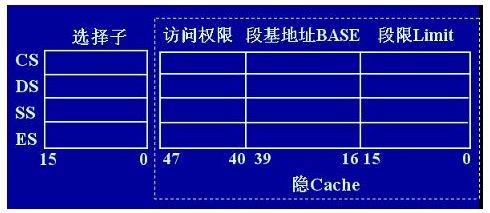

80286进入保护模式以后,那几个段寄存器存放的再不是段基址了,而是一种用来定位段描述子的东西,叫做选择子。选择子主要扮演以下三个角色:

◆ 指明使用该选择子的任务的特权级

◆ 指明所要访问的描述子在描述子表中的偏移量(索引)

◆ 指明访问全局描述子表还是访问局部描述子

RPL: 请求特权级,用以表示使用该选择子的任务的特权级。当前运行任务的特权级称为当前特权级CPL。一般有: RPL= CPL

TI: 区分访问全局描述子还是局部描述子:TI为0——访问全局描述子;TI为1——访问局部描述子。

偏移量D15~D3:所要访问的描述子在描述子表中的偏移量。

4.3.3、 虚存空间的计算

◆ 总共可以访问的描述子的数量为2^13=8K (个描述子)

◆ TI位区分了全局描述子或局部描述子,因此可以访问的描述子的总数为:2×8K=16K

◆ 一个描述子对应一个存贮段,段的最大空间64K(2^16(limit)),因此可访问的最大存储空间(虚地址空间)为: 16K×64K=1000M=1G

由于在保护模式下访存时,首先需要访问选择子,再得到描述子。为了加快访问速度,避免二次访存,即每次访问存储器时都要通过访问描述子表而获得对应的段描述子,从80286开始,每个段寄存器都配备了一个高速缓冲寄存器,称之为段描述子高速缓冲寄存器(隐Cache)。当将一个选择子装入某个段寄存器时,处理器将自动从描述子表中取出相应的描述子,将描述子的信息保存到对应高速缓冲寄存器中。 以后对该段进行访问时,处理器都使用对应高速缓冲寄存器中的描述子信息,从而不再从描述子表中取描述子。

隐Cache位于CPU内部,其内容随着段寄存器的修改而被重新装入,这种装入操作对程序员透明。

假设一个32位的虚地址:005E0100H,其中选择子为005EH=0000000001011110,低位补3个0,为0058H, 作为访问LDT的偏移量;RPL=2(10);TI=1,访问局部描述子。 每个描述子为8个字节, 意味着选择子中的偏移量每增减一个单位, 应指向另一个描述子(偏移8个字节), 因此描述子在描述子表中偏移量的D2、D1、D0始终保持为0, 增减一个单位均在D3上进行,以保证偏移8字节。虚地址的偏移量为0100H。

我们假设 LDTR=100000H

第一步:将描述子表基地址LDTR+选择子偏移量 =100000H+0058H=100058H

第二步:由物理地址100058H访问并得到相应的描述子,检查对该描述子访问的合法性(比较CPL和DPL),假设DPL=3, 则CPL=RPL=2≤DPL(数值上),访问是合法的。

第三步:由描述子中的访问权字段(TYPE)检查本次访问的访问权限,假设通过检查,将虚地址中的偏移量(即0100H)与描述子中的段限Limit进行比较,以确定访问是否越界,假设描述子中给出的段基地址位046000H, Limit=2000H, 有偏移量0100≤段限2000H,未越界。

第四步:形成物理地址046000+0100=046100H(24位),以此访问存储单元的物理地址,得到所需要的数据。

4.3.4、 门描述子

前面介绍了描述子和选择子,80286还有一个重要的概念是门描述子,用于中断控制和保护,以及任务之间的切换。注意,门描述子也是描述子的一种,但它并不用于描述某个存储段的属性,而是控制同一个任务内不同代码段之间的转移,或用于控制任务之间的切换。门描述子有四种类型:调用门、中断门、自陷门、任务门。前三者是控制同一个任务内不同代码段之间的转移;后一个是控制任务之间的切换。

调用门 → 主程序调用子程序、转移指令

中断门 → 中断引起的代码段转移

自陷门 → 自陷引起的代码段转移。与中断门区别仅在于调用中断门时要将IF置0, 调用自陷门则不管IF标志。

门描述子的格式如下:

对比描述子,我们可以看到,字计数(5位)仅调用门使用;若是任务门,则目标代码段描述子的选择子表示TSS描述子的选择子;目标代码段的偏移量对任务门无效。P为 0 表示该描述子内容无效;P为 1 表示该描述子内容有效;TYPE为4表示调用门、为5表示任务门、为6表示中断、为7表示自陷门。对任务门:任务门与任务状态段描述子一起, 控制任务之间的切换。

通过中断门/自陷门实现代码段转移调用的过程:

通过调用门实现代码段调用的过程:

先暂时把任务门放一放,这里说明几点问题:

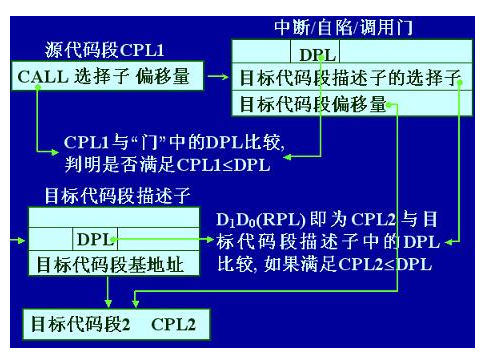

[1] 流程中的地址转换过程,只要访问描述子,都需要作的保护性检查,比如仅当CPL≤DPL时转换过程才能继续往下进行。

[2] 为什么需要两次访问描述子(第一次是访问门描述子,第二次是访问目标代码段描述子),就这个问题,我们来详细说一下。在保护模式下, 同一任务的不同代码段, 也有不同的特权级, 意味着主调代码段与被调代码段可能处于不同的特权级, 因此需要指明目标代码段特权级, 并由此实现这同一任务的特权级的改变。为实现特权级的改变, 通过 “门”这样一个描述子中提供目标代码段描述子的选择子, 该选择子的低2位(RPL)指明目标代码段的特权级。

[3] 中断/自陷/调用门的使用场合:

◆ 同级特权级之间转移:可以使用也可以不使用“门”。不使用意味着在指令中直接引用目标代码段描述子的选择子。

◆ 向更低特权级转移:可以使用也可以不使用调用门, 但不管使用与否, 都只能发生在RET或IRET两种情况。可以直接引用目标代码段描述子的选择子, 此时,该选择子中的RPL将成为新的CPL2。

◆ 向更高级转移:向更高特权级转移, 必须“门”来实现。举个例子,假设:源代码段的特权级为CPL1;目标代码段的特权级为CPL2;转换过程如下图所示:

我们可以看到,“门”为目标代码段提供了保护,如果不允许低优先级的代码来访问,我可以把我的“门”给关闭,即不设置对应的“门”。

[4] 任务门的存放位置

任务门与中断/自陷/调用门不一样,可在LDT、GDT和IDT任何一个表中。如果将任务门放在IDT表中, 即可以通过访问IDT表来访问任务门, 则可以达到由于中断而发生任务切换的目的。

4.3.5任务状态段描述子

任务状态段(Task State Segment 简称TSS)是Intel用于存放在任务被切换时刻的处理器现场的一个存储段。注意,它是一个段,跟代码段,数据段一样,而且每个任务都有一个TSS。TSS中的内容随着任务的执行不断发生变化。 TSS的内容主要包括:该任务断点各寄存器的内容,指向该任务的LDT选择子, 任务在特权级0、1、2的堆栈指针以及指向前一个任务的TSS的选择子等。

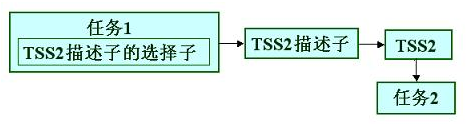

[1] 任务切换的引起。任务切换可由JMP、CALL指令或中断(INT)指令,异常或外部中断引起。JMP、CALL指令可以直接引用一个任务状态段, 也可以先引用一个GDT或LDT中的任务门, 再由任务门的目标选择子引用任务状态段而实现任务转换。中断类的指令则必须先从IDT中引用任务门,再由任务门的目标选择子引用状态任务段而实现任务转换。IRET指令通过引用IDT中的任务门而返回到原任务中去。

[2] 任务切换方式

直接切换 —— 直接引用目标任务状态段描述子的选择子

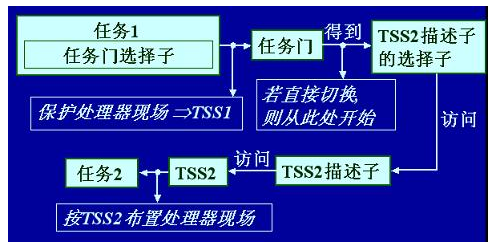

同特权级之间或向更低的特权级切换, 可采用直接切换。直接切换方式不使用任务门,直接引用任务状态段描述子的选择子来访问TSS,以实现任务切换。如下图:

间接切换 —— 从引用任务门开始, 由任务门提供目标任务状态段描述子的选择子。间接切换则可以向任何特权级切换。需要使用任务门。

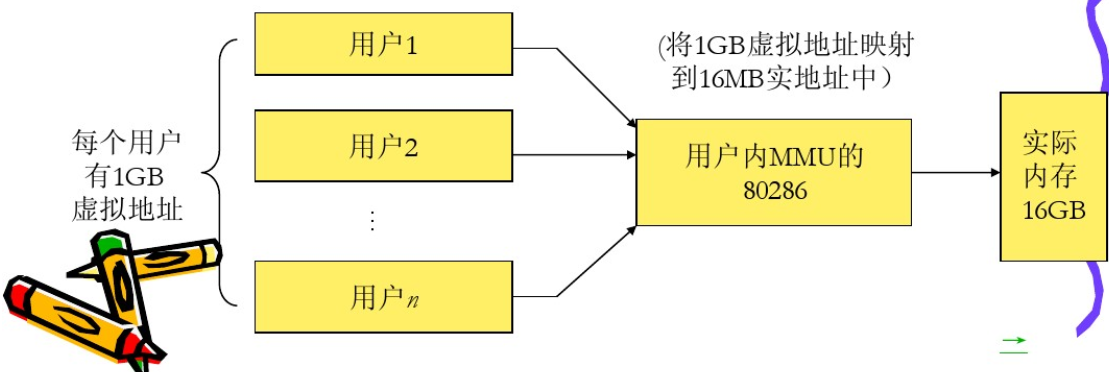

五、80286的内存管理

80286有两种工作模式,在实模式下,跟8086内存管理一样,只能管理和寻址1MB物理内存。而在保护模式下,可以管理224=16MB物理内存。但在保护模式下,采用的32位的虚拟地址来访问虚拟存储器(是指程序可以占有的空间,它并不是内存芯片提供的物理地址空间,而是由大型外部存储器提供的所谓虚拟地址空间),提供虚拟空间1GB。