转载博客:https://www.cnblogs.com/liujinggang/p/9609739.html

主要写的太好了,主要是我看懂了,我也想留下记录,那就把我博客园的第一次留给它吧。

SPI总线传输一共有4种模式,这4种模式分别由时钟极性(CPOL,Clock Polarity)和时钟相位(CPHA,Clock Phase)来定义,其中CPOL参数规定了SCK时钟信号空闲状态的电平,CPHA规定了数据是在SCK时钟的上升沿被采样还是下降沿被采样一、SPI模式

模式0:CPOL= 0,CPHA=0。SCK串行时钟线空闲是为低电平,数据在SCK时钟的上升沿被采样,数据在SCK时钟的下降沿切换

模式1:CPOL= 0,CPHA=1。SCK串行时钟线空闲是为低电平,数据在SCK时钟的下降沿被采样,数据在SCK时钟的上升沿切换

模式2:CPOL= 1,CPHA=0。SCK串行时钟线空闲是为高电平,数据在SCK时钟的下降沿被采样,数据在SCK时钟的上升沿切换

模式3:CPOL= 1,CPHA=1。SCK串行时钟线空闲是为高电平,数据在SCK时钟的上升沿被采样,数据在SCK时钟的下降沿切换

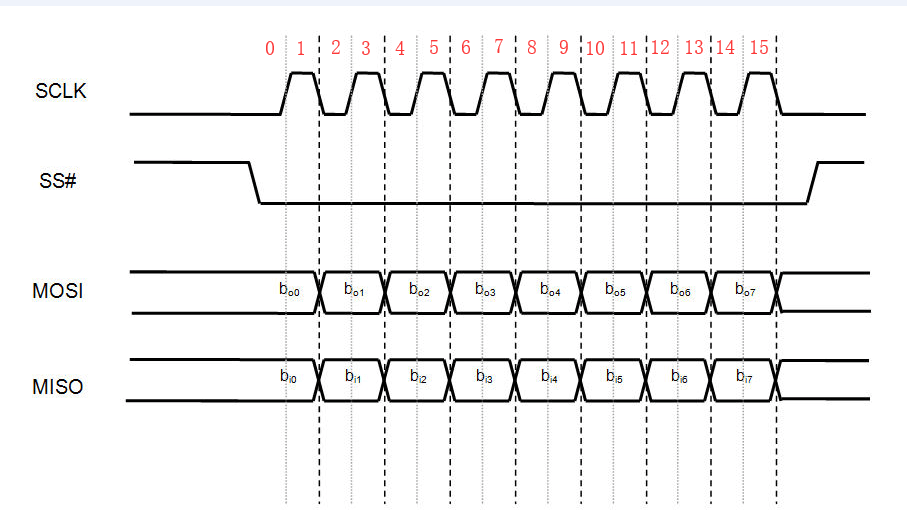

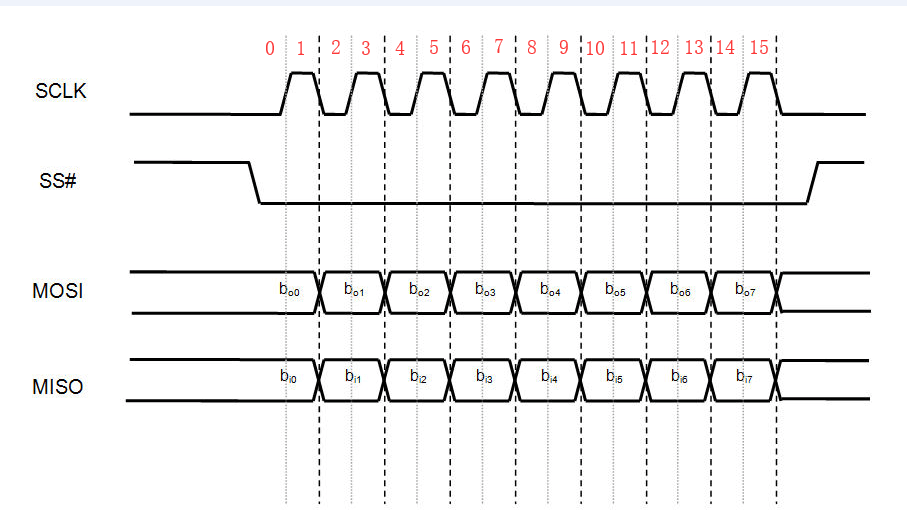

二、SPI时序分析1

下面展现了模式0下的SPI时序图以及分析

模式0:CPOL= 0,CPHA=0。SCK串行时钟线空闲是为低电平,数据在SCK时钟的上升沿被采样,数据在SCK时钟的下降沿切换

发送:当FPGA通过SPI总线往QSPI Flash中发送一个字节(8-bit)的数据时,首先FPGA把CS/SS片选信号设置为0,表示准备开始发送数据,整个发送数据过程其实可以分为16个状态:

状态0:SCK为0,MOSI为要发送的数据的最高位,即I_data_in[7]

状态1:SCK为1,MOSI保持不变

状态2:SCK为0,MOSI为要发送的数据的次高位,即I_data_in[6]

状态3:SCK为1,MOSI保持不变

状态4:SCK为0,MOSI为要发送的数据的下一位,即I_data_in[5]

状态5:SCK为1,MOSI保持不变

状态6:SCK为0,MOSI为要发送的数据的下一位,即I_data_in[4]

状态7:SCK为1,MOSI保持不变

状态8:SCK为0,MOSI为要发送的数据的下一位,即I_data_in[3]

状态9:SCK为1,MOSI保持不变

状态10:SCK为0,MOSI为要发送的数据的下一位,即I_data_in[2]

状态11:SCK为1,MOSI保持不变

状态12:SCK为0,MOSI为要发送的数据的下一位,即I_data_in[1]

状态13:SCK为1,MOSI保持不变

状态14:SCK为0,MOSI为要发送的数据的最低位,即I_data_in[0]

状态15:SCK为1,MOSI保持不变

一个字节数据发送完毕以后,产生一个发送完成标志位O_tx_done并把CS/SS信号拉高完成一次发送。通过观察上面的状态可以发现状态编号为奇数的状态要做的操作实际上是一模一样的,所以写代码的时候为了精简代码,可以把状态号为奇数的状态全部整合到一起。

接收:当FPGA通过SPI总线从QSPI Flash中接收一个字节(8-bit)的数据时,首先FPGA把CS/SS片选信号设置为0,表示准备开始接收数据,整个接收数据过程其实也可以分为16个状态,但是与发送过程不同的是,为了保证接收到的数据准确,必须在数据的正中间采样,也就是说模式0时序图中灰色实线的地方才是代码中锁存数据的地方,所以接收过程的每个状态执行的操作为:

状态0:SCK为0,不锁存MISO上的数据

状态1:SCK为1,锁存MISO上的数据,即把MISO上的数据赋值给O_data_out[7]

状态2:SCK为0,不锁存MISO上的数据

状态3:SCK为1,锁存MISO上的数据,即把MISO上的数据赋值给O_data_out[6]

状态4:SCK为0,不锁存MISO上的数据

状态5:SCK为1,锁存MISO上的数据,即把MISO上的数据赋值给O_data_out[5]

状态6:SCK为0,不锁存MISO上的数据

状态7:SCK为1,锁存MISO上的数据,即把MISO上的数据赋值给O_data_out[4]

状态8:SCK为0,不锁存MISO上的数据

状态9:SCK为1,锁存MISO上的数据,即把MISO上的数据赋值给O_data_out[3]

状态10:SCK为0,不锁存MISO上的数据

状态11:SCK为1,锁存MISO上的数据,即把MISO上的数据赋值给O_data_out[2]

状态12:SCK为0,不锁存MISO上的数据

状态13:SCK为1,锁存MISO上的数据,即把MISO上的数据赋值给O_data_out[1]

状态14:SCK为0,不锁存MISO上的数据

状态15:SCK为1,锁存MISO上的数据,即把MISO上的数据赋值给O_data_out[0]

一个字节数据接收完毕以后,产生一个接收完成标志位O_rx_done并把CS/SS信号拉高完成一次数据的接收。通过观察上面的状态可以发现状态编号为偶数的状态要做的操作实际上是一模一样的,所以写代码的时候为了精简代码,可以把状态号为偶数的状态全部整合到一起。而这一点刚好与发送过程的状态刚好相反。

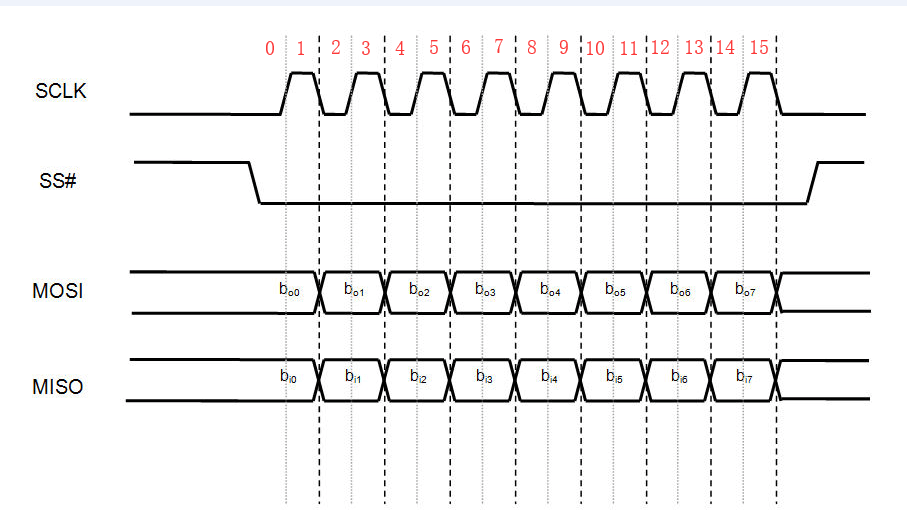

三、SPI时序分析2

自己看,连续发送4个字节数据(0x90 0x00 0x00 0x00)和连续接收2个字节数据(0xEF 0x17)。多看枫叶那边波形还是有意义的呢!!

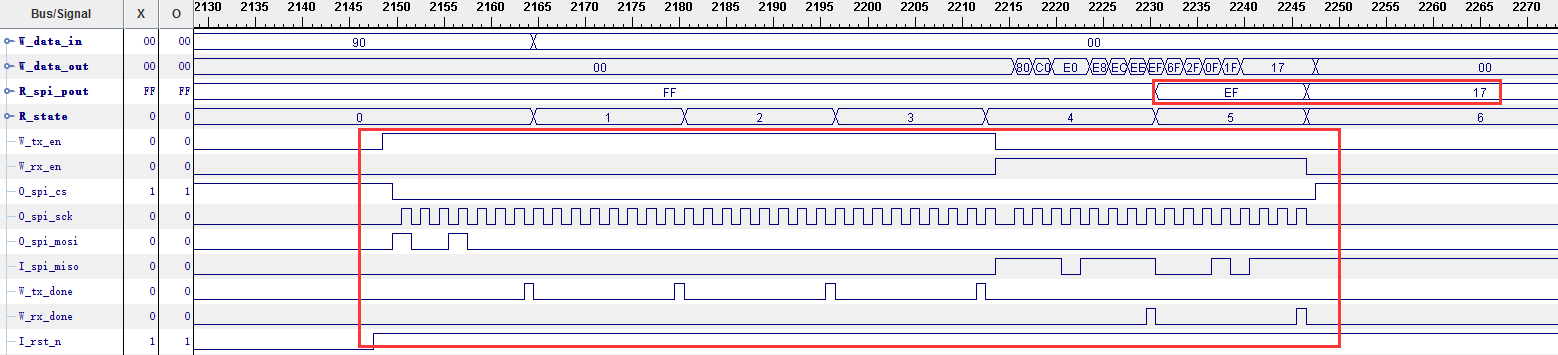

四、SPI时序分析3

解释一下波形,何时拉高O_tx_done。

在做这件事情之前,在重复理解一下SPI发送过程的时序:

状态0:SCK为0,MOSI为要发送的数据的最高位,即I_data_in[7],拉低O_tx_done信号

状态1:SCK为1,MOSI保持不变,拉低O_tx_done信号

状态2:SCK为0,MOSI为要发送的数据的次高位,即I_data_in[6] ,拉低O_tx_done信号

状态3:SCK为1,MOSI保持不变,拉低O_tx_done信号

状态4:SCK为0,MOSI为要发送的数据的下一位,即I_data_in[5] ,拉低O_tx_done信号

状态5:SCK为1,MOSI保持不变,拉低O_tx_done信号

状态6:SCK为0,MOSI为要发送的数据的下一位,即I_data_in[4] ,拉低O_tx_done信号

状态7:SCK为1,MOSI保持不变,拉低O_tx_done信号

状态8:SCK为0,MOSI为要发送的数据的下一位,即I_data_in[3] ,拉低O_tx_done信号

状态9:SCK为1,MOSI保持不变,拉低O_tx_done信号

状态10:SCK为0,MOSI为要发送的数据的下一位,即I_data_in[2] ,拉低O_tx_done信号

状态11:SCK为1,MOSI保持不变,拉低O_tx_done信号

状态12:SCK为0,MOSI为要发送的数据的下一位,即I_data_in[1] ,拉低O_tx_done信号

状态13:SCK为1,MOSI保持不变,拉低O_tx_done信号

状态14:SCK为0,MOSI为要发送的数据的最低位,即I_data_in[0] ,拉高O_tx_done信号

状态15:SCK为1,MOSI保持不变,拉低O_tx_done信号

可以看出,每一个bit为实际上是占了2个时钟周期(这里的时钟周期指的是系统时钟I_clk),发送一个字节完成标志位O_tx_done信号是在第14个状态拉高的,也就是在最后一个bit的前时钟周期产生了一个高电平,我之所以这么做的目的一是为了更好的整合代码,把偶数状态全部归类到一起,二是为了在连续发送数据时,在检测到O_tx_done信号为高以后,可以提前把下一次要发送的数据准备好。

五、重点看链接,写的太好了,一定是高手。

https://www.cnblogs.com/liujinggang/p/9609739.html