CTS基础知识

1、基础

1、概念和指标:https://www.sohu.com/a/219354626_99933533

2、CTS之前需要确认的

(a)placement已经完成

(b)power和ground nets已经preroute

(c)预估的congestion可以接受

(d)预估的setup timing可以接受(10%-15% still fine)

(e)预估的max cap/transition - 没有违规

(f)高扇出net:Reset和Scan Enable已经插入buffer,clock 还没有插buffer

3、插clock buffer的作用

(a)平衡时钟负载,同时满足DRC

(b)通过sizing最小化skew

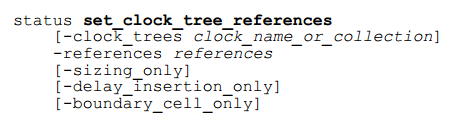

2、CTS setup需要做哪些事情?

(a)设定目标:尽可能在满足要求的前提下放松clock skew目标,这可以减少总体的buffer数量以及运行时间

set_clock_tree_options

-clock_trees clk1

-target_early_delay 0.9

-target_skew 0.1

(b)设置约束

(c)设置控制策略

(d)设置NDRs

1、目标

(a)满足DRC,即max_transition_time、max_capacitance、max_fanout、max_buffer_levels

(b)尽力去满足时钟树的target,即skew和insertion delay

2、如何选择做CTS的buffer/inveter?

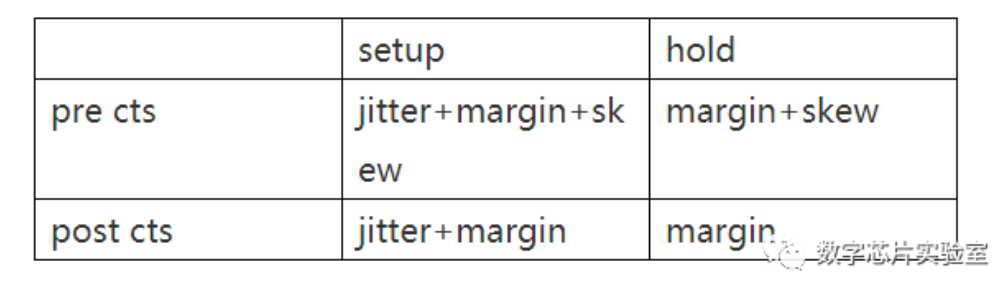

3、从uncertainty中移除skew

在CTS之前,uncertainty包括skew,而在CTS之后工具可以就算出实际的skew,就可以减少uncertainty的值。

对于setup/hold,uncertainty的设置也是不同的,因为hold一般是检查时钟的同一周期的同一沿,jitter对launch path和capture path的影响相同,jitter是时钟周期间的不一致性,因此不影响。

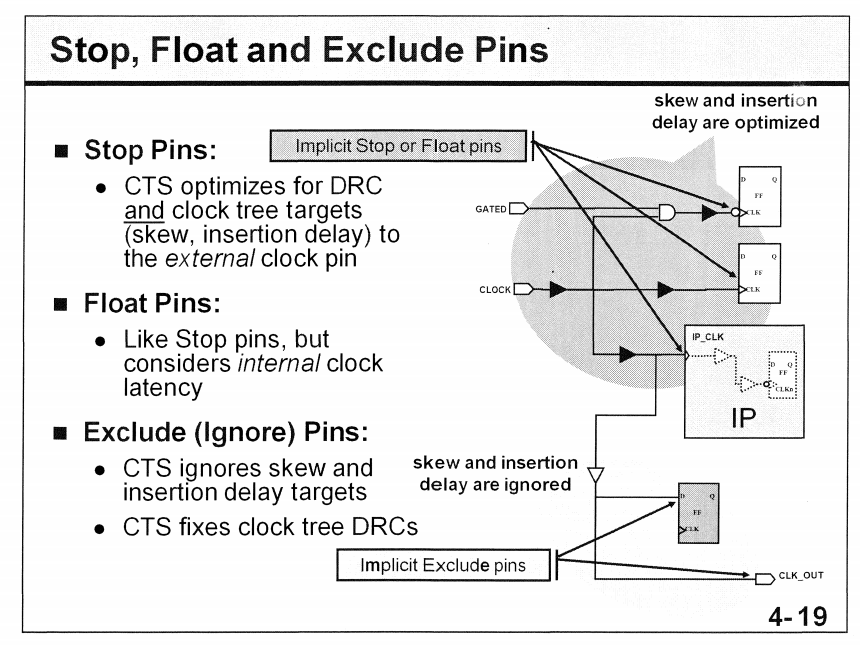

4、时钟树的起点和终点是什么?

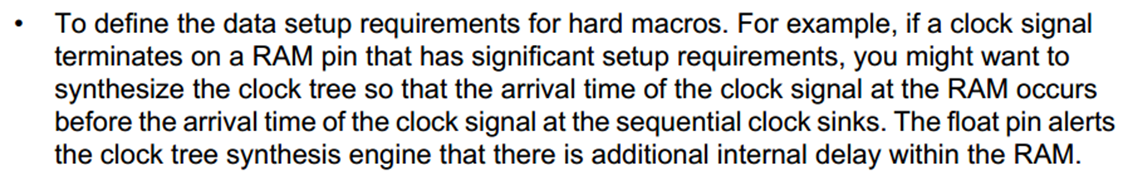

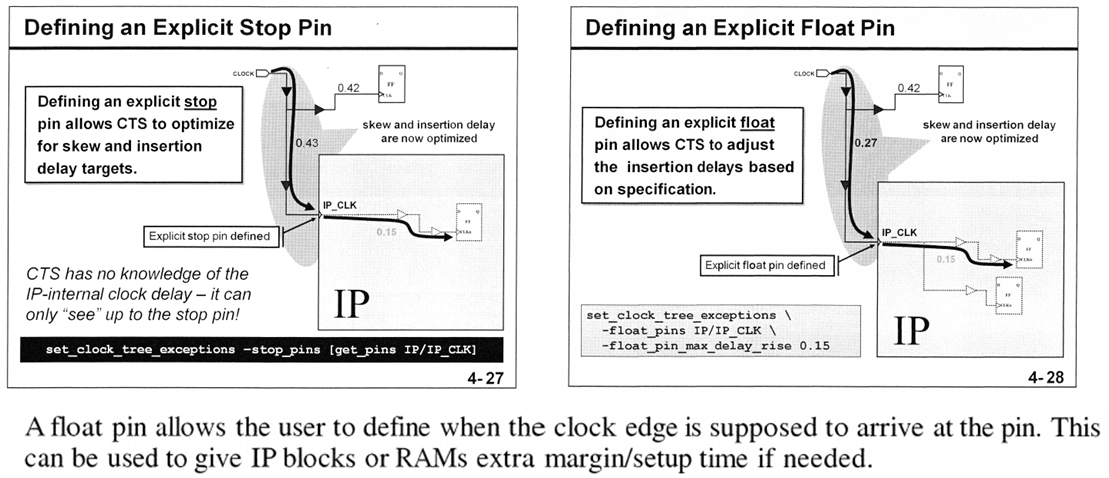

时钟树开始于SDC-defined的clock source,即create_clock,终止于寄存器和macro的时钟pin (stop或者float pins)

5、Stop、Float、Exclude pin的区别?

一般而言,

Stop(sync) pins

时序单元的时钟引脚

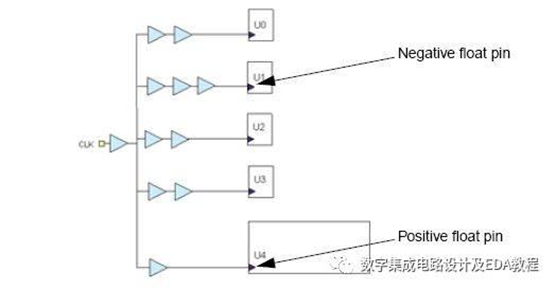

Float pins:

macro的clock引脚

# Specifying a negative float pin

icc_shell>set_clock_tree_exceptions -float_pins U1/CLK

-float_pin_max_delay_rise -0.5 -float_pin_max_delay_fall -0.5

# Specifying a positive float pin

icc_shell>set_clock_tree_exceptions -float_pins U4/CLK

-float_pin_max_delay_rise 0.5 -float_pin_max_delay_fall 0.5

Float pin和stop pin的区别:

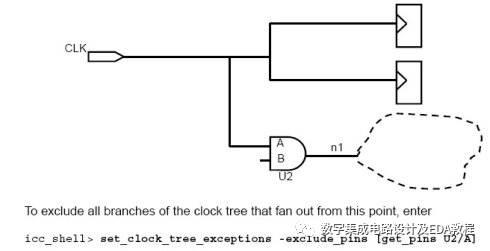

Exclude (ignore) pins:

时序单元的non-clock引脚(D,set,reset)

输出端口

组合逻辑单元或者ICG的pin

MUX的选择端

等等……

BNN项目的一些问题

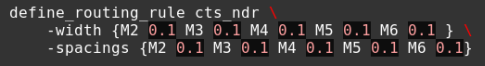

1、NDR规则怎么设置的?

但好像使用的是M4,M5,M6走线

2、时钟网络是什么样的?

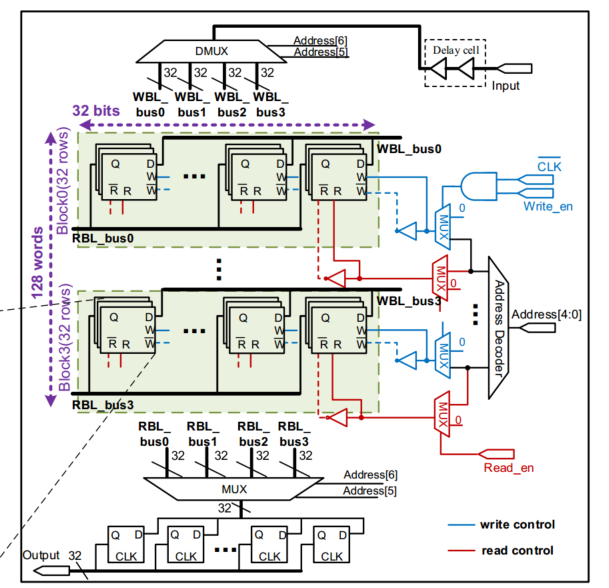

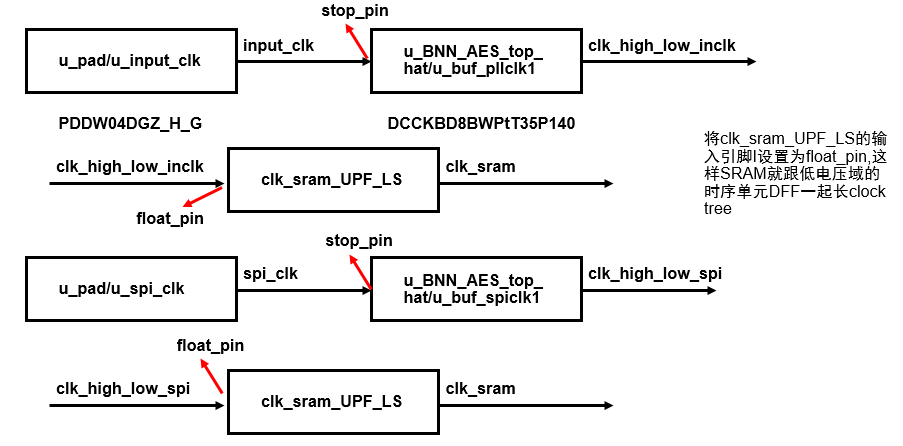

(a)芯片外围通过pad输入2个clk:u_input_clk(20MHz)和u_spi_clk(10MHz),前者是系统时钟,后者是SPI打数据的时钟

(b)在SDC创建了5个clock,分别是高电压域的input_clk,spi_clk,clk_sram,低电压域的clk_high_low_inclk,clk_high_low_spi,对5个clock分别长clock tree

(c)u_buf_pllclk1和u_buf_spiclk1的输入引脚被设置为stop_pin,clk_sram_UPF_LS的输入引脚被设置为float pin,指定的内部delay为0.14

2、时钟树的options怎么设置的?

target_skew=0.0

max_buffer_level=70

max_transition=1.5(H)或0.15(L)

max_capacitance=0.05

max_fanout=24

Memory Block

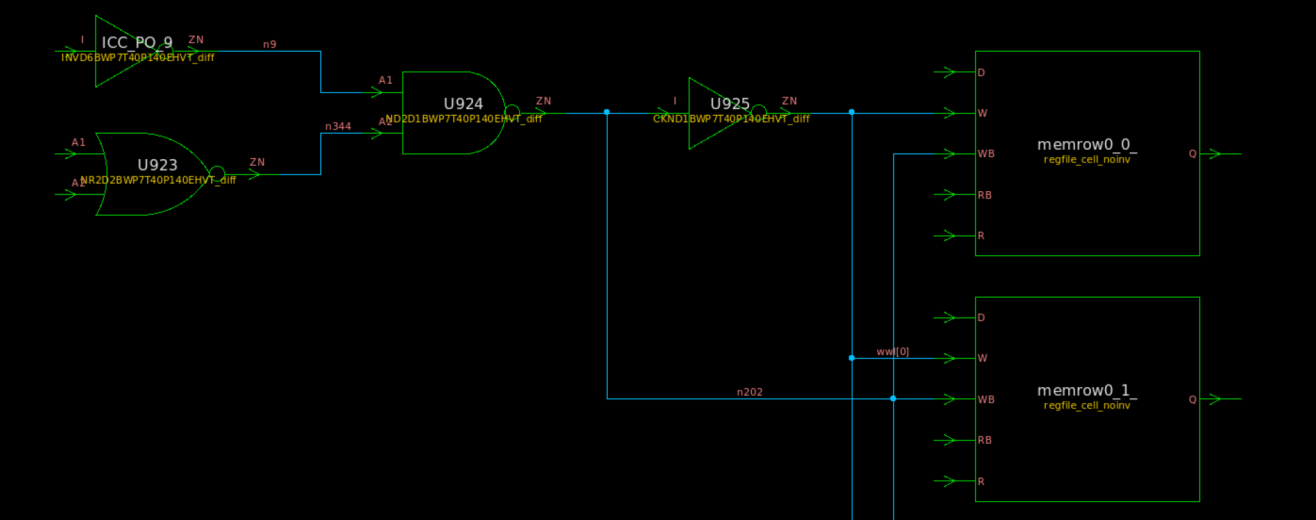

1、分析regfile_cell的W引脚

打开原理图方法:MainWindow菜单栏的Schematic

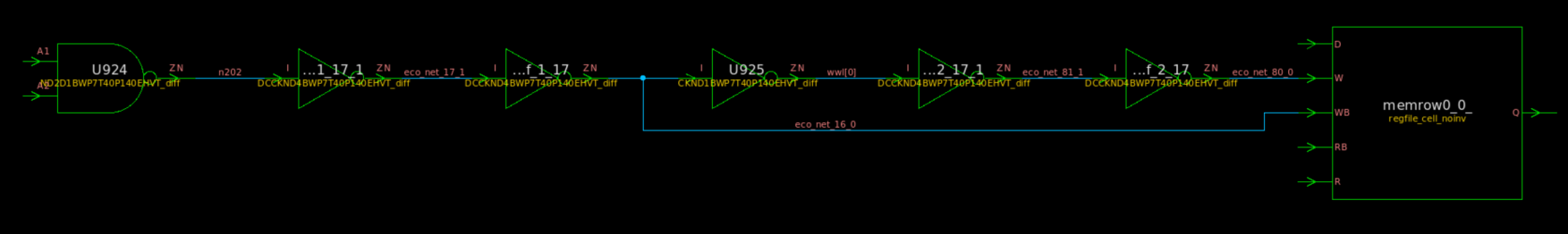

从下面的原理图可以看到,W由一个反相器驱动,WB由一个与非门驱动,手动CTS就是在这两个门的输出插DCCKND4

对于64x32的block,就要插入64x2=128个这样的DCCKND4

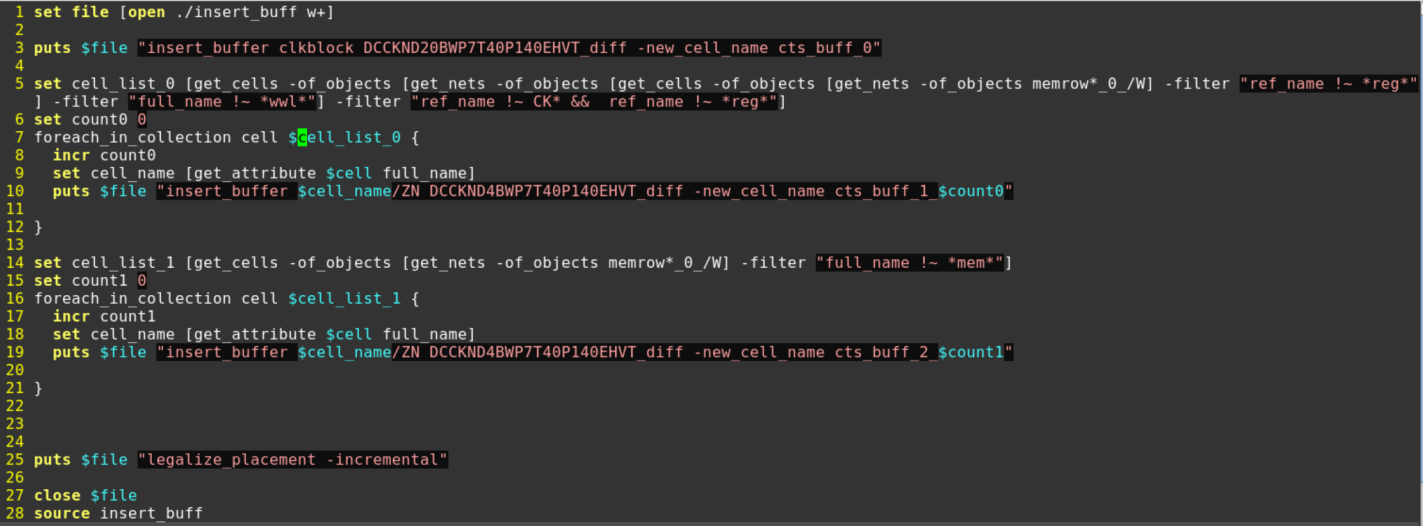

2、插buf脚本

从regfile的W引脚往上抓,直到抓到反相器(cell_list_1)和与非门(cell_list_2)

3、插入clock buf后的原理图

可以看到,在U924和U925的输出pin后面都接上了clock buf(由2个DCCKND4构成)

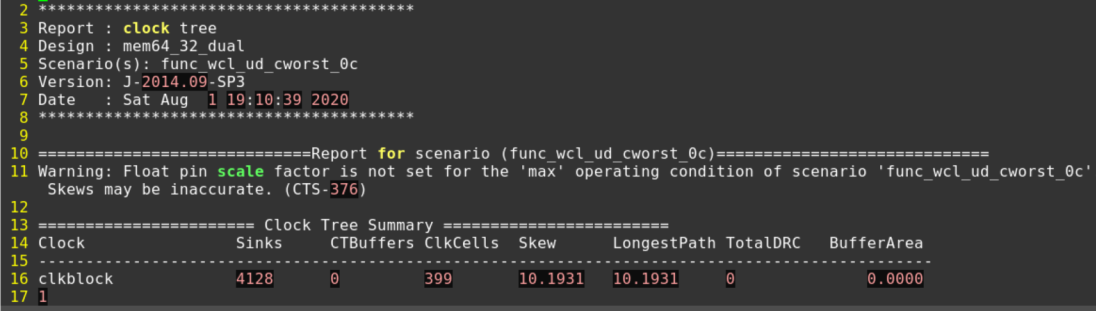

4、report时钟树的相关信息

report_clock_tree

-drc_violators

-exceptions

-summary

从以下报表可以看到,skew为10.19ns

5、将时钟设为propagated clock后检查时序

set_propagated_clock [all_clock]

report_clock_tree -summary

report_clock_timing -type latency

report_constraint -all_violators

6、memory block原理图