https://mp.weixin.qq.com/s/rXYqiZKuBpAYL8R94zxgRA

Chisel允许用户根据需要,把基本数据类型组合成为复合数据类型使用。如C语言里面的结构体,这样可以极大的简化Verilog中输入输出接口的声明和使用。

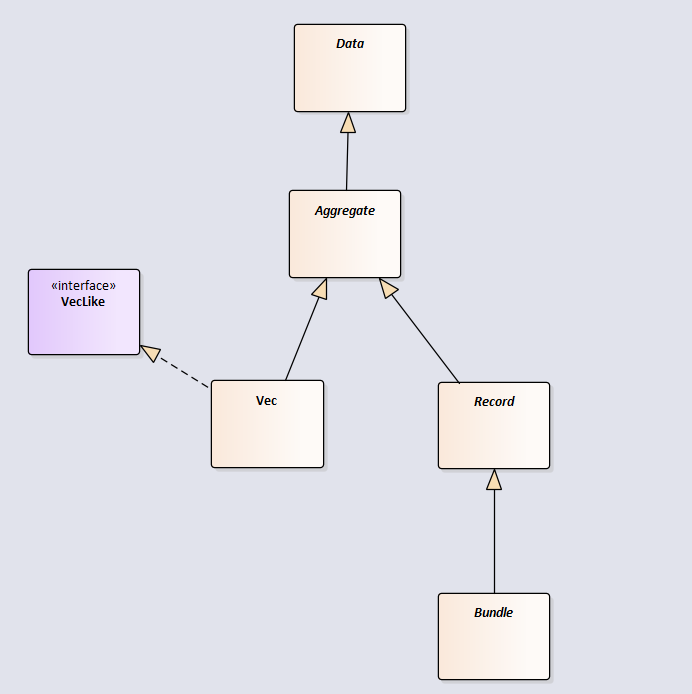

复合数据类型相关的类如下:

其中:

1. 实线箭头为继承父类(extends);

2. 虚线箭头为实现接口(with);

3. 倾斜字体的类为抽象类(abstract);

4. 标注为叶子(leaf)的为最终类(final);

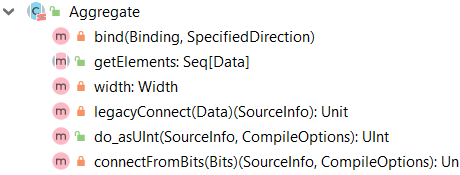

1. Aggregate

An abstract class for data types that solely consist of (are an aggregate of) other Data objects.

所有复合数据类型的父类。

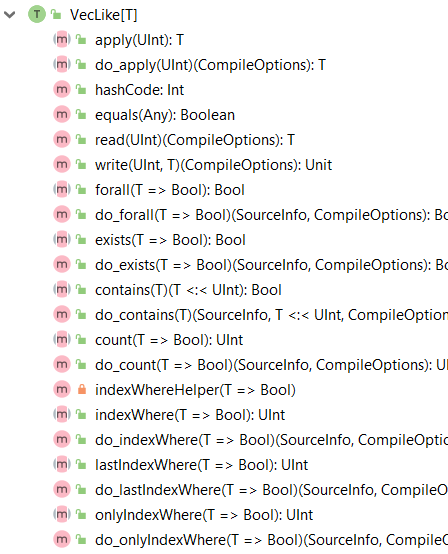

2. VecLike

A trait for Vecs containing common hardware generators for collection operations.

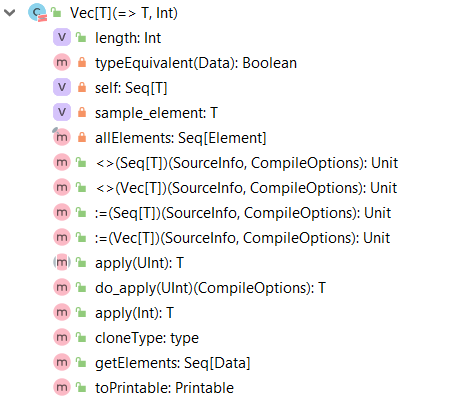

3. Vec

用于创建一个数据类型为T的数组,T为Data的子类。

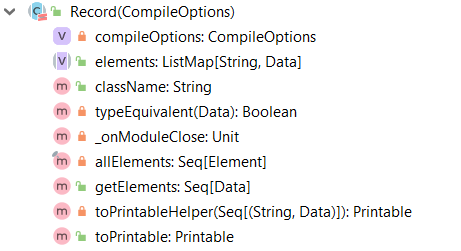

4. Record

用于存放组成复合类型的基本数据类型变量的<名称,类型>键值对。实际使用中用不到。

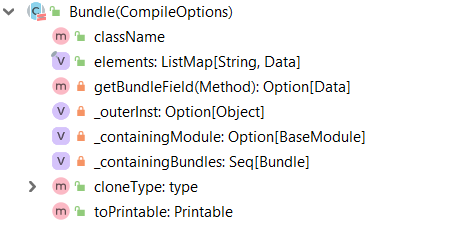

5. Bundle

Base class for data types defined as a bundle of other data types.

抽象类,作为复合数据类型的基类,用于自定义复合数据类型(匿名类或命名类)。

如:

class MyModule extends Module {

val io = IO(new Bundle {

val in = Input(UInt(64.W))

val out = Output(SInt(128.W))

})

}

再如:

class MyFloat extends Bundle {

val sign = Bool()

val exponent = UInt(8.W)

val significand = UInt(23.W)

}

val x = new MyFloat()

val xs = x.sign