1、DDR3管脚定义

》CK/CK# 全局差分时钟,所有控制和地址输入信号在CK上升沿和CK#的下降沿交叉处被采样,输出数据选通(DQS、DQS#)参考与CK和CK#的交叉点。

》CKE为时钟使能信号,使能(高)和禁止(低)内电路和DRAM上的时钟。由DDR3 SDRAM配置和操作模式决定特定电路被使能和禁止。CKE为低时,提供预充电和自刷新操作(所有Bank都处于空闲),或有效掉电(在任何Bank里的行有效)。CKE与掉电状态的进入、退出以及自刷新的进入同步。CKE与自刷新的退出异步,输入Buffer(除了CKE、CK#、RESET#和ODT)在掉电期间被禁止。输入Buffer(除了CKE和RESET#)在自刷新期间被禁止。CKE的参考值是VREFCA。

》CS#为片选信号,使能(低)和禁止(高)命令译码,大部分CS#为高时,所有命令被屏蔽、CS#提供了多Bank系统的Bank选择功能,CS#是命令代码的一部分,CS#的参考值是VREFCA。

》ODT片上终端使能。ODT使能(高)和禁止(低)片内终端电阻,在正常操作使能时,ODT仅对下面的引脚有效:DQ[7:0]、DQS、DQS#和DM。如果通过LOAD MODE命令禁止,OTD输入被忽略。OTD的参考值是VREFCA。

》BA0、BA1、BA2为BANK地址输入,用来确定当前的命令操作对哪个BANK有效。BA[2:0]定义在LOAD MODE命令器件哪个模式(MR0、MR1、MR2)被装载,BA[2:0]的参考值是VREFCA.

》A0~A9、A10/AP、A11、A12/BC#、A13为地址总线,为有效命令提供行地址,同时为读、写命令提供列地址和自动预充电位(A10),以便从某个Bank的内存阵列里选出一个位置。LOAD MODE命令器件,地址输入提供一个操作码。地址输入的参考值是VRECA。A12/BC#是在模式寄存器(MR)使能时,A12在读和写命令期间被采样,已决定burst chop(on-the-fly)是否被执行(HIGH=BL8执行burst chop)或者LOW-BC4不执行burst chop。

》RAS#、CAS#、WE#分别为 行 选择、列 选择与 写 使能信号,低电平有效。这三个信号与CS#一起组成了DDR的命令信号。

》DM为数据 掩码 (屏蔽)信号,写数据时,当伴随输入数据的DM信号被采样为高时,输入数据被屏蔽。当然DM仅作为输入脚,但是,DM负载设计成与DQ和DQS脚负载相匹配。DM的参考值是VREFCA。DM可选作为TDQS。

》DQ0~DQ7为数据总线,读写操作时的数据信号通过该总线输入或输出。

》RESET#为复位信号,低有效,参考值是VSS。

》DQS、DQS#为数据选通(锁存)信号,双沿有效,写数据时输入,信号沿与数据中心对齐、读数据时输出,信号沿以数据边沿对齐。

》TDQS、TDQS#输出信号,终端数据选通,当TDQS使能时,DM禁止,TDQS和TDDS提供终端电阻。

》VDD电源电压1.5V±0.075V。

》VEDO为DQ电源1.5V±0.075V。为了降低噪声,在芯片上进行了隔离。

》VREFCA为控制、命令、地址的参考电压。VREFCA在所有时刻(包括自刷新)都必须保持规定的电压。

》VREFDQ为数据的参考电压。VREFDQ在所有时刻(除了自刷新)都必须保持规定的电压。

》VSS为地。

》VSSQ为DQ地,为了降低噪声,在芯片上进行了隔离。

》ZQ输出驱动校准的外部参考,这个引脚应该连接240 ohm电阻到VSSQ。

2、启动过程

首先,芯片进入上电,在上电最小为200us的平稳电平后,等待500usCKE使能,在这段时间芯片内部开始状态初始化,该过程与外部时钟无关。在时钟使能信号前(cke),必须保持最小10ns或者5个时钟周期,除此之外,还需要一个NOP命令或者Deselect命令出现在CKE的前面。然后DDR3开始了ODT的过程,在复位和CKE有效之前,ODT始终为高阻。在CKE为高后,等待tXPR(最小复位CKE时间),然后开始从MRS中读取模式寄存器。然后加载MR2、MR3的寄存器,来配置应用设置;然后使能DLL,并且对DLL复位。接着便是启动ZQCL命令,来开始ZQ校准过程。等待校准结束后,DDR3就进入了可以正常操作的状态。对于基本的配置过程,现在就可以结束了。

2、信号组大致分类

》地址线、时钟差分、命令控制线,该组信号较多,布线不一定非要走在同一层

》8根数据高位、1根数据掩码、1对数据锁存差分,共11根线,同一组信号线走同一层。

》8根数据低位、1根数据掩码、1对数据锁存差分,共11根线,同一组信号线走同一层。

备注:同组信号必须走同一层,不同组信号可走不同层。

》电源和地

3、布线规则

>>信号线尽量不走顶层或底层,在焊盘就近打过孔,走中间层,顶层或底层信号走线传输速率相对中间层走线要慢,顶层和底层不走线,便于摆放元器件。

>>打过孔尽量对齐摆放,美观、更有利于线拉通

>>同组信号中,优先拉通差分线,同时给差分线对提前多预留的空间,便于后续做等长。

>>布线满足3W原则,如线宽W = 0.1mm,线与线的中心距离为3W = 0.3mm, 线与线边沿的距离也就是2W = 0.2mm。防止信号间的串扰。

>>单端50 ohm,差分100 ohm。

>>完整的参考平面。

>>不要有其他信号穿插到DDR布线区域。

>>VREF电源线尽量走宽 >=20~30mil。

>>差分对误差尽量控制在5mil。

>>数据线误差尽量控制在+/-20mil

>>地址线误差尽量控制在+/-50mil

4、CPU和DDR、DDR和DDR之间的摆放间距(参考别人的经验值)

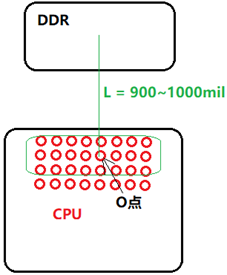

》一个CPU只对一个DDR时,间距大概900~1000mil,如果中间有串阻,范围1000~1300mil。

注意:这个距离不是CPU 中心到DDR中心的距离,而是CPU与DDR相关的焊盘一个大致区域中心到DDR的中心。

》一个CPU对两个DDR时,两个DDR相对CPU摆放时要严格对称(也是相对O点进行对称)。

5、走线方式:点对点,T型拓扑方式、菊花链拓扑方式

》点对点,一个CPU 仅对一个DDR, 只能用点对点的方式布线。

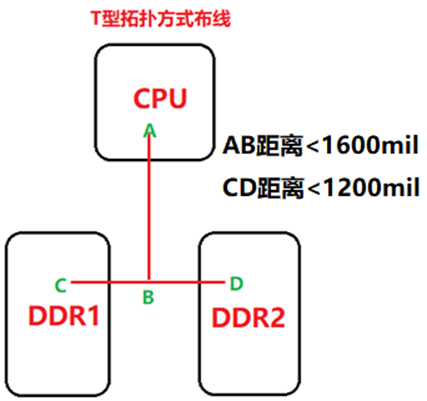

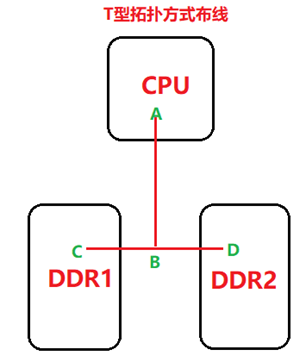

》T型:一个CPU对两个DDR 或4个DDR,线从A点到B点,B点分支分别到C和D点。

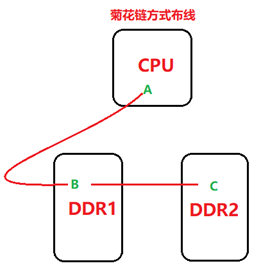

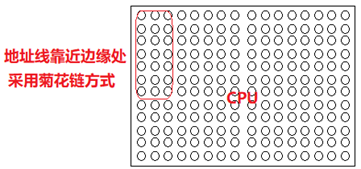

》菊花链,一个CPU对两个DDR 或4个DDR,下图线从A点到B点,B点再到C点。

小记:

>>菊花链方式的型号完整性相对好点,一般大品牌走的大都是菊花链。

>>快速的辨别是哪种方式,可以直接查看地址线组。

>>当有两个DDR时,如何判定用T型还是用菊花链,主要看CPU的地址线焊盘的位置。

如果地址线的焊盘在CPU BGA的边缘处,可以考虑用菊花链,如果是靠近中间考虑T型。

如果地址线的焊盘靠近边沿的中间处,可以考虑T型方式。

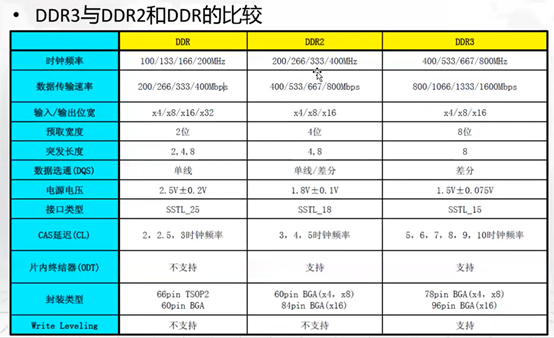

最容易区分出DDR1/2/3,主要看电源电压。