总览:

-

数制与编码

-

进位计数制及其相互转换

-

真值和机器数

-

BCD码

-

校验码

-

-

定点数的表示和运算

-

定点数的表示

无符号数的表示,有符号数的表示

-

定点数的运算

定点数的位移运算,原码定点数的加/减运算,补码定点数的加/减运算,定点数的乘/除运算,溢出的概念和判别方法。

-

-

浮点数的表示和运算

-

浮点数的表示

IEEE754标准

-

浮点数的加/减运算

-

-

算术逻辑单元(ALU)

-

串行加法器和并行加法器

-

算术逻辑单元的功能和结构

-

-

数制与编码

-

进位计数制及其相互转换

-

二进制、八进制、十进制、十六进制相互转换

-

十进制转二进制:整数部分除2取余,逆序书写,商成为新的操作数;小数部分,乘2取整,顺序书写,余数成为新的操作数

-

二进制转十进制:第i位的值乘2^i求和,小数点前为第0位,小数点后为第-1位

-

其余数制借助二进制转换

-

-

计算机内部采用二进制编码的好处

-

基本符号少,易于静态电路实现

-

编码、计数、运算等的规则简单

-

逻辑命题"真"和"假"与0和1对应

-

-

-

真值和机器数

-

BCD码

常见分为两类有权BCD码(8421/2421/5421等)和无权BCD码(如余3码、格雷码等)

-

8421码

使用四位二进制数表示一位十进制数'0' ~ '9',每位权重8421;十六进制数C表示'+',D表示'-';十进制位数为偶数时,第一个字节的高4位补"0"

-

余3码

在8421的基础上,加上十进制的3

-

2421码

权重2421;若十进制数大于等于5,则最高位是1;若小于5,则最高位是0

-

字符与字符串

-

ASCII

'0' 48 'A' 65 'a' 97

-

汉字编码

-

字符串的大小端存放

-

小端:从低位到高位依次存放数据

-

大端:从高位到低位依次存放数据

-

-

-

校验码

-

奇偶校验码

-

奇校验:添加一位校验码后,是的整个码字里面1的个数是奇数;接收端收到数据后就校验数据里面1的个数,如果正好为奇数,则认为传输没有出错;如果检测到偶数个1,则说明传输过程中,数据发生了改变,要求重发。

-

偶校验:添加一位校验码后,是的整个码字里面1的个数是偶数;接收端收到数据后就校验数据里面1的个数,如果正好为偶数,则认为传输没有出错;如果检测到奇数个1,则说明传输过程中,数据发生了改变,要求重发。

-

只具有检错功能,不具有纠错功能;一位发生变化可以检测出来,多位变化无法检测

-

-

循环冗余校验(CRC)码(P145)

-

可以发现并纠正信息在存储和传送过程中连续出现的多位错误代码。

-

K位校验位;k+1位生成多项式

-

循环校验码用约定的G(x)去除,如果无措,余数全为0,如果某一位出错,则余数不为0。不同的出错位其余数不同,出错位的余数对应G(x)的出错模式。

-

特性:

-

具有r检测位的多项式能够检测出多有小于或等于r的突发错误。

-

长度大于r+1的错误逃脱的概率是1/2^r

-

-

-

海明码(P100)

-

纠错编码

-

具有一位纠错能力。信息位有k位,校验位有r位,满足2^r >= k + r + 1

-

海明码求解步骤:

-

确定校验码的位数r

-

确定校验码的位置 2^(i - 1)

-

确定数据的位置

-

求校验位的值:被校验数据码的海明位号等于校验该数据码的各校验码海明位号之和,且校验码不需要在被校验

-

-

常用的(n, k)海明码中,冗余位的位数是 n - k

-

-

-

-

定点数的表示和计算

-

定点数的表示

-

定点数-1的补码是1.0000,原码定点数中不存在-1

-

原码和反码0的表示都有两种,补码只有一种

-

移码和补码符号位相反;移码真值大的表示形式就大;0~[2^(n+1) - 1]

-

-

定点数的运算

-

采用补码

-

-1的补码全为1, 0的补码全为0;最小负数的补码永远首位是1,其余位全是0

-

定点数的移位运算

-

逻辑移位

逻辑左移时,高位移丢,低位补0;逻辑右移时,低位移丢,高位填0

-

算术移位

-

当机器数为正时

-

原码:补码:反码:左移右移都补0

-

-

当机器数为负时:

-

原码:空位填0,符号位不变

-

反码:空位填1,符号位不变

-

补码:左移填0,右移填1

-

-

对精度的影响(天P35)

-

-

-

原码定点数的加/减运算

-

补码定点数的加/减运算

-

溢出的概念和判别方法(天P37)

-

定点数的乘法运算

-

原码一位乘

-

原码两位乘

-

补码一位乘

-

补码两位乘

-

-

定点数的除法运算

-

原码恢复余数法

-

原码不恢复余数法

-

补码不恢复余数法

-

-

-

浮点数的表示和运算

-

浮点数的表示

阶码 尾数

IEEE754标准:尾数用原码表示,阶码用移码表示

-

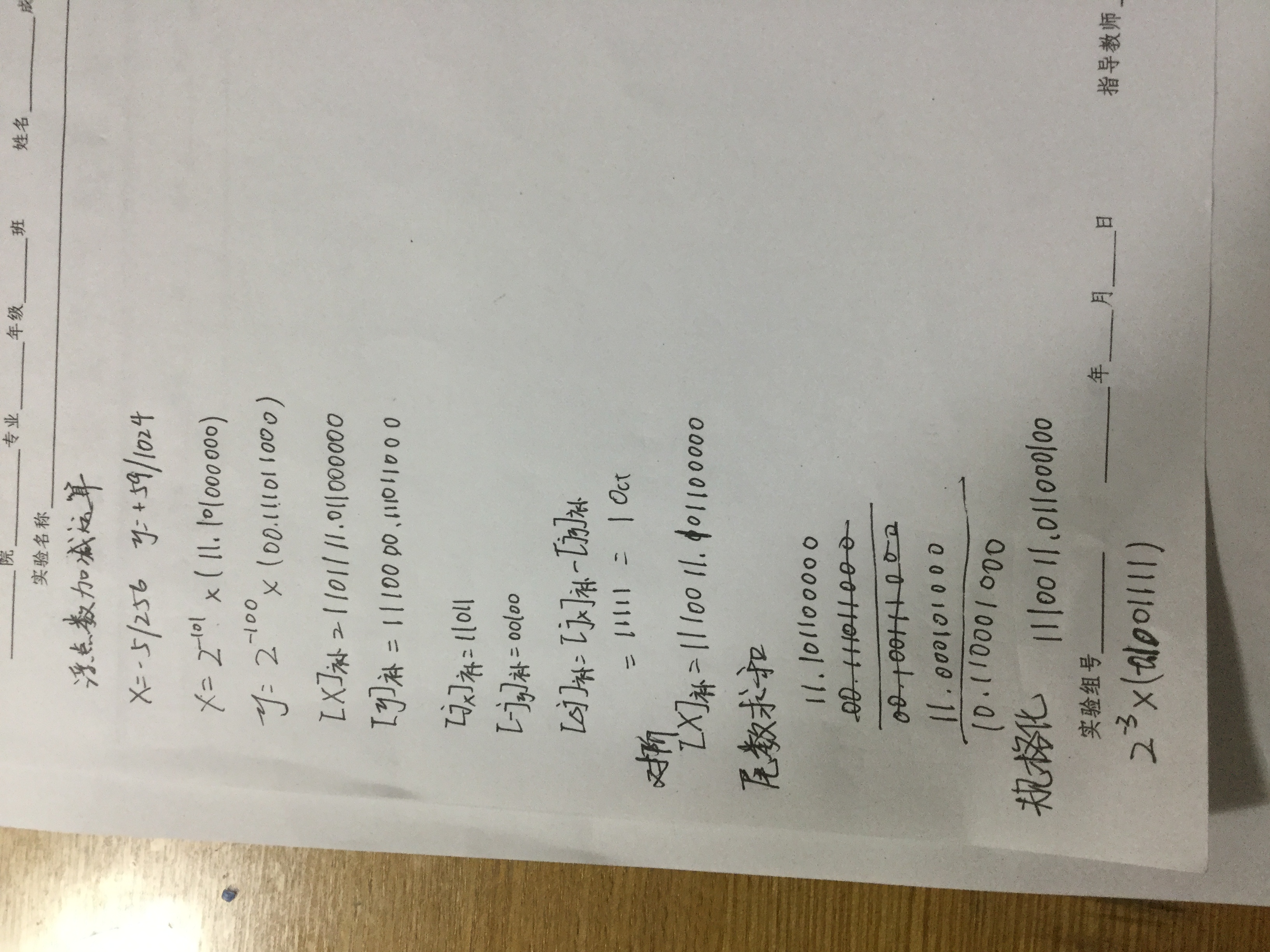

浮点数的加/减运算

-

步骤:对阶;尾数求和;规格化;舍入

-

-

-

算术逻辑单元

-

串行加法器和并行加法器

-

全加器和半加器

-

串行加法器

-

并行加法器

-

串行进位链

-

并行进位链

-

进位函数

-

单重分组跳跃进位链

-

双重分组跳跃进位链

-

-

-

算术逻辑单元的功能和结构

-

组合逻辑电路

-

时序逻辑电路

-

ALU

-

-

-

复习感想:

二三章东西真的是太多了,总结起来也是真的多,不总结一些又遗忘的太快,况且二三章还那么重要。看完二三章,后面的就相对较少一点了,感觉计算机组成比数据结构麻烦多了。前两天发烧,拖更了一天,不过,反正也没人看。