英文题目:Using the Zynq SoC Processing System,参考自ADI的ug1165文档。

利用Zynq Soc创建一个嵌入式工程,该工程总体上包括五个步骤:

步骤一、新建空白工程

步骤二、创建一个Embedded Processor工程

步骤三、Zynq7 Processing System的管理

步骤四、综合仿真、编译运行、生成二进制文件

步骤五、Exporting Hardware to SDK

步骤一、新建工程

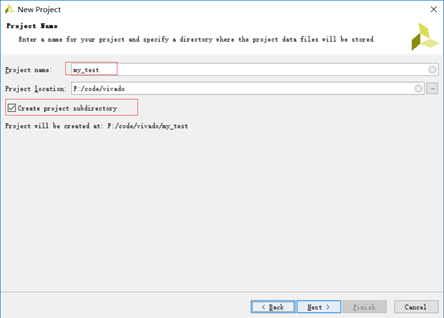

1. 点击Vivado图标启动软件,Create New Project 新工程。假定创建工程名为my_test,选择打勾方框[checked]

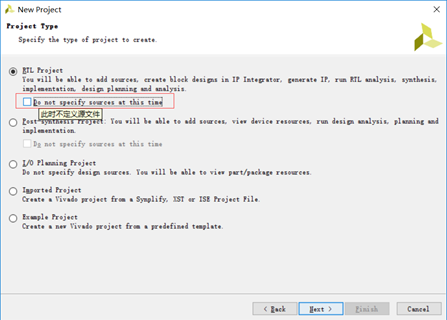

2. 选中RTL Project,注意下面方框不选中[Unchecked]。其它不选择。

3. 接下来Add Sources、Add Existing IP、Add Constraints三个界面不做任何改变,一路next。

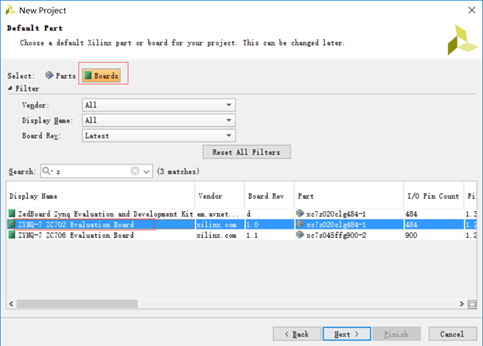

4. 选择 Board选项,搜索ZYNQ-7 ZC702 Evaluation Board作为开发板。

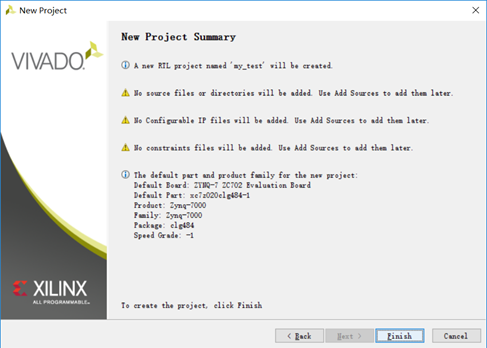

5. 点击Finish,至此一个空工程建立完毕。

步骤二、创建一个Embedded Processor工程。

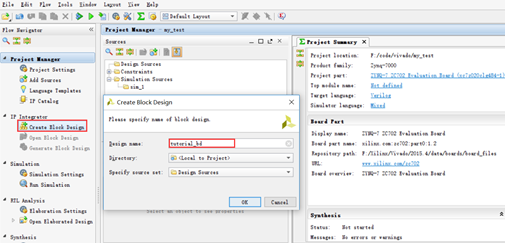

1. 在IP Integrator下,点击 Create Block Design.创建块的设计名为tutorial_bd,其它不变,点击OK.

2. 初始化后,在右侧Diagram下选择 Add IP图标按钮,在弹出框中输入zynq搜索IP核ZYNQ7,按Enter键确认。

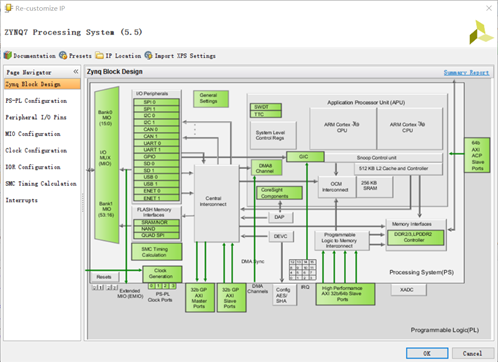

3. 双击ZYNQ Processing System该IP核,进入Block Design界面如下所示。

步骤三、Zynq7 Processing System的管理

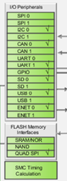

1. 点击Presets按钮,选择ZC702。此时左侧选择各个外设均有变化。

I/O Peripherals 部分引脚被选中。

MIO Configuration 中MIO设备部分被选中。

2. 点击OK关闭自定义IP核界面,此时IP核按照预先ZC702开发板来配置。

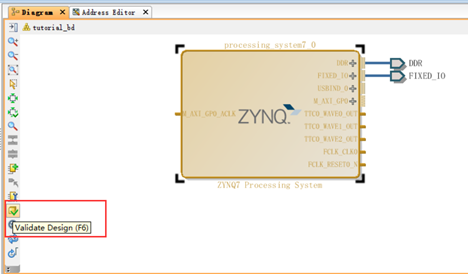

3. 点击Run Block Automation运行,没有报错。

4. 右键点击Diagram中空白处,选择Validate Design

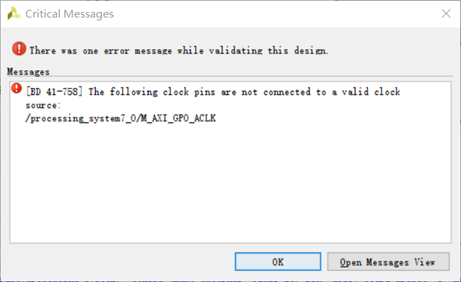

此时,弹出错误框

5. 将鼠标放在M_AXI_GP0_ACLK 端口,产生画笔性质后连线至 FCLK_CLK0,重新选择Validate Design,显示成功并点击OK。

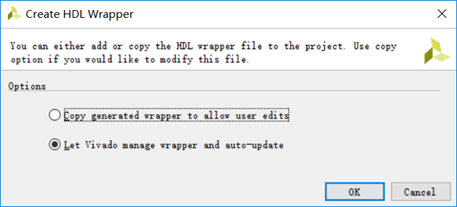

6. 在Block Design视窗, 选择Sources项。在 Design Sources下, 右键单击 tutorial_bd并选择Create HDL Wrapper.

7. 在弹出框选择Let Vivado manage wrapper and auto-update并点击OK

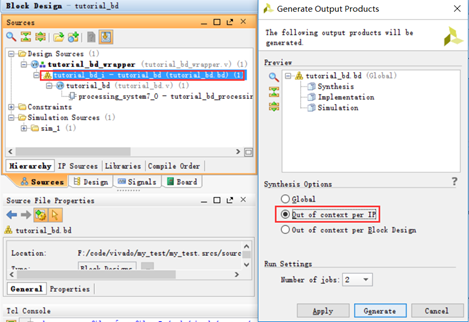

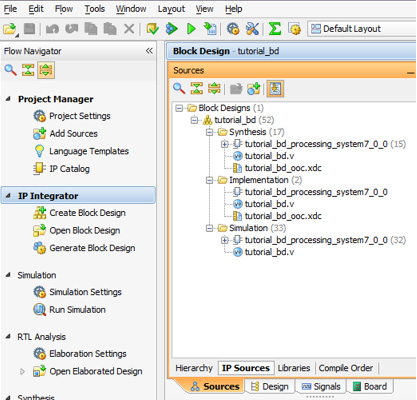

8. 在Design Sources视窗下,右键tutorial_bd_i - tutorial_bd(tutorial_bd.bd) 并选择Generate Output Products.

9. 生成成功后,点击OK确认。在IP Sources tab选项卡下面,可以看到所生成文件

步骤四、综合仿真、编译运行、生成二进制文件

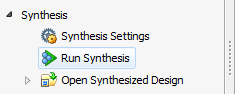

1. 在左侧Synthesis,下,点击Run Synthesis.

此时,右上角会一直有进度条运行,直至运行结束。

2. 在弹出框选择Run Implementation,注意进度条运行结束,点击OK。

3. 点击Generate Bitstream,注意进度条运行结束,点击OK.

至此,二进制文件生成。下一步将输出到hardware并运行软件Software Development Kit (SDK)。

步骤五、Exporting Hardware to SDK

1. 在vivado工具栏上,点击File > Export > Export Hardware,弹出如下界面,点击OK。

注意,仅当工程中有PL设计和二进制文件生成是,选项卡Include bitstream才被选中。

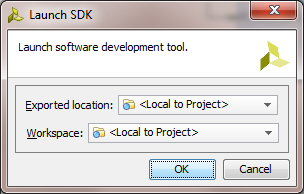

2. 选择File > Launch SDK.在弹出界面中选择默认,点击OK。

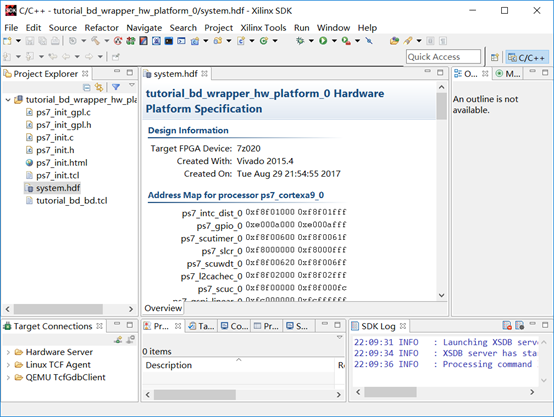

SDK软件打开,显示system.hdf文件,描述了处理器地址的映射。

3. 关闭SDK。

注:在Vivado中使用“Export Hardware”输出的硬件描述文件。都在工程目录下 “/<vivado project>/<project name>.sdk/<top module name>_hw_platform_0”文件夹下,可供petalinux使用。