将陆续上传本人写的新书《自己动手写处理器》(尚未出版),今天是第五篇,我尽量每周四篇

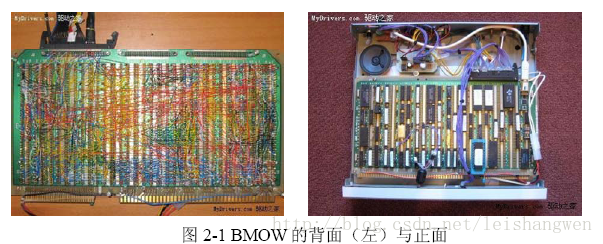

通过上一章的介绍,读者应该知道CPU内部有一些主要的电路,比方:译码电路、运算电路、控制电路。此外另一些寄存器等。这些电路怎么实现呢?当然能够通过一大堆分立的元器件实现,实际上在2008年,美国加州的游戏开发人士Steve Chamberlin就自己制造了一款8位CPU,耗时18个月,花费1000美元,总共使用了1253条线缆,如图2-1所看到的,Steve Chamberlin为它起了一个十分贴切的名字——BMOW(Big Mess of Wires)。

另一位叫Bill Buzbee的朋友也用200多块74系列的TTL集成电路纯手工制造了一款CPU。

上述事件仅仅是证明了使用分立元件实现CPU的可行性,但那并非实现CPU的好方法,本书是通过“代码 + FPGA”的方式实现CPU的,本章将对其原理进行解释,并对使用的编程语言Verilog HDL进行介绍。

2.1可编程逻辑器件概述

FPGA是可编程逻辑器件(PLD:Programmable Logic Device)的一种。

PLD是上世纪70年代发展起来的一种新型器件,它的应用和发展不仅简化了电路设计。减少了开发成本,提高了系统可靠性,并且给数字系统的设计方法带来了革命性的变化。截止到如今。出现了多种工艺、不同原理的PLD,例如以下。

- PLA(Programmable Logic Array)可编程逻辑阵列

- PAL(Programmable Array Logic)可编程阵列逻辑

- GAL(Generic Array Logic)通用阵列逻辑

- PROM(Programmable Read-Only Memory)可编程仅仅读存储器

- EPLD(Erasable Programmable Logic Device)可擦除可编程逻辑器件

- CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件

- FPGA(Field Programmable Gate Array)现场可编程门阵列

依照不同的内部结构能够将PLD器件分为例如以下两类。

1、基于乘积项(Product-Term)结构的PLD器件

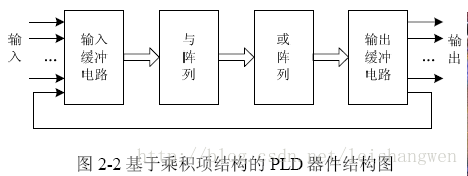

不论什么组合逻辑电路函数均可化为“与或”表达式,用“与门-或门”两级电路实现。而不论什么时序电路又都能够由组合电路加上存储元件(触发器)构成。因此。从原理上说。与或阵列加上触发器的结构就能够实现随意的数字逻辑电路。基于乘积项结构的PLD器件主要结构就是与或阵列,通过灵活配置的互连线,实现随意逻辑功能。其基本结构如图2-2所看到的。

基于乘积项结构的PLD器件由输入缓冲电路、与阵列、或阵列和输出缓冲电路四部分组成。“与阵列”和“或阵列”是主体。主要用来实现各种逻辑函数和逻辑功能;输入缓冲电路用于产生输入信号的原变量和反变量。并增强输入信号的驱动能力。输出缓冲电路主要用来对将要输出的信号进行处理,既能输出纯组合逻辑信号。也能输出时序逻辑信号。

PROM、PLA、PAL、GAL、EPLD和绝大部分CPLD器件都是採用乘积项(Product-Term)结构的PLD。内部基于与或阵列逻辑。这类器件多採用EEPROM或Flash工艺制作,掉电后不会丢失配置数据,器件规模一般小于5000门。

2、基于查找表(LUT:Look-Up Table)结构的PLD器件

基于与或阵列的PLD器件的规模不easy做得非常大,于是设计人员又开发出第二种可编程逻辑器件。即查找表结构。

其原理相似于ROM,物理结构基于静态存储器(SRAM:Static RAM)和数据选择器(MUX),通过查表方式实现函数功能。函数值放在SRAM中,SRAM的地址线即输入变量。不同的输入通过MUX找到对应的函数值并输出。N个输入项的逻辑函数能够由一个2N位容量的SRAM实现。

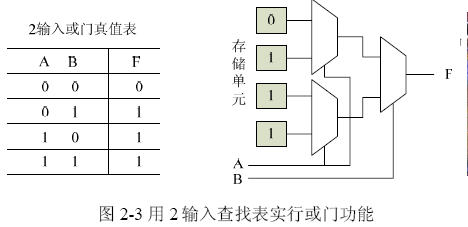

图2-3是用2输入查找表实现2输入或门的示意图。

2输入查找表中有4个存储单元,用来存储真值表中的4个值,输入变量A、B作为查找表中3个多路选择器的地址选择端,依据A、B值的组合从4个存储单元中选择一个作为查找表的输出,即实现了2输入或门的逻辑功能。

查找表结构的功能非常强,N个输入的查找表能够实现随意N个输入变量的组合逻辑函数。从理论上讲。仅仅要能够添加输入信号线和扩大存储器容量,用查找表就能够实现随意输入变量的函数。但在实际应用中。查找表的规模受技术和成本因素的限制。每添加一个输入变量,查找表SRAM的容量就要扩大一倍,SRAM的容量与输入变量数N的关系是2N倍。

8输入变量的查找表须要256b容量的SRAM,而16个输入变量的查找表则须要64Kb容量的SRAM。这个规模已无法忍受。实际上。FPGA器件查找表的输入变量一般不超过5个,多于5个输入变量的逻辑函数可由多个查找表通过组合或级联实现。

绝大多数FPGA器件都是基于SRAM查找表结构实现的。特点是集成度高(可实现百万逻辑门以上设计规模)、逻辑功能强,可实现大规模的数字系统设计和复杂的算法运算,但掉电后会丢失配置数据,需外挂非易失配置器件以存储配置数据,才干构成可独立执行的系统。

在FPGA内部一般还会集成很多其它的逻辑功能块,如存储器块、DSP块、硬件乘法器、数字锁相环等。用以满足数字信号处理、数字通信等应用的须要。

本书终于实现的实践版OpenMIPS处理器就将下载到FPGA上执行,使用的是Altera公司的EP2C35系列的FPGA,其具有33216个LE(Logic Element)。每个LE主要由一个4输入查找表和一个可编程的寄存器构成。

2.2 基于PLD的数字系统设计流程

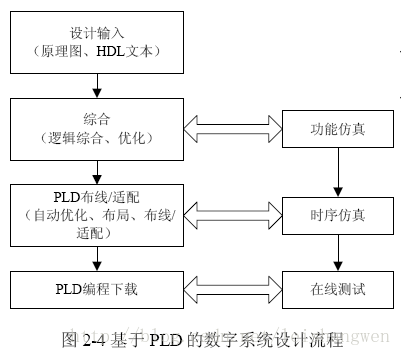

PLD不仅是技术的革新,也带来观念的革新、设计流程的革新。基于PLD的数字系统设计流程如图2-4所看到的。本节将分别介绍流程中的各个阶段。

2.2.1 设计输入

设计输入是将设计者所设计的电路以开发软件要求的某种形式表达出来,并输入到对应软件中的过程。

设计输入有多种方式。最经常使用的是原理图方式和HDL文本方式两种。

1、原理图输入

原理图(Schematic)是图形化的表达方式,使用元件符号和连线来描写叙述设计。

原理图输入对用户来说非常直观,尤其对于表现层次结构、模块化结构更为方便。适合描写叙述连接关系和接口关系,而描写叙述逻辑功能则比較繁琐。其要求设计工具提供必要的元件库或逻辑宏单元。假设输入的是较为复杂的逻辑或者元件库中不存在的模型。採用原理图输入的方式往往非常不方便,此外,原理图方式的设计可重用性、可移植性也差一些。

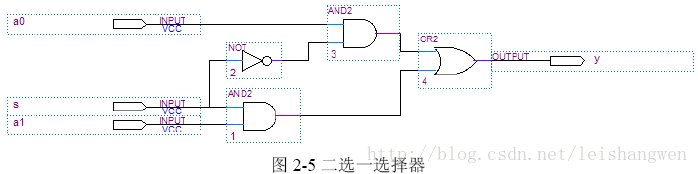

图2-5是使用原理图输入的二选一选择器的电路。有三个输入:a0、a1、s,一个输出y。当s为1时,y的值等于a1的值。当s为0时,y的值等于a0的值。

2、HDL文本输入

硬件描写叙述语言(HDL:Hardware Description Language)是一种用文本形式来描写叙述和设计电路的语言。设计者可利用HDL语言来描写叙述自己的设计。然后利用对应的工具进行综合。变为某种目标文件。最后下载到PLD器件,实现详细电路。眼下经常使用的HDL有VHDL、Verilog HDL等。

VHDL和Verilog HDL各有长处。能够进行算法级(Algorithm Levels)、寄存器传输级(RTL)、门级(Gate Levels)等各种层次的逻辑设计。也能够进行仿真验证、时序分析等。由于HDL语言的标准化。易于将设计移植到不同厂家的芯片中,信号參数也easy改变和改动。

此外,採用HDL进行设计还具有工艺无关性,使得设计人员在功能设计、逻辑验证阶段能够不必过多考虑门级及工艺实现的详细细节,仅仅需依据系统设计的要求,施加不同的约束条件。就可以设计出实际的电路。例如以下是使用Verilog HDL实现的二选一选择器的代码。

module mux2(a0, a1, s, y);

input s, a0, a1;

output y;

assign y = s ? a1 : a0;

endmodule

本书使用Verilog HDL实现OpenMIPS处理器。

2.2.2 综合

综合(Synthesis)是将较高级抽象层次的设计描写叙述自己主动转化为较低层次描写叙述的过程。有下面几种综合形式。

- 将算法表示、行为描写叙述转换到寄存器传输级(RTL)。即从行为描写叙述到结构描写叙述。

- 将RTL级描写叙述转换到逻辑门级。称为逻辑综合。

- 将逻辑门表示转换到PLD器件的配置网表表示,有了配置网表就可完毕基于PLD器件的系统实现。

综合器就是能够自己主动实现上述转换的软件工具。其能够将原理图或HDL语言表达、描写叙述的电路编译成由与或阵列、RAM、触发器、寄存器等逻辑单元组成的电路网表。

2.2.3 布局布线

布局布线能够理解为将综合生成的电路网表映射到详细的目标PLD器件,并产生终于可下载文件的过程。

布局布线将综合后的电路网表针对某一详细的目标PLD器件进行逻辑映射。把整个设计分为多个适合PLD器件内部逻辑资源实现的逻辑小块,并依据用户的设定在速度和面积之间做出选择或折中。

当中布局是将已切割的逻辑小块放到PLD器件内部逻辑资源的详细位置,并使它们易于连线;布线则是利用PLD器件的布线资源完毕各功能块之间、反馈信号之间的连接。

布局布线完毕后产生例如以下一些关键的文件。

1、芯片资源耗用的情况报告。

2、产生延时网表结构。以便于进行精确的时序仿真,能比較精确的预測未来芯片的实际性能。

3、器件编程文件。如用于CPLD编程的JEDEC、POF等格式的文件;用于FPGA配置的SOF、JAM、BIT等格式的文件。

2.2.4 下载

把布局布线过程中产生的器件编程文件放入PLD的过程称为下载。通常将对CPLD器件的下载称为编程,将对FPGA器件的下载称为配置(Configuration)。下载后,PLD内部的与或门(对FPGA而言就是查找表)会依照编程文件的要求变化,从而实现了设计的电路。

2.2.5 仿真

从图2-4中可发现当中有仿真环节。

仿真(Simulation)也称为模拟,是对所设计电路的功能进行检验。

用户能够在设计过程中对整个系统和各个模块进行仿真,即在计算机上用软件验证功能是否正确,各部分的时序配合是否准确。假设有问题能够随时进行改动,从而避免了逻辑错误。规模越大的设计,越须要进行仿真。

仿真包括功能仿真和时序仿真。不考虑信号时延等因素的仿真,称为功能仿真,又叫前仿真;时序仿真又称后仿真,它是在选择详细器件并完毕布局布线后进行的包括时延的仿真。由于不同器件的内部时延不一样。不同的布局、布线方案也会影响时延,因此在设计实现中,对网络和逻辑块进行时序仿真,分析定时关系,预计设计性能是非常必要的。

本书实现的教学版OpenMIPS处理器就主要通过仿真来验证其是否实现正确,仅仅有实践版OpenMIPS才配置到详细的FPGA芯片中。

2.2.6 工具介绍

在基于PLD的数字系统设计流程的每个阶段都有对应的工具支持,有些工具是集成的,能够完毕整个设计流程的各个阶段。有些工具是专门针对某一设计阶段的。

本书在设计实现OpenMIPS处理器时使用的工具例如以下。

- 设计输入工具:UltraEdit

- 仿真工具:ModelSim

- 集成工具:QuartusII

由于实践版OpenMIPS是下载到Altera公司的FPGA芯片中,所以集成工具使用的是Altera公司的QuartusII。

一般而言,集成工具最好选择目标PLD芯片厂商提供的工具,由于厂商的工具会针对自己器件的工艺特点做优化设计。从而提高资源利用率、减少功耗、改善性能。

未完待续!