一 、前言

本文设计思想采用明德扬至简设计法。VGA是最常见的视频显示接口,时序也较为简单。本文从利用显示屏通过VGA方式显示测试图案及静态图片着手带大家接触图像显示应用,算是为后续VGA显示摄像头采集图像以及HDMI高清数字显示方式打个基础。

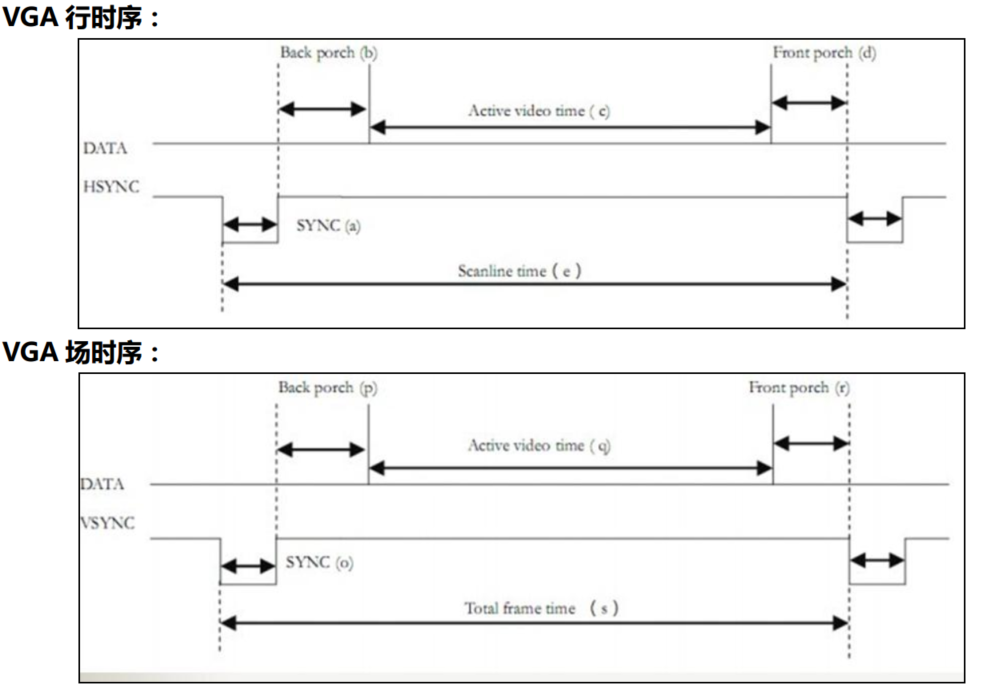

二、VGA显示原理

关于VGA的详细解释可查看参考文献1,这里主要讲解下根据VGA的分辨率计算时钟频率的方式。以本文使用到的1024*768@60HZ为例。

一帧图像显示周期为Tv,在这段时间内VGA需要扫描806行,每行1344个点。所以每个点的持续周期为:Ts=Tv/(n*m),故时钟频率:fs = n*m*fv=806*1344*60=65MHz。因此设计下来其实非常简单,PLL产生65MHz工作时钟信号,利用两个计数器分别计数行列值,之后根据计数器数值产生行场同步信号以及相应的RGB图像数据即可。有一点需要注意:VGA显示标准规定行场同步脉冲均为负脉冲,意思是只有同步脉冲阶段拉低,其他时刻为高电平。

三、静态图片显示

VGA显示基本原理和设计方式确定后,显示图片也不是什么难事。可以将图片以.coe形式保存在FPGA内部BRAM中,通过VGA接口模块循环读取RAM数据方式来显示图片。FPGA片内BRAM的存储容量一般在kbit量级,存储640*480*24bit真彩色图像捉襟见肘,因此这里仅显示320*240*16bit图像用于测试。把图片格式设定为.coe文件的方法:一是可以利用些小的软件工具,此处先用img2Lcd软件将图片调整为合适的分辨率,再用BMP2Mif软件生成.coe文件初始化BMG IP核(见参考文献2);第二就是自己写一段软件脚本来转换。

测试需求:VGA接口以1024*768分辨率,60Hz帧频,在显示屏中央位置显示一幅320*240图片,其他位置左右各一半分别显示白色和红色。

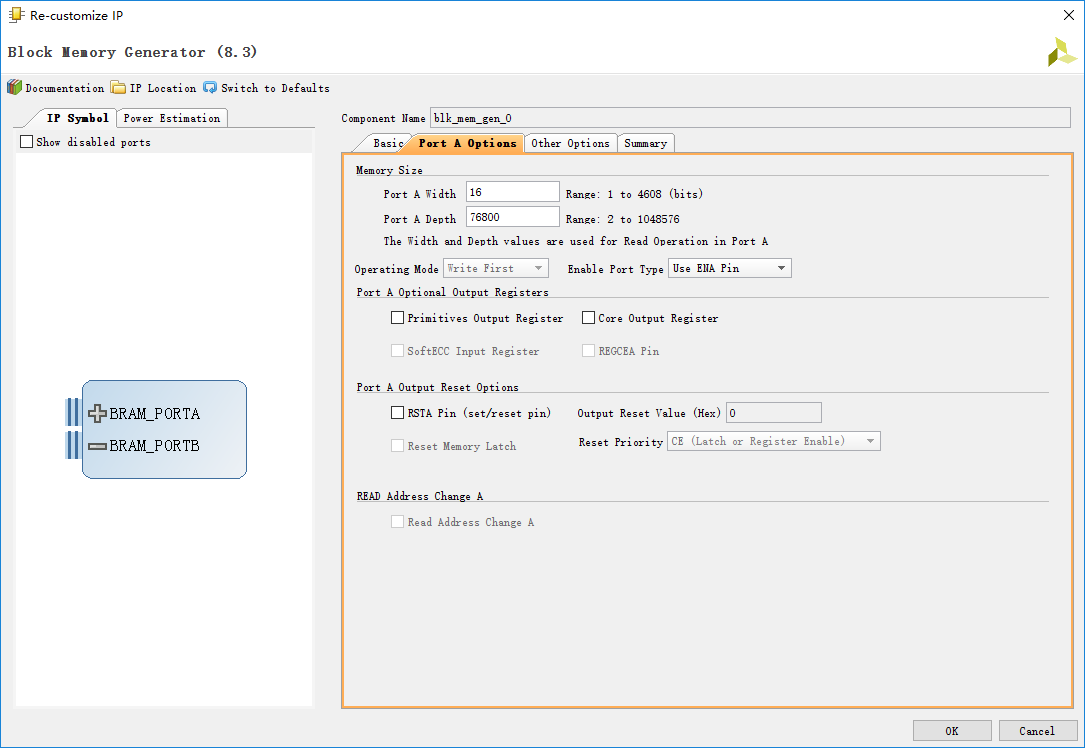

BMG IP核配置:

第一页选择单口ROM模式,其他保持默认。主要第二页的位宽和深度设置正确,另外取消掉输出寄存器选择匹配时序。

四、显示硬件方案

大多数VGA显示采用电阻网络分压代替DA过程,这种方案成本较低,能满足大多数显示需求。当对分辨率要求较高时,采用专用显示芯片来完成R G B三路同步数模转换,本文采用ADI公司的ADV7123芯片,内含有三路10位DAC,最高支持1080p@60Hz图像输出。硬件中将每路低两位拉低,仅提供高8位接口可满足8*8*8 = 24bit真彩色显示需求。上升沿采样数据,为方便处理和代码规范,FPGA逻辑在PLL时钟上升沿驱动,输出显示芯片工作采样时钟为PLL产生时钟信号取反,如此可保证满足显示芯片建立保持时间需求。

五、逻辑代码设计

VGA显示接口代码如下:

1 `timescale 1ns / 1ps 2 3 module vga_interface#( 4 parameter DATA_W = 8) 5 ( 6 input clk,//65MHz 7 input rst_n, 8 9 output vga_clk, 10 output reg vga_en, 11 12 //input [DATA_W-1:0] din_r, 13 //input [DATA_W-1:0] din_g, 14 //input [DATA_W-1:0] din_b, 15 output [DATA_W-1:0] vga_r, 16 output [DATA_W-1:0] vga_g, 17 output [DATA_W-1:0] vga_b, 18 output reg vga_hs, 19 output reg vga_vs 20 ); 21 22 /*********************************参数******************************************/ 23 //VGA:1280*768@60HZ 24 //行参数 25 localparam H_A = 136, //同步脉冲 26 H_B = 160, //显示后沿 27 H_C = 1024, //显示时段 28 H_D = 24; //显示前沿 29 //场参数 30 localparam V_A = 6, //同步脉冲 31 V_B = 29, //显示后沿 32 V_C = 768, //显示时段 33 V_D = 3; //显示前沿 34 35 //有效区域边界 36 localparam X0 = H_A+H_B, //136+160=296 37 X1 = H_A+H_B+H_C, //136+160+1024=1320 38 Y0 = V_A+V_B, //6+29=35 39 Y1 = V_A+V_B+V_C; //6+29+768=803 40 41 localparam COL_NUM = H_A+H_B+H_C+H_D,//1344 42 ROW_NUM = V_A+V_B+V_C+V_D;//806 43 44 //显示中心位置 45 localparam X_CENTER = (X0+X1)/2,//808 46 Y_CENTER = (Y0+Y1)/2;//419 47 48 //显示图片分辨率及位置 49 localparam PIC_H = 320, 50 PIC_V = 240; 51 52 localparam PIC_H_LB = X_CENTER-PIC_H/2, 53 PIC_H_RB = X_CENTER+PIC_H/2, 54 PIC_V_UB = Y_CENTER-PIC_V/2, 55 PIC_V_DB = Y_CENTER+PIC_V/2; 56 57 /*********************************信号定义******************************************/ 58 reg [ (12-1):0] cnt_hs ; 59 wire add_cnt_hs ; 60 wire end_cnt_hs ; 61 reg [ (12-1):0] cnt_vs ; 62 wire add_cnt_vs ; 63 wire end_cnt_vs ; 64 wire valid_area; 65 wire left_half; 66 wire picture_area; 67 reg [DATA_W-1:0] r_reg,g_reg,b_reg; 68 69 wire ena; 70 wire [15:0] douta; 71 reg [ (17-1):0] cnt_addr ; 72 wire add_cnt_addr ; 73 wire end_cnt_addr ; 74 wire [16:0] addra; 75 reg ram_vld; 76 /*********************************计数器******************************************/ 77 78 always @(posedge clk or negedge rst_n) begin 79 if (rst_n==0) begin 80 cnt_hs <= 0; 81 end 82 else if(add_cnt_hs) begin 83 if(end_cnt_hs) 84 cnt_hs <= 0; 85 else 86 cnt_hs <= cnt_hs+1 ; 87 end 88 end 89 90 assign add_cnt_hs = 1; 91 assign end_cnt_hs = add_cnt_hs && cnt_hs == (COL_NUM)-1 ; 92 93 always @(posedge clk or negedge rst_n) begin 94 if (rst_n==0) begin 95 cnt_vs <= 0; 96 end 97 else if(add_cnt_vs) begin 98 if(end_cnt_vs) 99 cnt_vs <= 0; 100 else 101 cnt_vs <= cnt_vs+1 ; 102 end 103 end 104 assign add_cnt_vs = (end_cnt_hs); 105 assign end_cnt_vs = add_cnt_vs && cnt_vs == (ROW_NUM)-1 ; 106 107 108 /*********************************BRAM相关信号******************************************/ 109 //BRAM读取地址计数器 110 always @(posedge clk or negedge rst_n) begin 111 if (rst_n==0) begin 112 cnt_addr <= 0; 113 end 114 else if(add_cnt_addr) begin 115 if(end_cnt_addr) 116 cnt_addr <= 0; 117 else 118 cnt_addr <= cnt_addr+1 ; 119 end 120 end 121 122 assign add_cnt_addr = (ena); 123 assign end_cnt_addr = add_cnt_addr && cnt_addr == 320*240 -1 ; 124 125 assign addra = cnt_addr; 126 assign ena = picture_area; 127 128 //BRAM数据有效指示 129 always @(posedge clk or negedge rst_n)begin 130 if(rst_n==1'b0)begin 131 ram_vld <= 0; 132 end 133 else begin 134 ram_vld <= ena; 135 end 136 end 137 /*********************************VGA输出信号******************************************/ 138 //行场同步信号 139 always @(posedge clk or negedge rst_n)begin 140 if(rst_n==1'b0)begin 141 vga_hs <= 1; 142 end 143 else if(add_cnt_hs && cnt_hs == H_A-1)begin 144 vga_hs <= 1; 145 end 146 else if(end_cnt_hs) 147 vga_hs <= 0; 148 end 149 150 always @(posedge clk or negedge rst_n)begin 151 if(rst_n==1'b0)begin 152 vga_vs <= 1; 153 end 154 else if(add_cnt_vs && cnt_vs == V_A-1)begin 155 vga_vs <= 1; 156 end 157 else if(end_cnt_vs) 158 vga_vs <= 0; 159 end 160 161 //R G B寄存器信号 162 always @(posedge clk or negedge rst_n)begin 163 if(rst_n==1'b0)begin 164 r_reg <= 0; 165 g_reg <= 0; 166 b_reg <= 0; 167 end 168 else if(valid_area && !picture_area)begin 169 if(left_half)begin //彩条测试 左半屏幕显示白色 170 r_reg <= 8'b1111_1111; 171 g_reg <= 8'b1111_1111; 172 b_reg <= 8'b1111_1111; 173 end 174 else begin //右半屏幕显示红色 175 r_reg <= 8'b1111_1111; 176 g_reg <= 0; 177 b_reg <= 0; 178 end 179 end 180 else begin//无效区域显示黑色 181 r_reg <= 0; 182 g_reg <= 0; 183 b_reg <= 0; 184 end 185 end 186 187 assign valid_area = cnt_hs >= X0 && cnt_hs < X1 && cnt_vs >= Y0 && cnt_vs < Y1; 188 assign left_half = cnt_hs >= X0 && cnt_hs < X_CENTER; 189 assign picture_area = cnt_hs >= PIC_H_LB && cnt_hs < PIC_H_RB 190 && cnt_vs >= PIC_V_UB && cnt_vs < PIC_V_DB; 191 192 assign vga_r = ram_vld ? {douta[15:11],3'b0} : r_reg;//5bit 193 assign vga_g = ram_vld ? {douta[10:5],2'b0} : g_reg;//6bit 194 assign vga_b = ram_vld ? {douta[4:0],3'b0} : b_reg;//5bit 195 196 //输出控制信号 197 assign vga_clk = ~clk; 198 199 always @(posedge clk or negedge rst_n)begin 200 if(rst_n==1'b0)begin 201 vga_en <= 0; 202 end 203 else if(valid_area)begin 204 vga_en <= 1; 205 end 206 else 207 vga_en <= 0; 208 end 209 210 /*********************************子模块例化 BRAM******************************************/ 211 212 blk_mem_gen_0 bram ( 213 .clka(clk), // input wire clka 214 .ena(ena), // input wire ena 215 .addra(addra), // input wire [16 : 0] addra 216 .douta(douta) // output wire [15 : 0] douta 217 ); 218 219 endmodule

这里VGA接口代码包含了显示内容,在实际应用中要去掉显示部分逻辑和BRAM的例化,添加用户侧接口及逻辑。测试工程顶层:

1 `timescale 1ns / 1ps 2 3 module vga_test_top( 4 input sys_clk_p, 5 input sys_clk_n, 6 input rst_n, 7 8 output vga_hs, 9 output vga_vs, 10 output vga_clk, 11 output vga_en, 12 output [8-1:0] vga_r, 13 output [8-1:0] vga_g, 14 output [8-1:0] vga_b 15 ); 16 17 wire clk; 18 wire sys_clk_ibufg; 19 wire locked; 20 21 IBUFGDS # 22 ( 23 .DIFF_TERM ("FALSE"), 24 .IBUF_LOW_PWR ("FALSE") 25 ) 26 u_ibufg_sys_clk 27 ( 28 .I (sys_clk_p), 29 .IB (sys_clk_n), 30 .O (sys_clk_ibufg) 31 ); 32 33 clk_wiz_0 pll 34 ( 35 // Clock out ports 36 .clk_out1(clk), // output clk_out1 37 // Status and control signals 38 .resetn(rst_n), // input resetn 39 .locked(locked), // output locked 40 // Clock in ports 41 .clk_in1(sys_clk_ibufg)); // input clk_in1 42 43 44 vga_interface#(.DATA_W(8)) 45 vga_interface 46 ( 47 .clk (clk) ,//65MHz 48 .rst_n (rst_n) , 49 .vga_clk (vga_clk) , 50 .vga_en (vga_en) , 51 .vga_r (vga_r) , 52 .vga_g (vga_g) , 53 .vga_b (vga_b) , 54 .vga_hs (vga_hs) , 55 .vga_vs (vga_vs) 56 ); 57 58 59 endmodule

六、仿真及板级测试

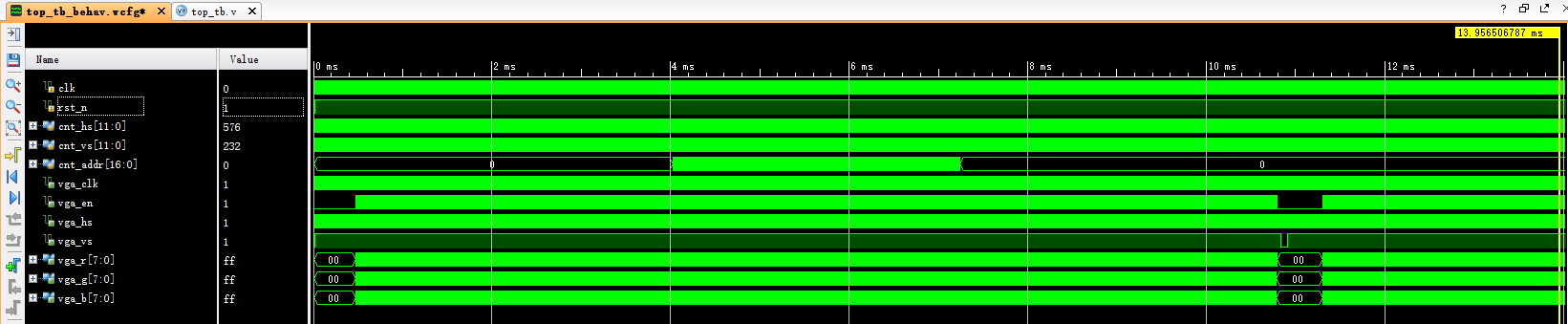

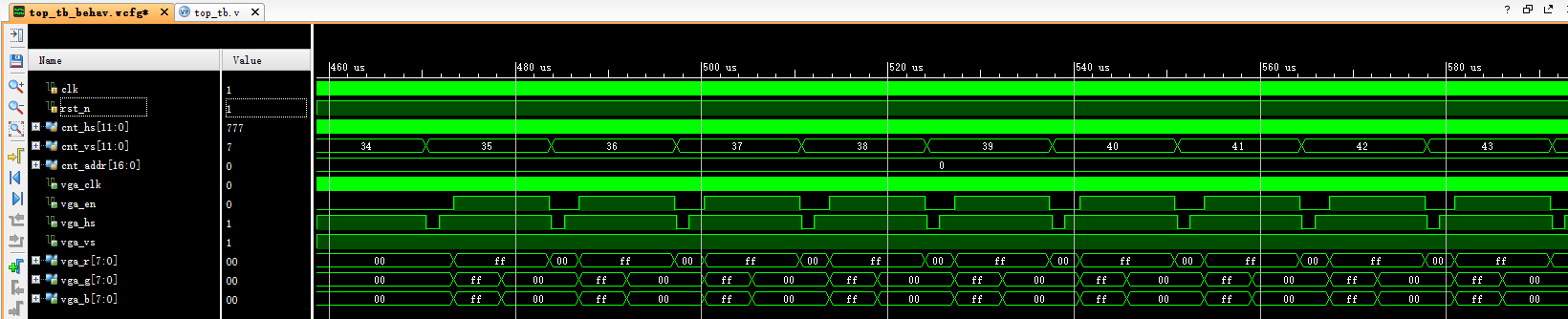

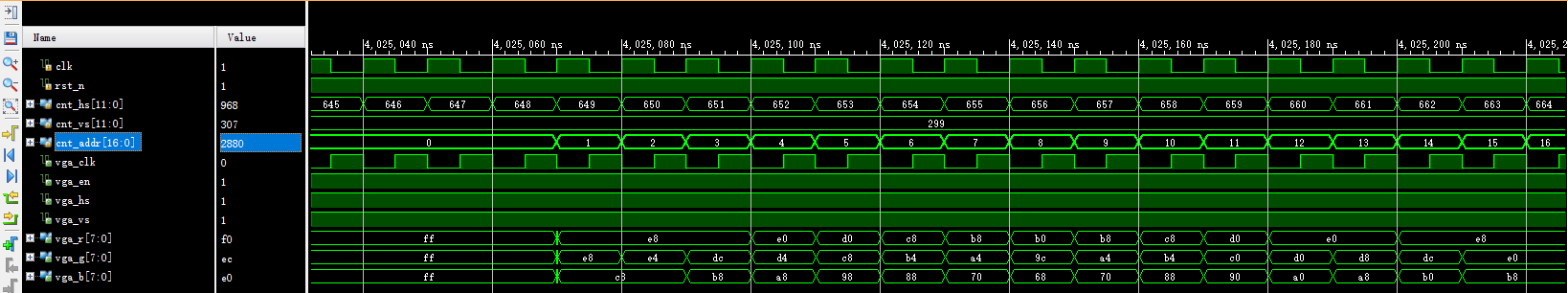

为了方便仿真,只将vga_interface作为uut。查看行为仿真波形:

可见行场计数器及同步脉冲按照预期工作,在显示图片区域地址计数器递增。现在我们看看实际上板后的显示效果:

和原始图片对比下

由于原始图片是24位真彩图,且在VGA显示接口模块中进行了R G B低位填充导致些许失真,不过整体显示正确。

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

参考文献:

1 [笔记]VGA时序及其原理 - LiangXuan - 博客园 https://www.cnblogs.com/spartan/archive/2011/08/16/2140546.html

2 【原创】bmp转mif、coe或hex软件发布及使用介绍-crazybird-电子技术应用-AET-北大中文核心期刊-最丰富的电子设计资源平台 http://blog.chinaaet.com/crazybird/p/5100000224