一、实验硬软件环境:

- EDA软件:Vivado2019

- 实验开发板:Basys3 FPGA套件

二、实验内容:

实现如下电路功能:当开关开启,灯泡按1s的间隔闪烁;开关关闭,则灯泡关闭。使用实验板上的按键模拟开关,led模拟灯泡,时钟使用实验板提供的clk。参考实验板的管脚文件编写约束文件。

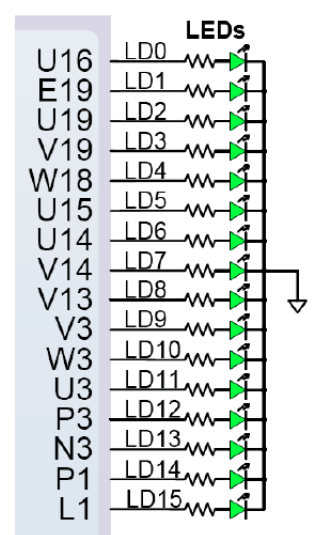

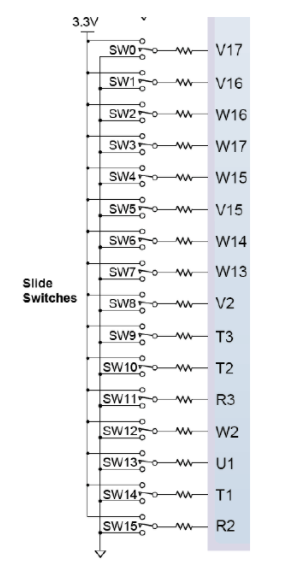

注意,LED部分的电路图如左图所示,当FPGA输出为高电平时,相应的LED点亮;否则,LED熄灭。拨码开关的电路如右图所示,当开关打到下档时,表示FPGA的输入为低电平。

三、具体实现

- 思路分析:开发板的晶振为100Mhz,则其周期为10ns,初值为0的计数器自加1到100,000,000时为1s。

- 设计源码:

1 module led( 2 input switch, 3 input clk, 4 output reg led, 5 ); 6 7 reg [28:0] count; 8 9 always @(posedge clk) 10 begin 11 if(!switch) 12 begin 13 count <= 0; 14 led <= 0; 15 end 16 else 17 begin 18 if(count == 29'd100_000_000) 19 begin 20 count <= 0; 21 led <= ~led; 22 end 23 else 24 begin 25 count <= count + 1; 26 led <= led; 27 end 28 end 29 end

- 仿真代码

1 `timescale 1ns / 1ps 2 3 module led_tb; 4 reg switch; 5 reg clk; 6 wire led; 7 8 led uut( 9 .switch(switch), 10 .clk(clk), 11 .led(led) 12 ); 13 14 initial 15 begin 16 switch = 0; 17 clk = 0; 18 19 #100 switch = 1; 20 #100; 21 end 22 23 always #50 clk = ~clk; 24 endmodule

- 约束文件

1 set_property PACKAGE_PIN V17 [get_ports switch] 2 set_property IOSTANDARD LVCMOS33 [get_ports switch] 3 set_property PACKAGE_PIN U16 [get_ports led] 4 set_property IOSTANDARD LVCMOS33 [get_ports led] 5 set_property PACKAGE_PIN W5 [get_ports clk] 6 set_property IOSTANDARD LVCMOS33 [get_ports clk]

- 总结:时序逻辑使用 always #50 clk = ~clk 这条语句来产生一个不断重复的周期为100个的时钟信号clk。