此设计的结构包括:1.移位寄存器链,n阶的有n-1个寄存器。

2.第一次累加部分。由fir滤波系数对称可得到对称的寄存器相加可以减小电路规模,所以第一次累加很有必要。

3,锁存并移位部分。此部分是为了通过移出lut地址,通过给出lut地址即可得到lut输出。

4,lut部分,该部分实现的主要功能是输出不同地址情况下的结果。

5,二次累加部分。该部分是将每一位卷积得到的结果加权累加,需要注意的是,由于是采用补码运算,最高位加权后应该是被减去而不是被加上。

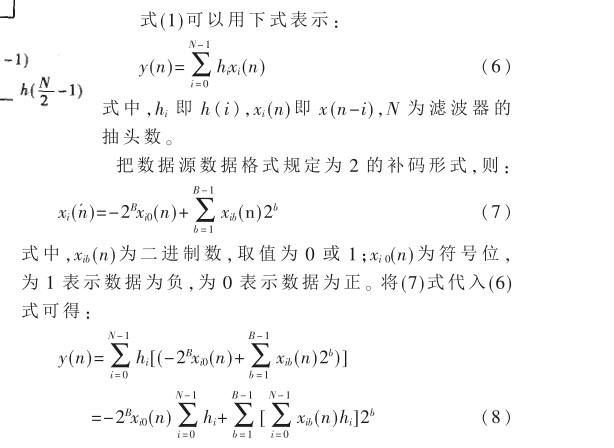

分布式滤波器的原理如下

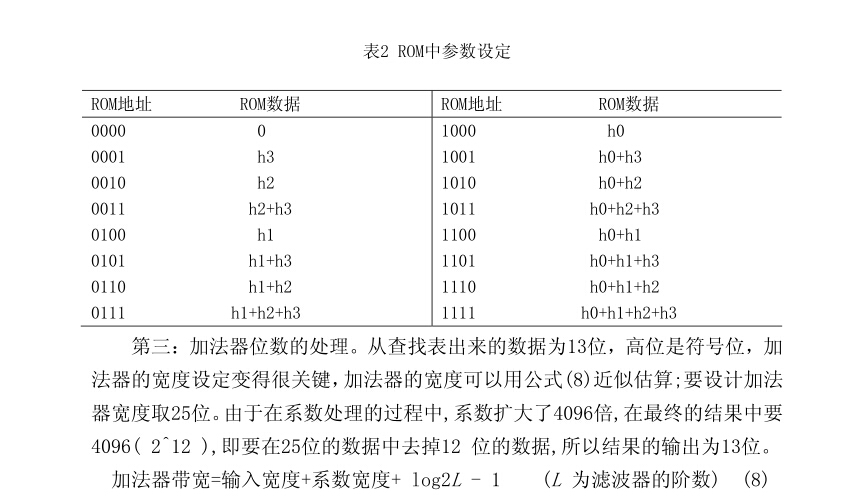

查找表的实现可参考下表

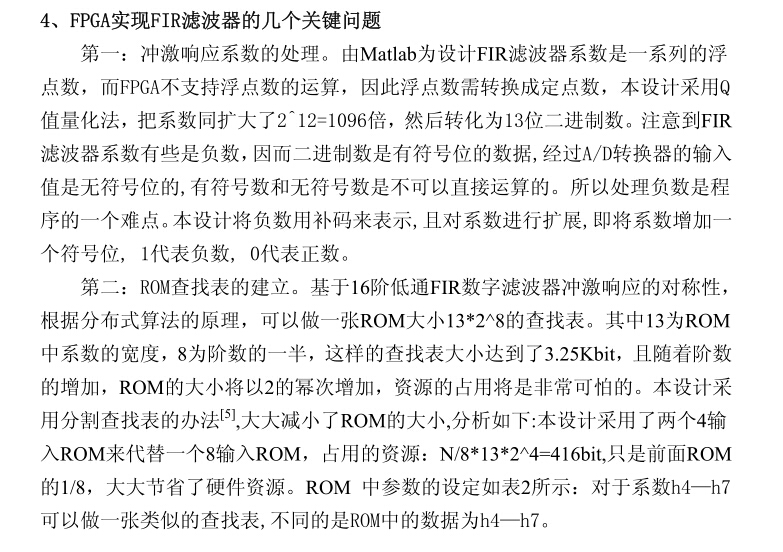

实现过程的几个关键问题:

这次设计就在加法器带宽处产生问题,带宽不够,发现出来的波形顶部挪到低下去了,通过看中间数据发现是数据位宽不够造成的,根据这个公式得到的加法器带宽刚好能满足设计需求。