[施工编辑中。。。]

1. 什么是TDR?

TDR = Time Domain Reflectometry

时域反射计TDR用来测量信号在通过某类传输环境传导时引起的反射,如电路板轨迹、电缆、连接器等等。

2. TDR测试原理

2.1 传统时域反射计工作原理

图1是传统时域反射计的工作原理图。由三部分组成:

- 快沿信号发生器。典型发射信号的特征是: 幅度200mV, 上升时间35ps, 频率250KHz的方波。

- 采样示波器。

- 探头系统。

图1 - 传统时域反射计工作原理图

原理: 信号在某一传输路径传输,当传输路径中发生阻抗变化时,一部分信号会被反射,另一部分信号会继续沿传输路径传输。TDR是通过测量反射波的电压幅度,从而计算出阻抗的变化;同时,只要测量出反射点到信号输出点的时间值,就可以计算出传输路径中阻抗变化点的位置。

TDR 显示了在沿着一条传输线传播快速阶跃信号时返回的电压波形。波形结果是入射阶跃和阶跃遇到阻抗偏差时产生的反射的组合。阶跃信号源的上升时间决定分辨阻抗不连续点的能力;高速采样电路决定阻抗变化位置的准确性。

图2 - 时域反射计测试电压波形与传输线对应关系

TDR测量的数学基础很简单,但十分重要。从本质上看, TDR 测量基于一系列阻抗比率。大多数 TDR 测量将在内部执行必要的比率计算,显示一个数字结果。TDR测量以反射系数( (rho)表示。系数是反射的脉冲幅度与入射脉冲幅度之比:

对固定终端ZL,还可以用传输线特性阻抗Z0和负载阻抗ZL 表示:

2.2 网络分析仪测试方案

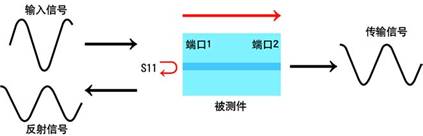

网络分析仪VNA是测量被测件DUT频率响应的仪器,测量时为被测件输入一个正弦波激励信号,然后通过计算输入信号与传输信号S21或反射信号S11之间的矢量幅度比得到测量结果。

VNA测试的频率响应特性

频域和时域之间的关系可以通过傅里叶理论来描述。通过对使用VNA获得的反射和传输频率响应特性进行傅里叶逆变换,可以获得时域上的冲激响应。这和在TDR示波器上观察到的响应特性是一样的。由于积分计算非常耗时,因此实际上使用的方法是在频域中根据傅里叶变换的卷积原理进行计算-- 把输入信号的傅里叶变换和被测件的频率响应特性进行卷积,然后对结果实施傅里叶逆变换。

从傅里叶逆变换推导的阶跃响应特性和冲激响应特性间的关系

3. TDR时域波形分析

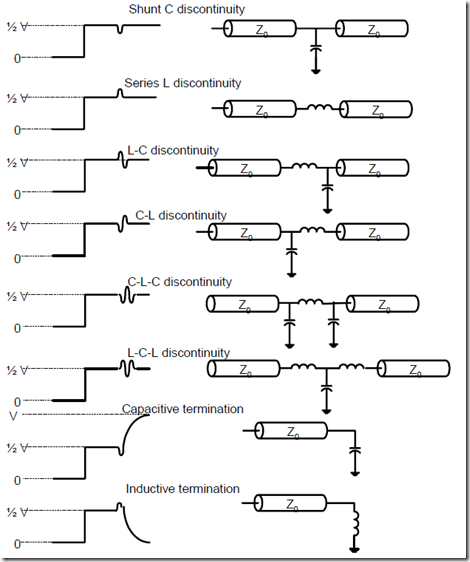

对于有经验的测试工程师来说,通过TDR时域波形可以直观地知道传输线路径上阻抗突变的因素。下图中列出了常见的一些情况。

扩展阅读

1. TDR分辨率因素

TDR 测量可以有效地考察电路阻抗和信号完整性。但是,并不能以“一刀切”的方式创建TDR解决方案。许多因素影响着TDR 系统可以分辨的最小的不连续点的距离间隔的能力。

如果 TDR 系统的分辨率不足,那么间隔很小或间隔紧密的不连续点可能会平滑地转化成波形中的一个畸变。这种效应不仅可能会隐藏某些不连续点,而且可能会导致阻抗读数不精确。上升时间、建立时间和脉冲畸变可能会明显影响 TDR 系统的分辨率。

(1). 上升时间

阻抗不连续点的表现之一是上升时间等于或更可能长于(慢于)入射阶跃。电路中任意两个不连续点之间的物理间隔决定了在TDR波形上彼此之间相对反射位置的接近程度。如果它们的之间的距离不到系统上升时间的一半,那么测量仪器可能区分不出两个相邻的不连续点。下面的公式说明了这一概念。

(2). 提前畸变

这是在主要入射阶跃之前发生的畸变,提前畸变特别讨厌,因为它们到达不连续点,在主要阶跃到达之前开始产生反射。这些早期反射隐藏了间隔紧密的不连续点,降低了分辨率。

(3). 建立畸变

稳定畸变是指在入射阶跃之后发生的畸变,如瞬变 ,这将导致反射中发生相应的畸变。这些畸变很难与测试的设备(DUT)不连续性导致的反射区分开来。注意, TDR 仪器阶跃发生器中的畸变和取样器阶跃响应中的畸变产生的影响几乎完全相同。

2. TDR精度因素

许多因素影响着 TDR 测量的精度,包括 TDR 系统的阶跃响应、互连反射和 DUT 损耗、阶跃幅度精度、基线校正和测量中使用的参考阻抗的精度(Z0 )。

(1). 参考阻抗

所有 TDR 测量都是相对的,它们通过比较反射的幅度与入射幅度得出。现代 TDR 仪器执行所有计算,比较入射幅度和反射幅度,以rho或ohm直接表示结果。但是,这一过程仍取决于参考阻抗的精度 (Z0 )。

(2). 阶跃幅度和基线校正

一般来说,现代TDR 仪器测量和 / 或校准入射阶跃幅度,根据已知的阶跃幅度和基线电平,计算毫rho和ohm。通过在取样模块中置入一条已知空气线,TDS8000示波器向前推进了一步。之后它会定期监视基线和入射阶跃幅度。这样,可以自动补偿系统,允许即使在阶跃幅度偏置漂移的情况下实现可重复性非常强的测量。

(3). 入射阶跃畸变

入射阶跃畸变导致的最明显问题是,如果在相对于测量的线路很短的时间内脉冲没有稳定,那么则不能精确地测量反射阶跃幅度。这类错误只对阻抗明显不同于50欧姆的 DUT 阻抗特别重要。在这种情况下,精度在很大程度上取决于反射阶跃幅度精度。阻抗越靠近50欧姆,精度越取决于反射阻抗,因为反射很小。

可能导致问题的第二类畸变是阶跃之前的“脚”或前冲。如果 DUT 在末端存在开路,那么阶跃的这一部分将在看到阶跃明显上升边沿之前反映开路。这将在接近测量线路的末端导致错误。

低频阶跃畸变会引起更加错综复杂的效应。这些畸变可以在轨迹中显示为一个斜坡,甚至使用一个完美的50欧姆端接代替 DUT。如果没有在测量参考阻抗的同一时间内测量 DUT,那么这会导致 50 欧姆电平偏置。

(4). 噪声

在测量小的阻抗偏差时,随机噪声会成为一个重大的误码源。幸运的是,现代仪器可以执行信号加权平均,降低随机噪声的影响。许多仪器的缺点是加权平均可能会明显降慢处理速度,特别是在显示自动测量结果时。 TDS8000 示波器内置多部处理器,可以分担处理工作负载,解决了这个问题。

(5). 互连精度和反射

如果使用的探头电缆很长,在测量相对于电缆末端的 DUT阻抗时要非常谨慎,以降低电缆损耗的影响。但是,在这种情况下,电缆阻抗直接影响着测量精度。参考电平将移动电缆的 rho ((cable ),DUT 上的入射阶跃幅度将为(1- |( cable |)。为实现最大精度,可以测量这些参数,计算其阻抗。

互联元器件和探头到 DUT 接口反射也会导致问题。探头接口可能会产生大的电感反射,在进行精确测量前必须稳定电感反射。尽量缩短探头触点和地线的长度非常重要,以使这些问题达到最小。

(6). 电缆损耗

测试设置中的电缆损耗可能会导致多个问题。尽管可能会同时发生导线损耗和绝缘体损耗,但导线损耗通常占大多数。导线损耗是由电缆中金属导线的有限阻抗导致的,由于集肤效应,导线损耗会随着频率一起提高。在进一步考察电缆时,这一递增串联阻抗结果的阻抗值会明显提高。因此,在使用长的测试电缆时,DUT阻抗看上去要高于实际值。

第二个问题是入射脉冲到达电缆末端的时间会使其上升时间和稳定时间降级。这影响着分辨率和精度,因为入射阶跃的有效幅度不同于预期幅度。在DUT 阻抗接近 50 欧姆时,这种阻抗不精确不会引起大的误差,但是对较大或较小的阻抗,误差可能会很大。

通过使用延长电缆,使取样头更靠近DUT,可以使导线损耗达到最小。如果不可能使用这种方法,那么则可以采用比较反射技术之类的方法,帮助解决问题。该技术的实例如下:

- 用已知标准阻抗的空气线代替DUT。测量在使用这条空气线时的实际阻抗读数。这种测量提供了一个可以用于下一步骤中的偏置值。这个偏置值量化了在DUT 之前互连单元的影响。

- 在 DUT 本身的所有后续测量中加上或减去偏置值。

- TDS8000示波器等支持TDR功能的仪器具有杰出的线性能力,保证了在使用标准空气线或DUT时,阶跃信号经历完全相同的信号源、互连和取样器不完整性。

比较反射方法大大改善了 r 和阻抗测量的绝对精度。

(7). 控制上升时间

尽管在许多情况下,用户希望最快的上升时间,但在某些情况下,极快的上升时间在 TDR 测量中会给出误导性结果。例如,在使用上升时间为35 ps的系统测试电路板上微带的阻抗时,会提供完美的分辨率。但是,即使当前使用的最高速的逻辑家族也不能一开始就与 35 ps 的 TDR 阶跃上升时间相匹配。典型的高速逻辑家族如 ECL,输出上升时间在 200 ps 到 2 ns 之间。小的不连续性,如微带中的短线或锐角转角,会变得非常明显,在35 ps上升时间时可能会产生大的反射。上升时间为1 ns的ECL栅在实际运行中驱动的相同传输线可能会产生非常小的可以忽略不计的反射。

参考文献: