Read "Zynq-7000 All programmable Soc"

1.Table of Contents

首先是目录,可以看到是标准的总分结构。开头介绍了Zynq的各种功能,后面再逐个解释。

2.introduction

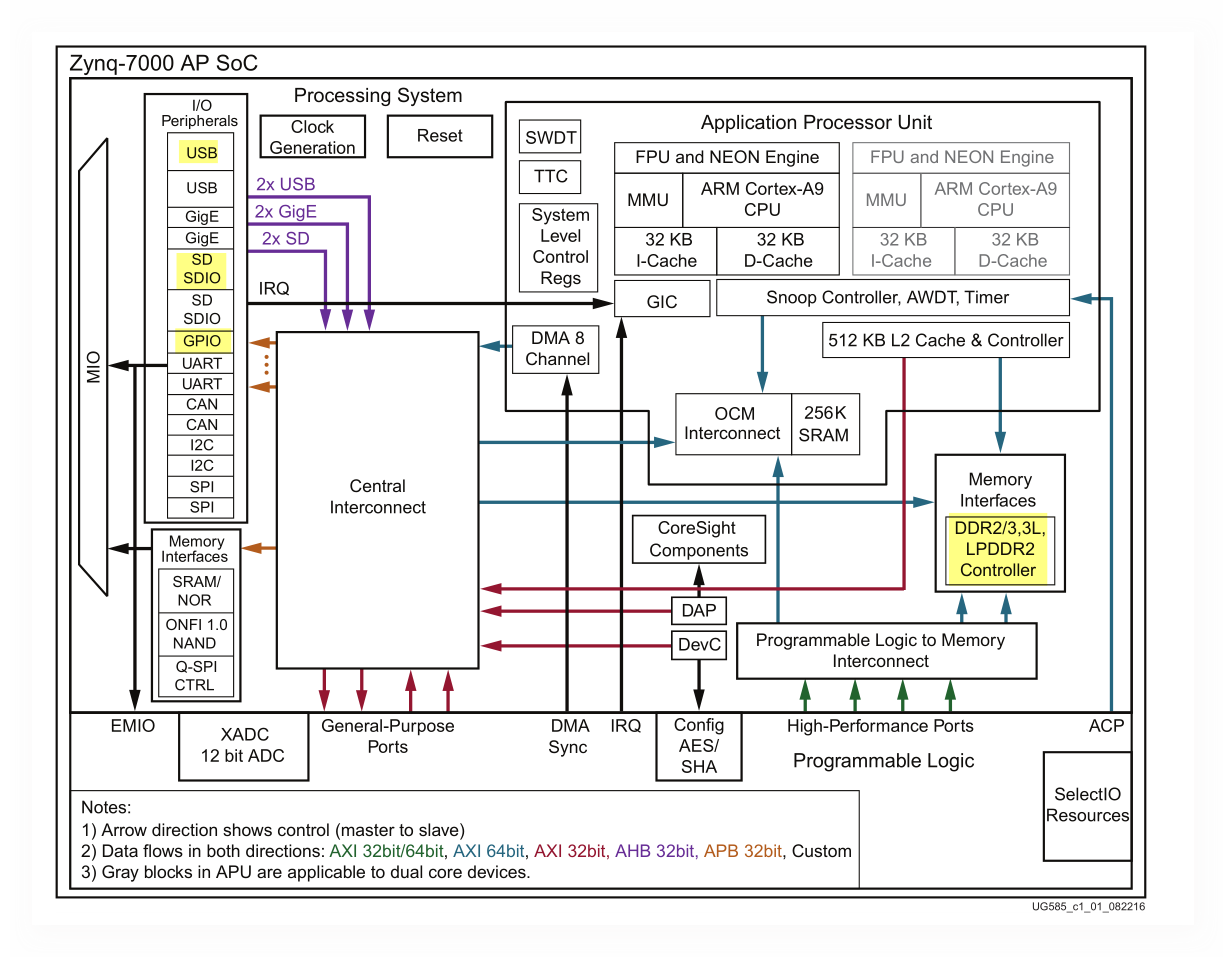

这里是总的陈述,一般工程类的说明会有一个关系图用于说明总的的原理,例如这里的关系图:

这张图在理解每个功能模块之间的相互联系起到了重要作用。一般在读文档时首先要熟悉这张图。当然,开头还会有一些其他的信息,比如关联文档等,这里就不多阅读。

3.other parts

挑选一个目前在用的模块阅读:GPIO部分。

先看GPIO的介绍:

The general purpose I/O (GPIO) peripheral provides software with observation and control of up to 54 device pins via the MIO module. It also provides access to 64 inputs from the Programmable Logic (PL) and 128 outputs to the PL through the EMIO interface. The GPIO is organized into four banks of registers that group related interface signals. Each GPIO is independently and dynamically programmed as input, output, or interrupt sensing. Software can read all GPIO values within a bank using a single load instruction, or write data to one or more GPIOs (within a range of GPIOs) using a single store instruction. The GPIO control and status registers are memory mapped at base address 0xE000_A000

GPIO外围设备提供软件观察和上至54器件引脚经过MIO模块。它也提供64引脚来自PL和128输出经由EMIO关联。这个GPIO为分为4个板卡,由寄存器控制关联信号。

每个GPIO独立而动态可编程,可以作为输入输出和中断检测。软件可以读取所有的GPIO的值在板卡使用单一加载指令或者写数据到一个或者多个GPIOs(同一范围的GPIO)使用一个单一存储指令。GPIO的控制和状态寄存器的基础地址……

【注释】基本上不需要复杂的语法,在单词量充足的情况下即可实现无障碍的阅读,但是想要快速理解比较困难,这需要一定的阅读经验。

接着就是特色features

一般就是对这个模块的一些重点信息做一个概括。

下面就是对具体的每一个功能做详解,这里由于没有设计需求就不一一列举。从中可以看到对于英文文档的阅读的主体在于介绍部分,其它部分的英语量一般不多,多以数据表格的形式说明。这也符合说明的特点。

所以对于这种标准的说明文,了解简介,即可得到相应的信息。

再来看一下SD/SDIO Controller

The SD/SDIO controller communicates with SDIO devices, SD memory cards, and MMC cards with up to four data lines. On the SD interface, one (DAT0) or four (DAT0-DAT3) lines can be used for data transfer. The SDIO interface can be routed through the MIO multiplexer to the MIO pins or through the EMIO to SelectIO pin in the PL. The controller can support SD and SDIO applications in a wide range of portable low-power applications such as 802.11 devices, GPS, WiMAX, UWB, and others. The SD/SDIO controller block diagram is shown in Figure 13-1. The SD/SDIO controller is compatible with the standard SD Host Controller Specification Version 2.0 Part A2 with SDMA (single operation DMA), ADMA1 (4 KB boundary limited DMA), and ADMA2 (ADMA2 allows data of any location and any size to be transferred in a 32-bit system memory - scatter-gather DMA) support. The core also supports up to seven functions in SD1, SD4, but does not support SPI mode. The Zynq-7000 AP SoC is expected to work with eMMC devices because the protocol is the same as SD, but this has not been extensively verified. Users must be careful to meet all timing requirements as they might or might not comply with eMMC. It does support SD high-speed (SDHS) and SD High Capacity (SDHC) card standards. The user should be familiar with the SD2.0/SDIO 2.0 specifications. These are listed in Appendix A, Additional Resources. The SD/SDIO controller also supports MMC3.31 standard. eMMC flash memories are not primary boot devices for Zynq-7000 family, but can be used as secondary boot devices. For details, refer to UG821, Zynq-7000 Software Developers Guide. The SD/SDIO controller is accessed by the ARM processor via the AHB bus. The controller also includes a DMA unit with an internal FIFO to meet throughput requirements.

这里就不逐字翻译,直接使用翻译软件直译

SD/SDIO控制器与SDIO设备、SD存储卡和MMC卡进行通信,最多有四条数据线。在SD接口上,可以使用1 (DAT0)或4

(DAT0- dat3)行进行数据传输。SDIO接口可以通过MIO多路复用器路由到MIO引脚,或者通过EMIO路由到PL中的SelectIO

引脚。控制器可以支持SD和SDIO应用,适用于各种便携式低功耗应用,如802.11设备、GPS、WiMAX、UWB等。SD/SDIO控制器

框图如图13-1所示。SD / SDIO控制器兼容标准SD主机控制器规范版本2.0 A2一部分SDMA(单操作DMA), ADMA1 (4 KB边界

有限DMA),和ADMA2 (ADMA2允许数据传输的任何位置和大小是32位系统内存-散集DMA)的支持。在SD1、SD4中,核心还支持

多达7个功能,但不支持SPI模式。预计Zynq-7000 AP SoC将与eMMC设备一起工作,因为协议与SD相同,但这一点尚未得到

广泛验证。用户必须小心地满足所有的时间需求,因为他们可能遵守也可能不遵守eMMC。它支持SD高速(SDHS)和SD

高容量(SDHC)卡标准。用户应该熟悉SD2.0/SDIO 2.0规范。这些都列在附录A“附加资源”中。SD/SDIO控制器

也支持MMC3.31标准。eMMC闪存不是Zynq-7000系列的主引导设备,但可以作为辅助引导设备使用。有关详细信息,

请参阅UG821, Zynq-7000软件开发人员指南。ARM处理器通过AHB总线访问SD/SDIO控制器。控制器还包括一个

具有内部FIFO的DMA单元,以满足吞吐量要求。

一般来说,理解大概的意思即可。

直译的不能直接用,但是可以在一定程度上提供词汇量,对于词汇量不好的来说,前期可以用其作为辅助。