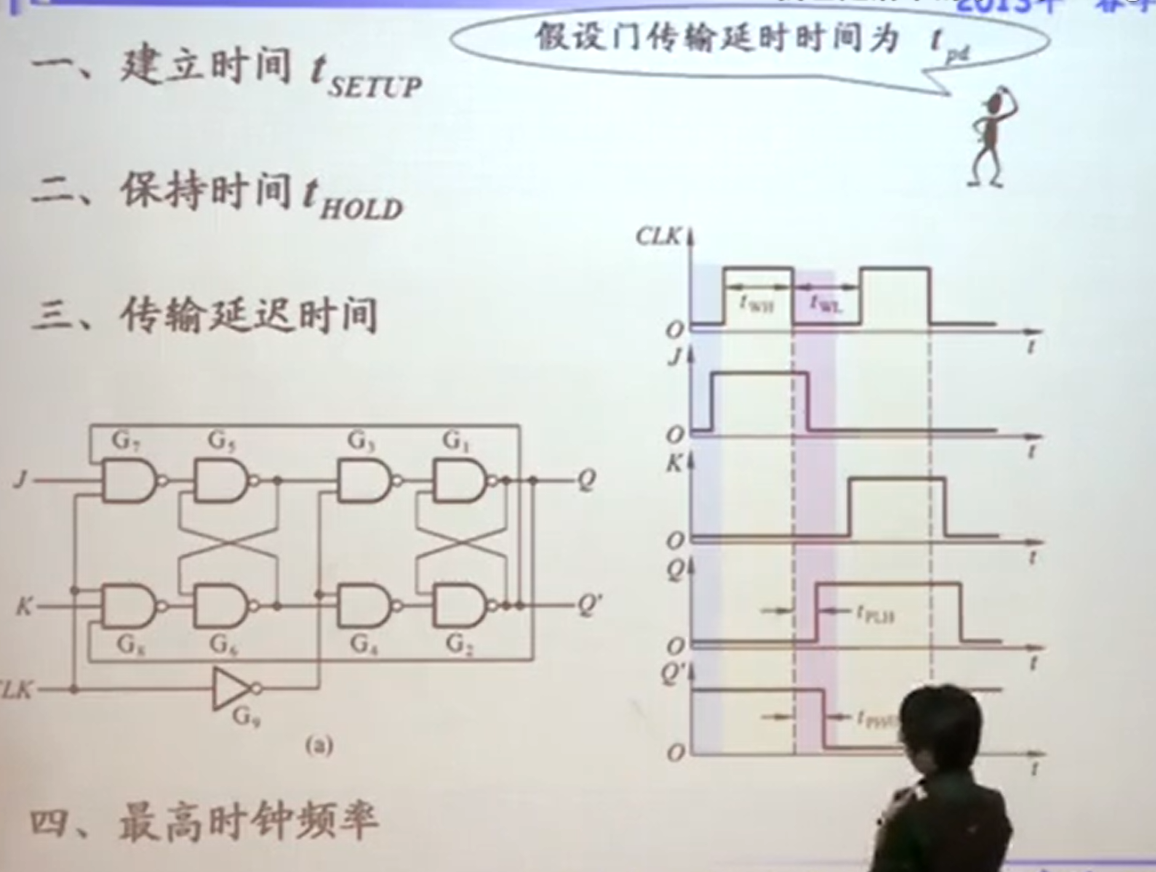

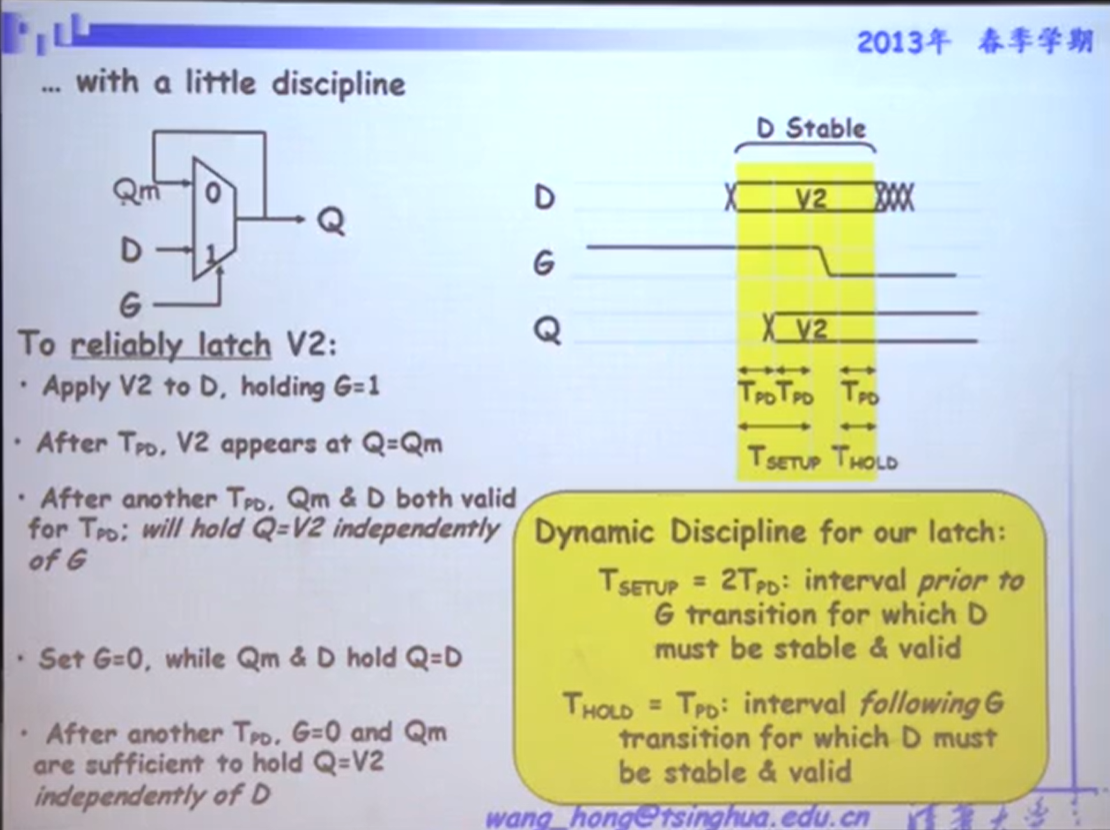

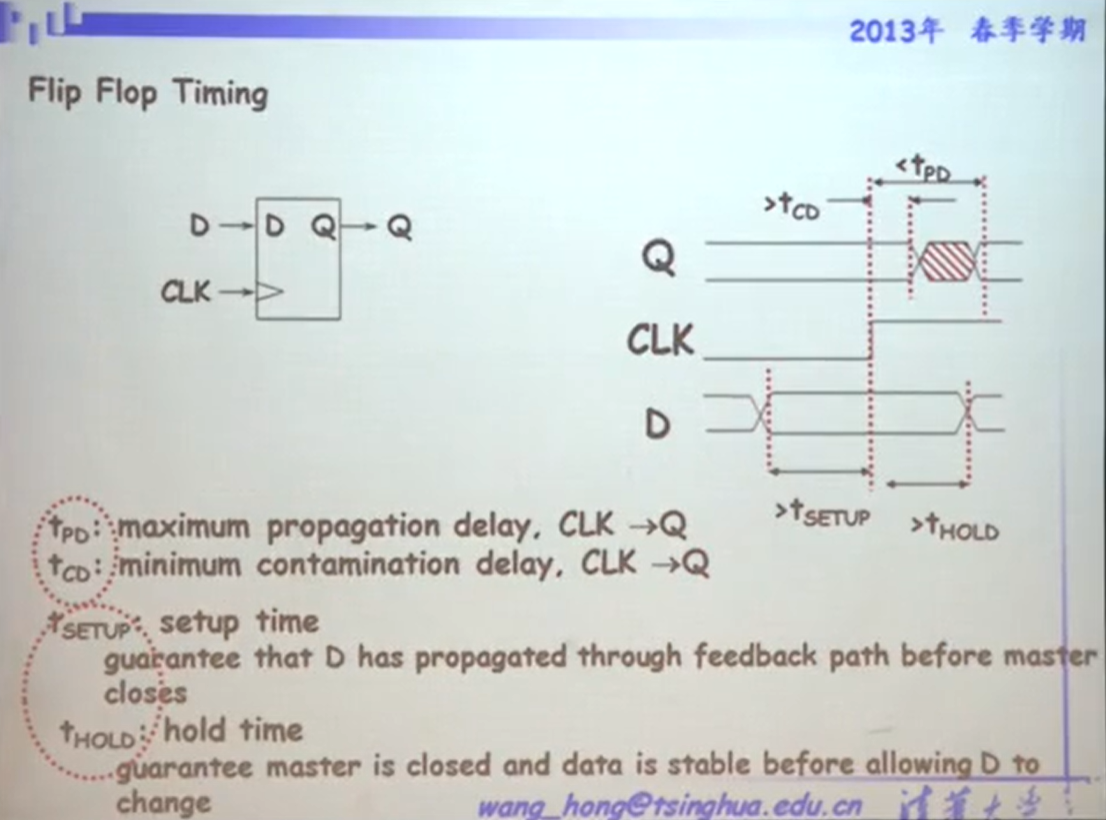

数据端和触发端之间的配合关系,这个配合关系就叫建立时间和保持时间。

建立时间:在触发信号到达之前,数据信号就建立

保持时间:触发信号到达之后,为了保证我的数据能稳定的写到后面去,数据还能坚持一段时间。

数据信号早点来,晚点走。确保数据信号可以稳定的写到Q和Q反

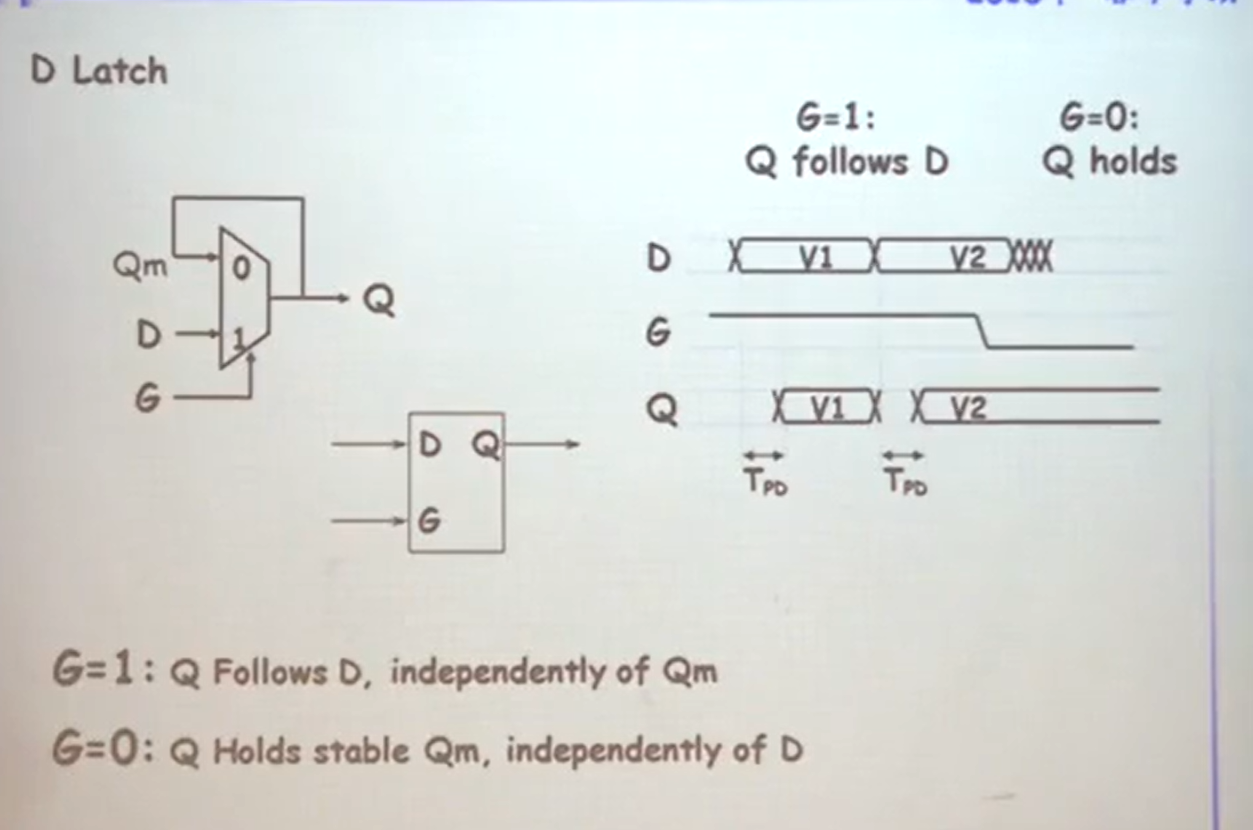

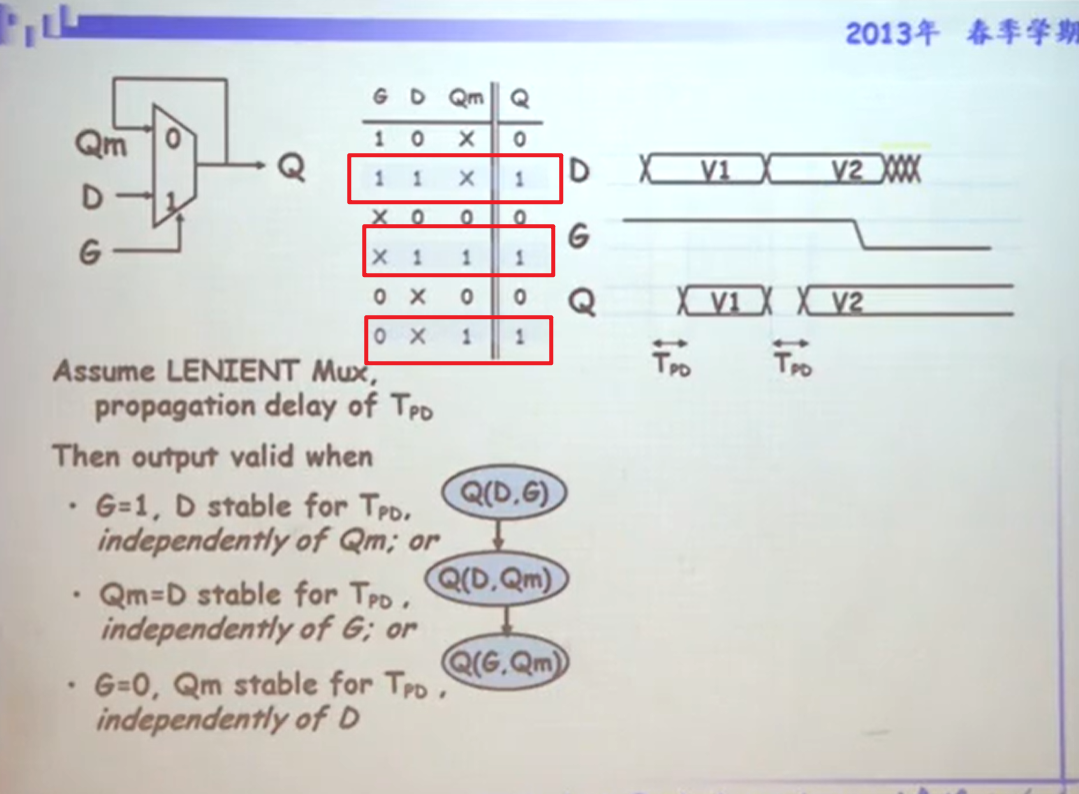

真值表每一行之间跳转要一个Tpd

输入信号要提前于clk上升沿T-su这么久到达才可以保证在clk到达时数据稳定。提前的这个时间叫做建立时间。

在时钟信号到来后,数据信号需要保持T-hold这么久,保证输出不会因为数据变化而产生差错。这个时间叫做保持时间。

这和逻辑运算无关,和稳定的实现逻辑功能有关

电平触发需要D信号维持至少一个tpd,传输到输出端要一个tpd

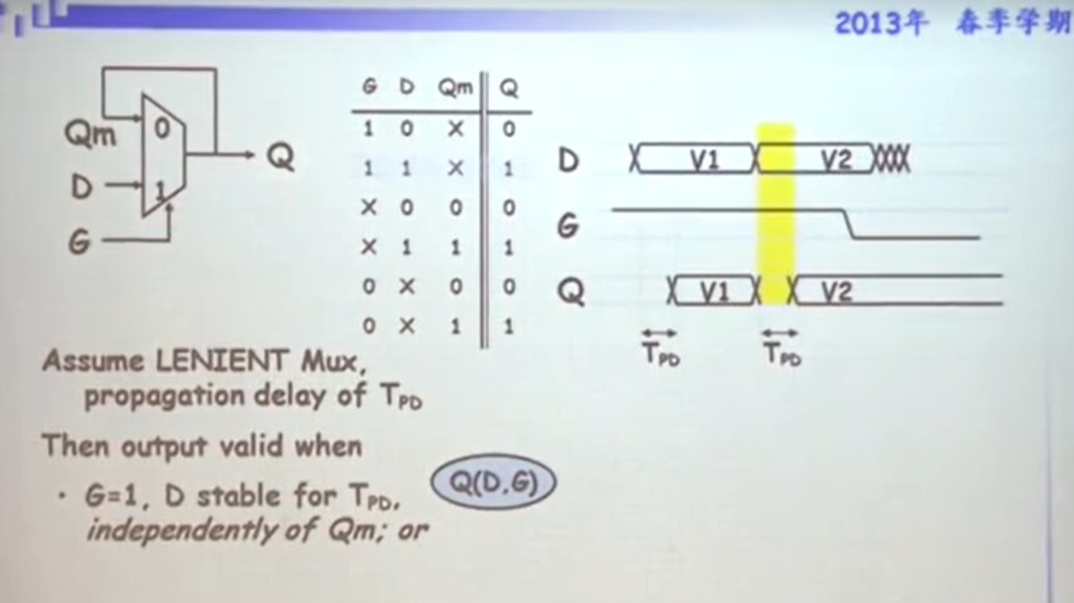

传进来 改变qm 然后锁存 在G发生变化时,为了保持Q还为1的话,就必须经过老师所讲的中间那个状态

D需要一个 tpd的时间,Q才会变,

D还需要一个tpd时间,否则Qm是不能写入Q,

因为要建立Qm和Q之间的连接 才能在G=0的时候保持状态呀~

就是保持时间要保证数据完全经过回环所有的cmos管,它才能真正的有能力锁存起来

其实这里没有给出选择器内部状态,Qm和d都同时存在于内部,由g决定将哪个放出,经过一个tpd后Qm虽然有了变化,但选择器内部它的值还是旧的,所以还要经过一个tpd让新值进入选择器代替旧值

G=0时,此时希望Qm不变这样结果才能保持,被锁进去,对应真值表中的一行。建立时间和保持时间分别在G=1和G=0的两端

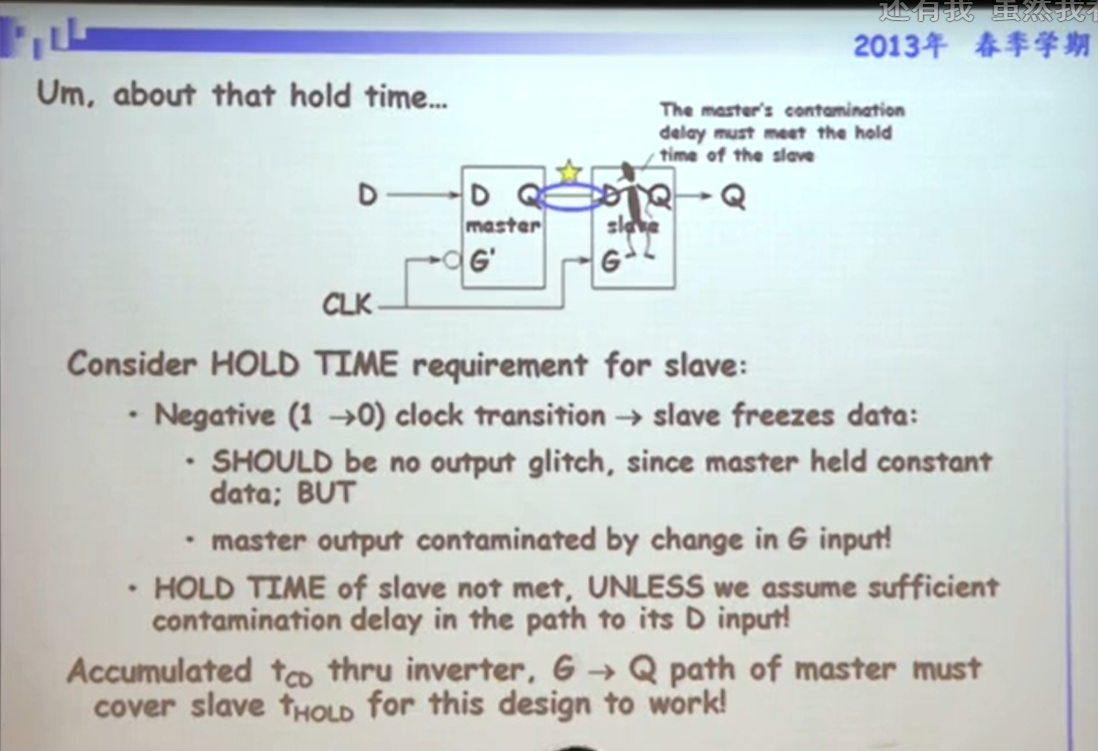

Tcd大于Thold(保持时间)

保持时间的概念是时钟信号到达后,输入信号需要保持的时间。时钟信号一变化,主触发器的输出信号在tcd之后就无效了,而从触发器还需要输入信号再保持tHOLD,所以需要tcd大于tHOLD(如果没理解错的话

主从结构的D触发器:主触发器的Tcd要大于从触发器的Thold.

如果Tcd小于Thold,可以增加模块加大Tcd.

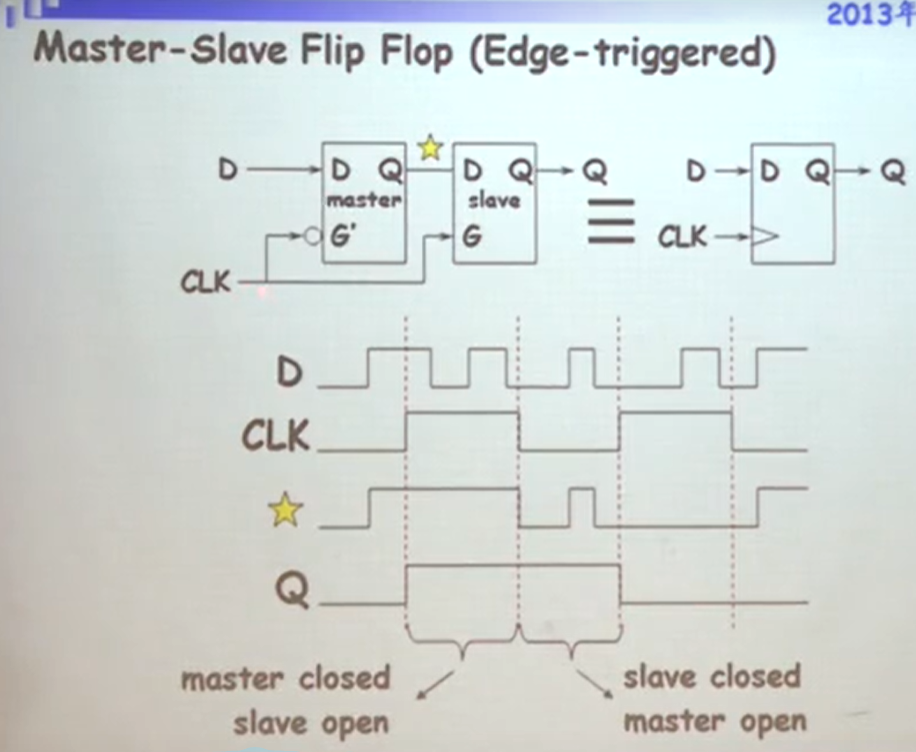

最高工作频率和tpd与tsetup有关,即触发信号周期至少要大于tpd+tsetup

而传输延迟时间tcd,tpd也都是在触发信号来之后D的变化才能反映到输出Q上

总结:如果是边沿触发器,关心的时间点都是触发信号,建立时间和保持时间一定要跨在触发信号的两端

本章需要掌握: