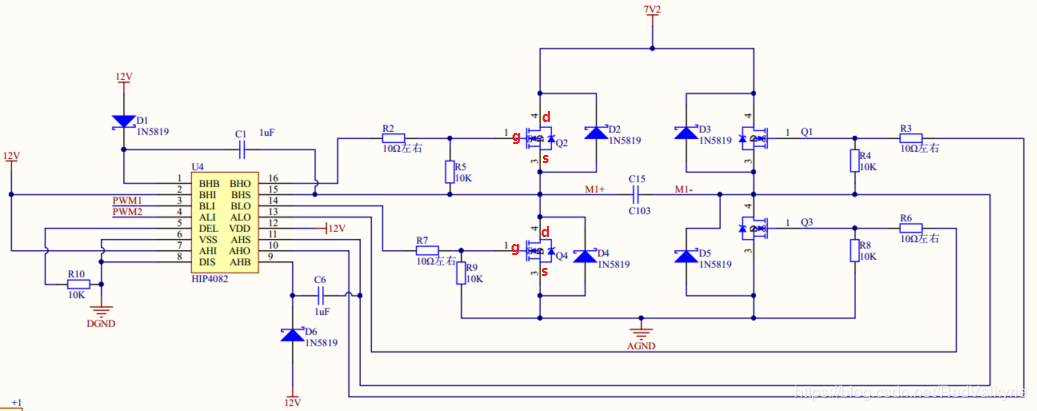

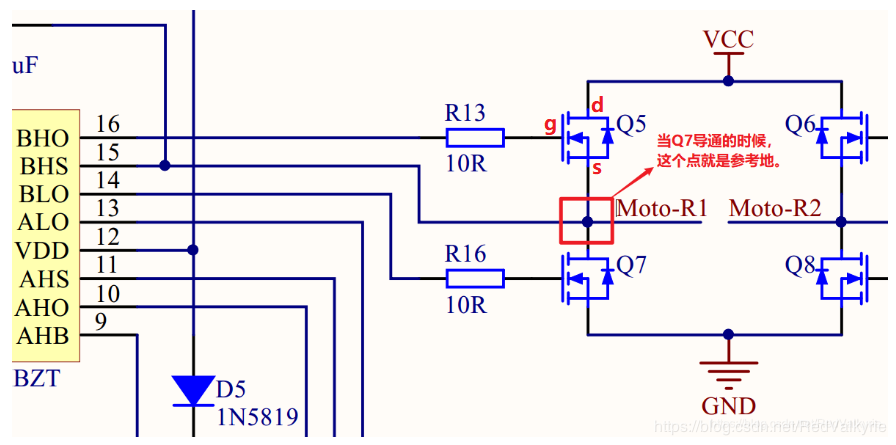

一、原理图

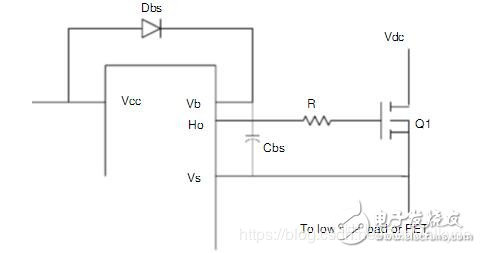

驱动原理图,因为突然回顾以前做过的这个驱动电路,所以记录一下防止遗忘。以下只列出以下主要电路:

二、化简电路再做分析的前提

前提,我们先明确以下知识点,再来把无关器件省略掉,分析主干电路。

MOS管导通的实质是对GS结电容充电,在上图所示的原理图我在G级串联一个电阻是为了限制充电速度,防止充电过快产生震荡。

栅极电阻一般串联一个10欧左右的电阻,GS级之间一般并联一个10K的电阻用来关断期间结电容的放电。

与MOS管并联的二极管是不必要的,因为MOS管内部集成了二极管,即体二极管。

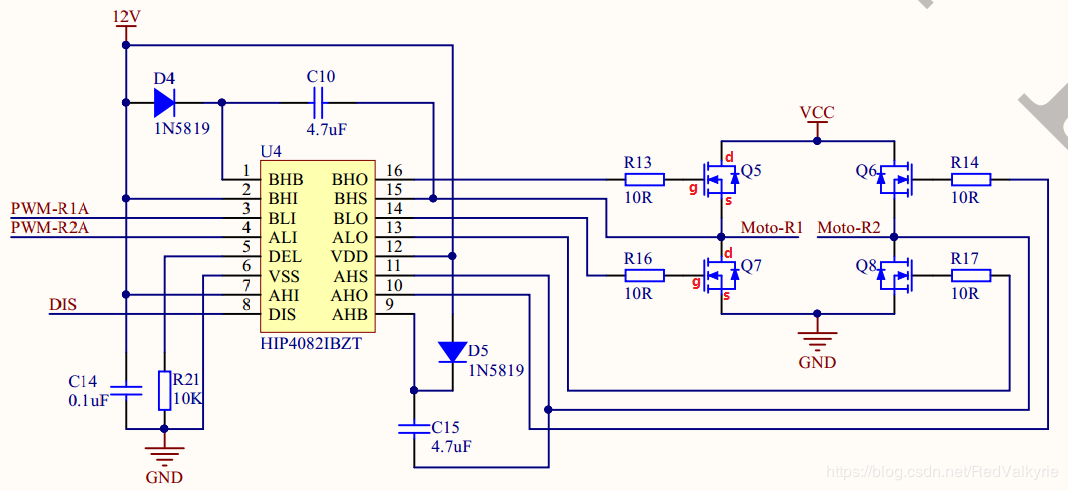

在不考虑串联的10欧姆左右的电阻以及GS级并联的10K欧姆的电阻,还有MOS管外面另外并联的二极管,电路简化至下图作分析:

三、分析一下自己的理解

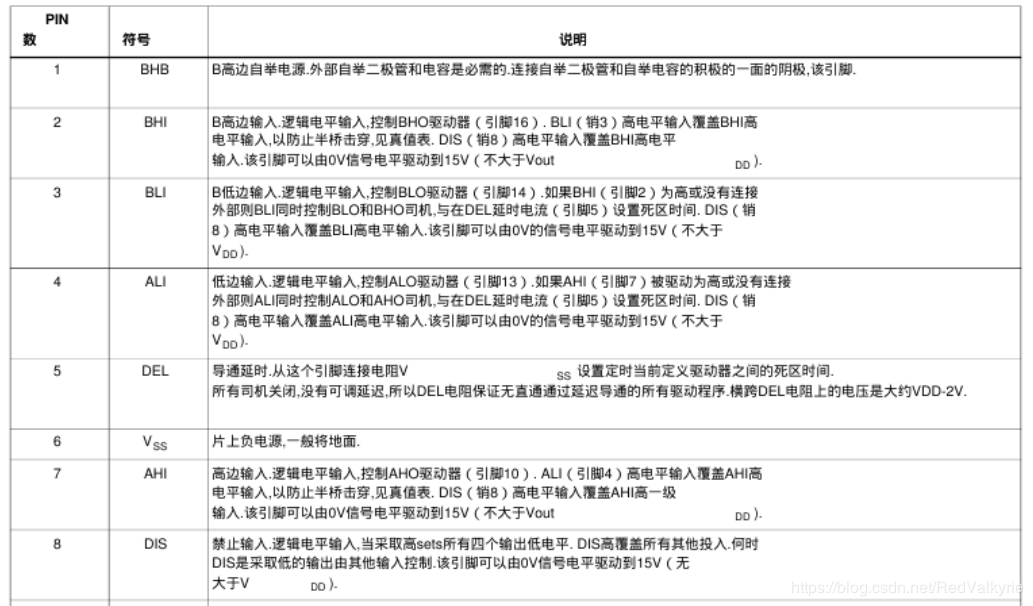

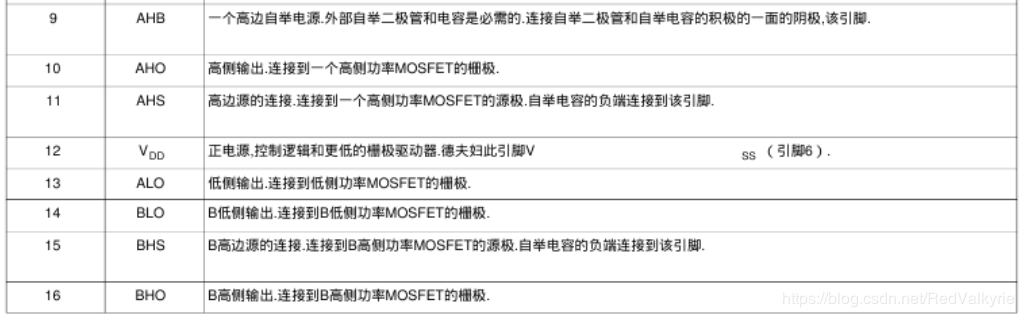

< 1 > 引脚说明

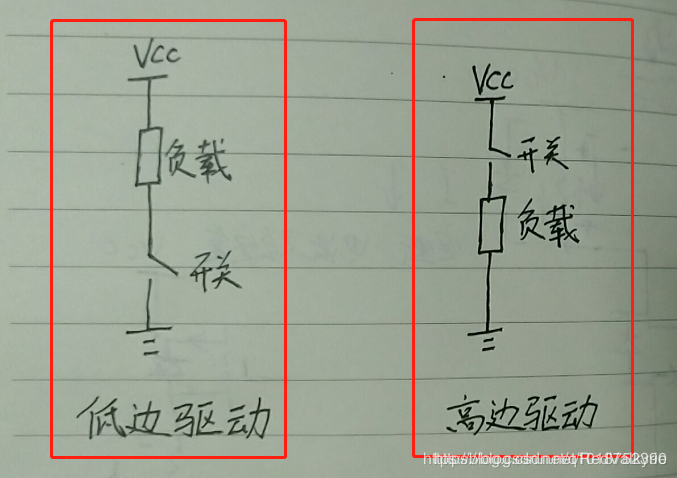

< 2 > MOS管的高端驱动和低端驱动

所谓的高边驱动或者低边驱动,指的是在电子电路驱动负载时,当需要控制开关时,开关所处电路的位置。“高”指的是“电源”,“低”指的是“地”。

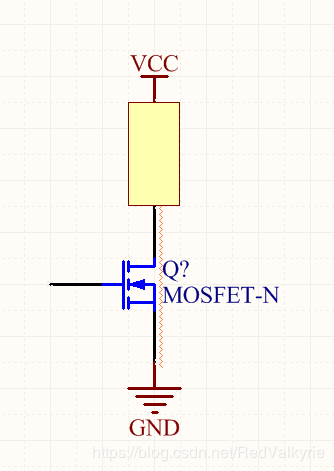

低边驱动简单的理解为:负载的一端默认与电路的正级即电源保持连接,负载的另一端与开关连接,当开关导通时,负载的另一端与地连接,负载开始工作,当开关与关断时,负载的另一端与地断开,负载停止工作。低边驱动/开关英文:Low Side Drivers,简称为LSD。具体到使用MOS管作为开关的情况的时候,MOS管相对于负载在电势的低端,其中D通过负载接电源,S直接接地。

对于NMOS管,只有当Vgs大于开启电压时,MOS管才能导通。所以当未导通时,S处于一个不能确定的电位。若让Vgs大于开启电压,则DS导通,S确定为地电位,此时仍可以保证Vgs大于开启电压,保持DS导通。

对于PMOS管,只有到Vgs小于一个值,MOS才能导通。此时S处于一个不确定的电位。若让Vgs小于开启电压,即使导通了,S确定下降到地电位,就不能保证Vgs小于开启电压。

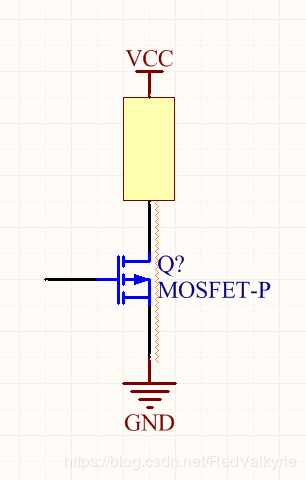

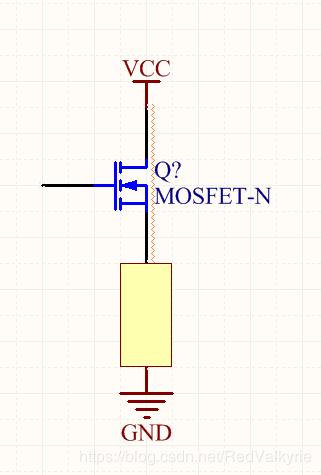

高边驱动简单的理解为:负载的一端默认与电路的负级即地保持连接,负载的另一端与开关连接,当开关导通时,负载的另一端与电源连接,负载开始工作,当开关与关断时,负载的另一端与电源断开,负载停止工作。高边驱动/开关英文:High Side Drivers,简称为HSD;具体到使用MOS管作为开关的情况的时候,MOS管相对于负载在电势的高端,其中D直接连接电源,S通过负载接地。

对于NMOS,只有当Vgs大于开启电压时,MOS管才能导通。所以当未导通时,S处于一个不能确定的电位。即使让Vgs大于开启电压,DS导通后,DS电位相等,同为电源电位,除非G极电位比电源电位还高,则不能保持导通状态。

对于PMOS,只有到Vgs小于一个值,MOS才能导通。此时S处于一个不确定的电位。若让Vgs小于开启电压,使DS导通,DS同为电源电位,还是能保持Vgs小于开启电压,是MOS保持导通状态。

总结:PMOS适合作为高端驱动,NMOS适合作为低端驱动。但是由于工艺等各方面的原因。在大电流情况下,通常仍把NMOS作为高端驱动。于是,为了保证高端驱动的NMOS的Vgs保持大于开启电压。我们会使用半桥驱动芯片。半桥驱动芯片把高端驱动的NMOS的S极作为参考地,输出一个恒定的开启电压,来控制MOS的导通。

< 3 > 电机驱动电路分析

如上图所示电机驱动原理图,我采用的是HIP4082全桥驱动芯片。将高端驱动的NMOS作为参考地。

因为我们是用的是NMOS管,所以当Ugs的电压大于开启电压,MOS管才被导通,而我在此处采用的自举的方式,输出一个恒定的开启电压,来控制MOS管导通。

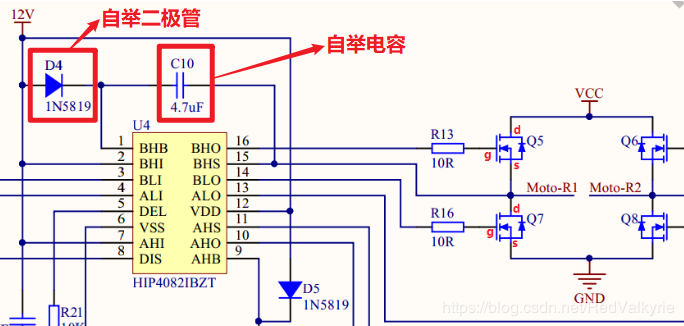

下面解释一下,在HIP4082驱动芯片这边的自举电路原理:

首先BHS引脚里的HS指的是High S极,也就是上管Q5的S极,可以看到此处下管Q7的S极是接地的,所以如果下管Q7处于导通状态的时候,BHS引脚,也就是上管Q5的S极就相当于接地了,这时BHS的电压也就是上图Q5的S极的电压。

这个时候,外部电源通过自举二极管向自举电容充电。

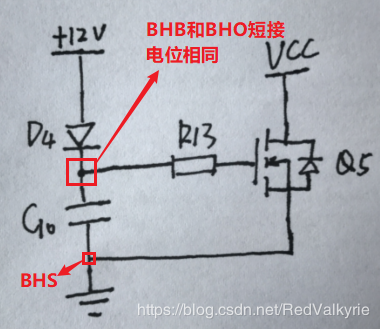

在处于目前下管Q7导通,上管Q5关闭的状态的时候,此时外部电源通过二极管和自举电容给电容充电,然后BHB和BHO引脚处于短接状态,此时上端MOS管Q5导通。

我们先假设这里C10充满电就是12V,因为BHB和BHO短路,此时自举电容充的电就通过BHS举给了BHO,所以BHB和BHO的电压是一样的。然后此时Q5的S级接地,忽略掉R13的时候电压约为12V,相当于Vgs之间是接了一个恒定的电压来保持这里NMOS管的必然导通。此处就是通过自举出来一个恒定的电压来确保Vgs的电压大于MOS管的导通电压解决了上面提到的当NMOS为高端驱动时的导通状态不确定的问题。

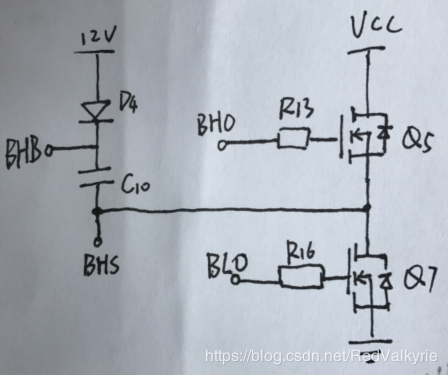

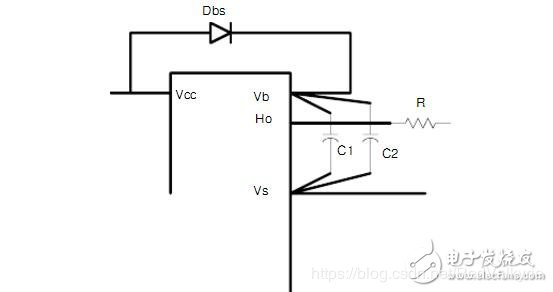

经过以上环节之后,上管Q5导通,下管Q7关闭,此时BHB和BHO就不处于短接的状态了,由于电容充满电了,BHB的电压是比BHS的电压高的。此时我手绘了一下电路如下图:

以上就是自举电路的原理。

值得注意的是:

正是因为这里自举电容只能在下管Q7导通的时候充电,所以一般的NMOS桥驱动都不能输出百分之百的占空比。你可以这么理解,就是此时电容里的电是维持上管Q5持续导通的,比如我假设的这里电容充满电之后电压是12V,但是总有时候电容里的电是会放光的,此时自举电容电没了就举不动了,这个时候上管Q5就关闭了,而这个过程是慢慢的,可能会导致上管的G极电压出现非饱和区和截止区,造成上管gg,所以一般限制占空比最高在 95% 到 98%95\% 到 98\%95% 到 98% 。然后上管Q5关闭之后,Q7导通,继续给电容重新充电。然后循环这个过程。

上图只是我们使用的某一款驱动芯片,下面列出的是通用解释自举电路内部原理的图,其中Vbs(驱动电路Vb和Vs管脚之间的电压差)给集成电路高端驱动电路提供电源。该电源电压必须在10-20V 之间,以确保驱动集成电路能够完全地驱动MOS栅极器件。Vbs电源是悬浮电源,附加在Vs电压之上(Vs通常是一个高频的方波)。有许多方法可以产生Vbs悬浮电源,其中一种如本文中介绍的自举方式。这种方式的好处是简单、低廉,但也有局限性。占空比和开通时间受限于自举电容的再充电(长时间导通和大占空比时要求有充电泵电路支持,详见AN-978C了解):

对于含有自举电路的PCB布板方法,需要注意自举电容要尽可能靠近IC的管脚。如下图所示,至少有一个低ESR的电容提供就近耦合。例如:如果使用了铝电解电容做为自举电容,就应再用一个瓷电电容。如果自举电容是瓷电或钽电容,自己作为就地耦合也就足够了。

< 4 > 具体到通过PWM控制电机占空比

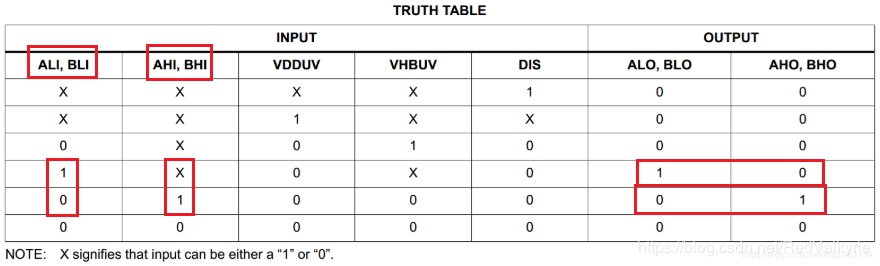

首先列出HIP4082芯片引脚的真值表:

首先看看DIS引脚,这个引脚的作用是控制芯片是否工作的。我当初接的是低电平,也就是芯片一直保持工作。但是它也可以接一个IO口,让GPIO输出高电平或者低电平来控制芯片是否工作。

再看BHO和BLO的引脚,我的理解是,B表示这个芯片控制的其中一个半桥的引脚开头字符,A就是另外一个半桥引脚的开头字符,H(high)表示的上管,L(low)表示的是下管,O表示的是ON,也就是打开的意思。通过真值表我们可以看到,这里以B开头的半桥引脚为例:

当BLI为高电平的时候,意思也就是比如我现在给的 90%90\%90% 的占空比,他处于高电平的那段时间,此时无论BHI接的什么电平,此处接的是12V高电平,这个时候下管是关闭的,上管是导通的,也就是这段时间用来给电机以 90%90\%90% 的占空比输出。

当BLI为低电平的时候,也就是 90%90\%90% 占空比的另外 10%10\%10%处于低电平的时间段,若BHI为高电平的时候,此时上管关闭,下管导通,也就是这段时间去给自举电容充电。

————————————————

版权声明:本文为CSDN博主「万树不会古冬u」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/RedValkyrie/article/details/105463217