参考: https://www.deyisupport.com/question_answer/dsp_arm/sitara_arm/f/25/t/138266.aspx

// vim drivers/spi/spi-omap2-mcspi.c

654 static int omap2_mcspi_setup_transfer(struct spi_device *spi,

655 struct spi_transfer *t)

656 {

// ... ...

// 这里是设置 D0 为 MOSI master input

// D1 为 MISO master output

680 #if 0

681 /* standard 4-wire master mode: SCK, MOSI/out, MISO/in, nCS

682 * REVISIT: this controller could support SPI_3WIRE mode.

683 */

684 l &= ~(OMAP2_MCSPI_CHCONF_IS|OMAP2_MCSPI_CHCONF_DPE1);

685 l |= OMAP2_MCSPI_CHCONF_DPE0;

686 #endif

687

// 这里设置为 D0 为 MISO master output

// D1 为 MOSI master input

688 #if 1

689 /* standard 4-wire master mode: SCK, MOSI/out, MISO/in, nCS

690 * REVISIT: this controller could support SPI_3WIRE mode.

691 */

692 l &= ~(OMAP2_MCSPI_CHCONF_DPE0);

693 l |= (OMAP2_MCSPI_CHCONF_IS | OMAP2_MCSPI_CHCONF_DPE1);

694 #endif

// ... ...

-

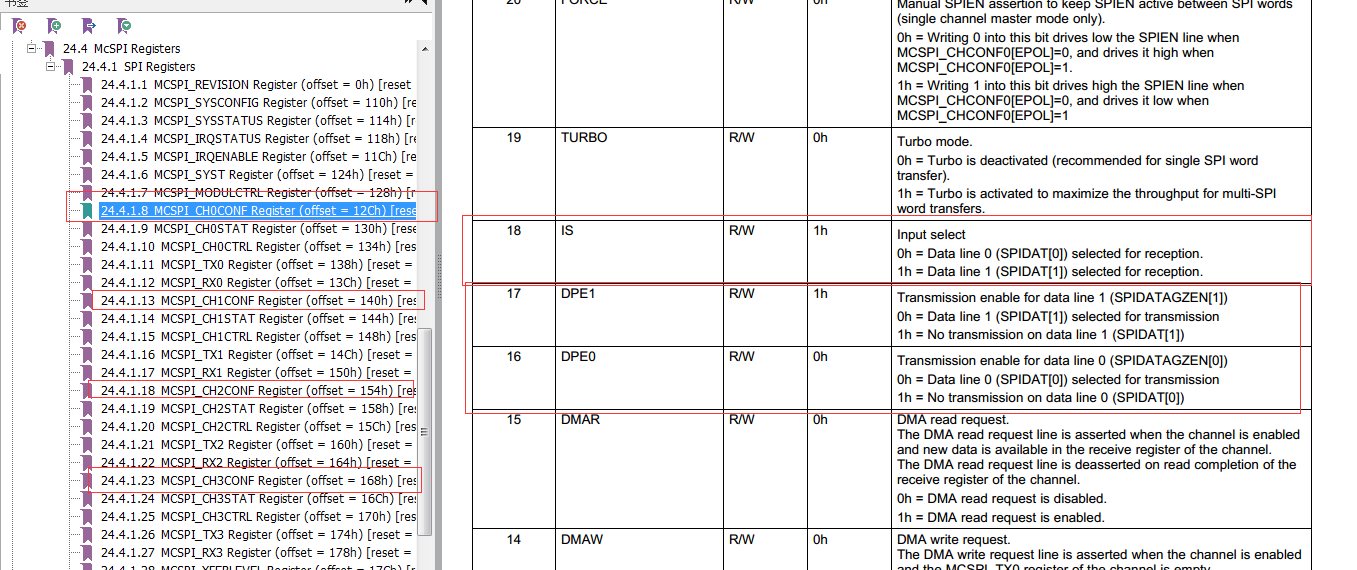

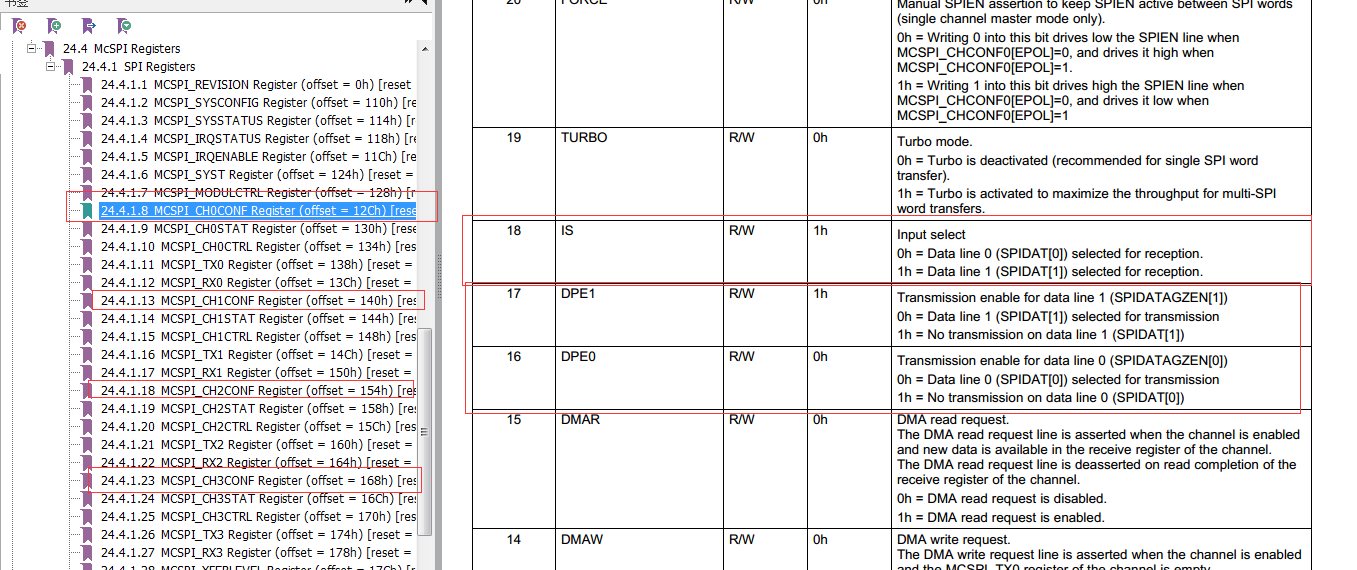

对应的 TRM 如下图: