本文整理了arm cortexA 系列的CPU的相关信息,以便在芯片选型时提供帮助。

Cortex-A发布时间

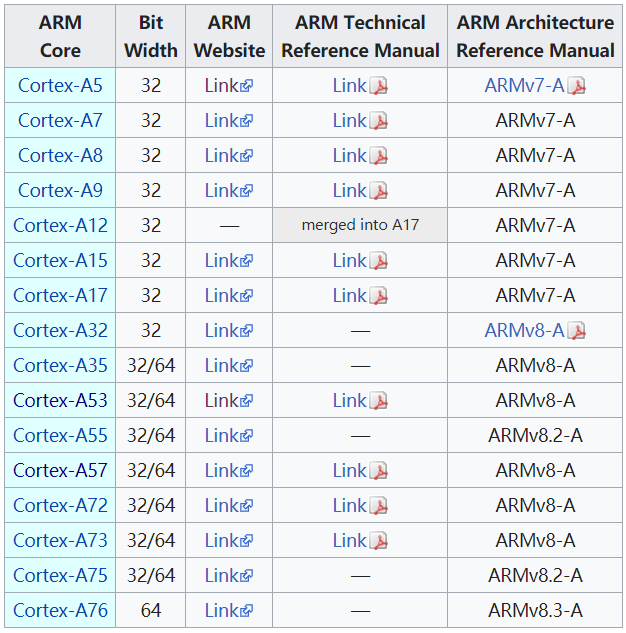

Cortex-A 支持的位数及架构

Cortex-A 系列的芯片

ARMv7-A内核的比较

从DMIPS/MHz角度的cpu性能比较

A5(1.57) < A7(1.9) < A8(2.0) < A9(2.5) < A12(3.0) < A15(3.5~4.1) < A17(4.0)

ARMv8-A内核的比较

从DMIPS/MHz角度的cpu性能比较

A35(1.78) < A53(2.24) < A57(4.6) < A72(4.72) < A73(~6.35) A55,A75,A76暂时未知

A55比A53 15%功耗提升,18%性能提升;

A75比A73 16-48%性能提升;

A76 提升了25%的整数运算能力,提升了35%的浮点运算能力,内存带宽提升了90%相对A75,性能上是A73的两倍。

big.LITTLE

big.LITTLE是一种节能省耗技术,最高性能的ARM CPU核心与最高效的ARM CPU核心相结合,以更低的功耗提供最好的工作性能,最快的处理任务速度。

那什么时候使用什么核?由kernel的scheduler实现决定,包括三种方式:集群切换(Clustered switching),CPU迁移(CPU migration),HMP(Heterogeneous multi-processing)

集群切换,只能同时全开大核或同时全开小核,最高性能 = 单个大核性能 X 大核个数;实现最简单,切换灵活度低。

例如,A57和A53构成big.LITTLE,调度器一次只能全开4cores的A57 或者 全开4 cores 的A53

CPU迁移,每个大核与每个小核构成虚拟核心,每个虚拟核心同时只允许打开一个大核或一个小核,最高性能 = 单个大核性能 X 大核个数;切换灵活度中等。

例如,A15与A7组成big.LITTLE,每一组A15和A7看作一个虚拟核心,每个虚拟核心中的core在某个时刻只有一个运行。

HMP,所有核心可同时全开,最高性能 = 单个大核性能 X 大核个数 + 单个小核性能 X 小核个数;实现起来最复杂,切换灵活度高。

简要的列出支持big.LITTLE的CPU:

A7 LITTLE

A15 big

A17 big

A32 LITTLE

A35 LITTLE

A53 big/LITTLE

A57 big

A72 big

A55 big/LITTLE

A75 big

A76 big

A73 big

DMIPS/MHz

MIPS

MIPS(Million Instruction Per Second)表示每秒执行多少百万条指令,如10MIPS,表示每秒一千万条指令。

MIPS/MHz

表示CPU在每MHz的运行速度下可以执行多少个MIPS,如10MIPS/MHz,表示如果CPU运行在1MHz的频率下,每秒可执行一千万条指令,如果 CPU 运行在 5MHz 的频率下,每秒可执行五千万条指令。

超标量运行

以前计算机大部分都是"单线程"工作模式,就是说在1MHz工作频率下(1秒钟震荡1M次周期,而且取指、译码、执行操作只能串行运行),计算机1秒钟处理的指令不会超过1M条,因为每秒中它只能计算1M次而很多指令不是1次就能完成的,而现在的计算机都使用了多级流水线结构,取指、译码、执行……可以并行运行,就是说在1个计算周期(次)计算机能够执行超过1条以上的指令,这样,在1MHz的运行频率下,它就能得到超过1MIPS的执行效率了。

DMPS/MHz

DMIPS是“Dhrystone MIPS”的缩写

DMIPS是一个测量CPU运行一个叫Dhrystone(整数运算)的测试程序时表现出来的相对性能高低的一个单位(很多场合人们也习惯用MIPS作为这个性能指标的单位)。

因为基于程序的测试容易受到恶意优化的干扰,并且DMIPS指标值的发布不受任何机构的监督,所以使用DMIPS进行评估时要慎重。例如对Dhrystone测试程序进行不同的编译处理,在同一个处理器上运行也可以得出差别很大的结果。

DMIPS的简单推算公式:

DMIPS = DMIPS/MHz * 主频(MHz) * 核心数

例如,RK3288是Quad-core ARM Cortex-A17, up to 1.8 GHz,那么,DMIPS=4x1800x4=28800