设计一个101序列检测器。要画出状态转移图,写verilog,并仿真测试。

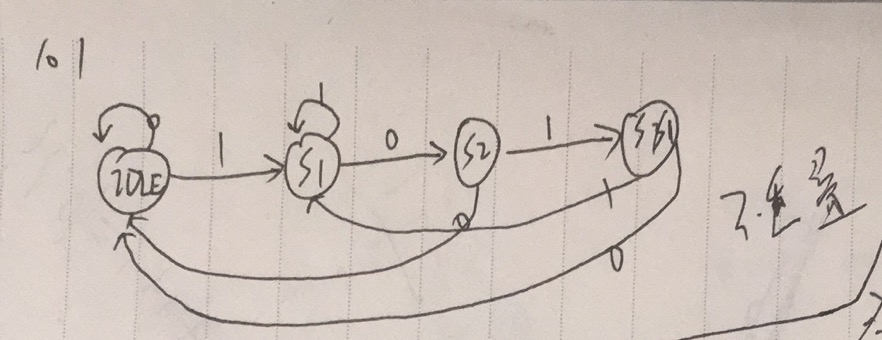

使用Moore状态机进行序列检测,状态转移图如下:

module seq_101( clk, rst_n, data_in, data_out ); input clk; input rst_n; input data_in; output reg data_out; localparam IDLE=4'b0001,s1=4'b0010,s2=4'b0100,s3=4'b1000; //state change reg [3:0]current_state; reg [3:0]next_state; always@(posedge clk or negedge rst_n) if(!rst_n) current_state<=IDLE; else current_state<=next_state; //next_state generate always@(*)begin case(current_state) IDLE:begin if(data_in==1) next_state=s1; else next_state=IDLE; end s1:begin if(data_in==0) next_state=s2; else next_state=s1; end s2:begin if(data_in==1) next_state=s3; else next_state=IDLE; end s3:begin if(data_in==1) next_state=s1; else next_state=IDLE; end default:next_state=IDLE; endcase end // always@(posedge clk or negedge rst_n) begin if(!rst_n) data_out<=0; else if(current_state==s3) data_out<=1; else data_out<=0; end endmodule

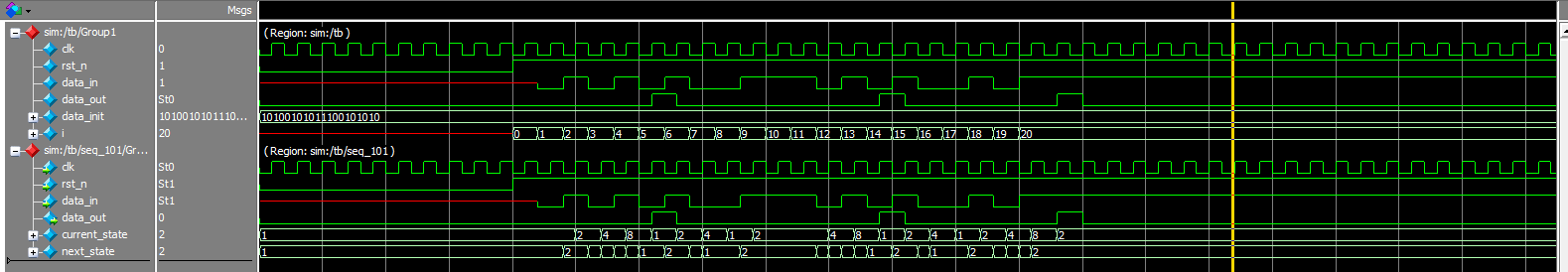

`timescale 1ns/1ns module tb; reg clk; reg rst_n; reg data_in; wire data_out; reg [19:0]data_init; integer i; seq_101 seq_101( .clk(clk), .rst_n(rst_n), .data_in(data_in), .data_out(data_out) ); initial clk=0; always #10 clk=~clk; initial begin rst_n=0; data_init=20'b1010_0101_0111_0010_1010; #200; rst_n=1; for (i=0;i<20;i=i+1) #20 data_in=data_init[i]; end endmodule