Verilog在行为级建模时常用到的一些函数,变量等。

1:$random(seed),每次根据seed的值产生一个32位的有符号数,seed的数据类型必须是寄存器(reg),整形(integer),时间(time)等类型。变形$dist_uniform(seed,start,end)。

integer a_time;

integer AP_SEED;

a_time = $dist_uniform(AP_SEED,min_time,max_time);

2: Driver strength spec,只适用于线网等类型的变量,wire tri wand等。可以在变量声明或连续赋值中使用。一对关键字分别表示(0,1)时的strength. 有supply,strong,pull,weak,highz等,strength按8个level划分。

assign (pull0,pull1) SD1_CLK = 1'b0;

3: $display("pc_mon_%d (time: %t): pc_ca7=%h ", PC_NUM,$time,cur_pc);

4: tranfif1 gpio_pads_logic0 (gpio_pads[0], tb_gpio_pads[0], select_gpio_driver);表示select_gpio_driver为1时,两个信号双向连接起来。

5:bufif1 bf1 (outw, inw, controlw); notif1 bf1(outw, inw, controlw); 表示相应的control为1时,输出会为Z,否则正常logic。只能单向传输。

6:buf和not可以有多个输出。 buf b1(out1, out2, in); in输入,out1,out2输出。只能单向传输。

7: specify模块用于指定source与destination之间的时延,参数用specparam表示。

8:final begin...end,在$finish之前,会显式调用的procedure。

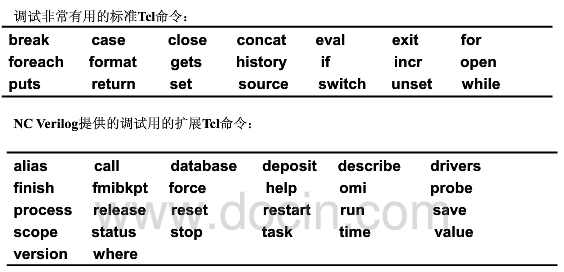

9:NC verilog调试的一些tcl命令:

deposit,与force信号作用类似,但是如果有驱动自然会跟随驱动的情况。

verilog中的位运算符,缩位运算符,逻辑操作符。

1)位运算符:操作数几位,结果就有几位,若两个操作数位数不同,位数短的操作数做段补零。

按位取反:~

按位与:&

按位或:|

按位异或:^

按位同或:^~或~^

2)缩位运算符:结果只有一位。

与缩位运算:&

或缩位运算:|

异或缩位运算:^

与,或,异或,和非运算符组成的复合运算符:~&, ~|, ~^

3)逻辑运算符:

逻辑与:&&

逻辑或:||

逻辑非:!

逻辑与和逻辑非是双目运算符,逻辑非是单目运算符。