由于工作内容和行业性质的原因,经常画的PCB是两层或者四层的低速板子,也一直想学习高速布线的相关知识,但就是无法实践逼迫不了自己,最近公司刚好接到一个项目涉及到了DDR3和NAND FLASH,乘此机会逼自己一把学习高速布线,下面大概是我总结的一些东西。在这里采用的Altium Designer软件,Candence软件还不会,等学完这个准备去学Candence。

首先找到了三星的一款DDR3芯片收据手册,大致看了一些要求和时序这些,然后去网上找了一下这些参数具体代表的含义,先对DDR3形成了一个直观的了解,然后在高速先生网站看了一些基础知识,大家可以去我的另一篇文章去看看https://www.cnblogs.com/zhiqiang_zhang/p/13889402.html。然后就还是动手实践了,实践也不是一步到位的,得分目标进行:

目标1:只熟悉DDR3的引脚布局,扇出和拓扑结构(T型和FLY-BY)以及绕等长线

1、在我网上随便找一个DDR3相关的原理图,然后自己照猫画虎画下来,包括器件封装等;

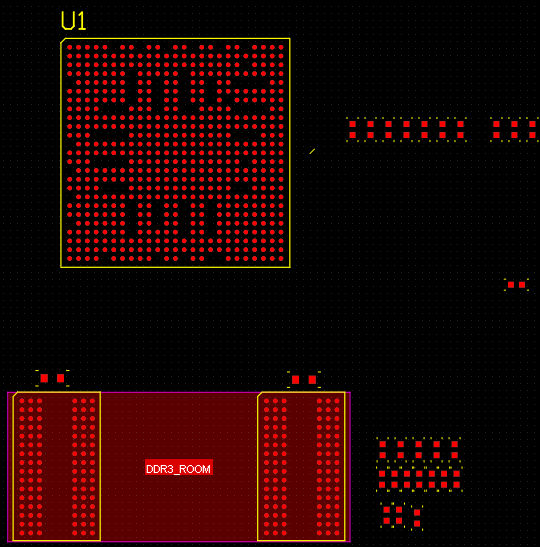

2、完成封装分配后导入PCB,然后进行布局,主要进行的是DDR周围滤波电容的布局,这一步刚入门的新手可以先跳过,将所有电容仍在一边先不管,将主要的精力放在布线上面,等自己画过一次有点经验和直观的了解之后在进行电容布局;

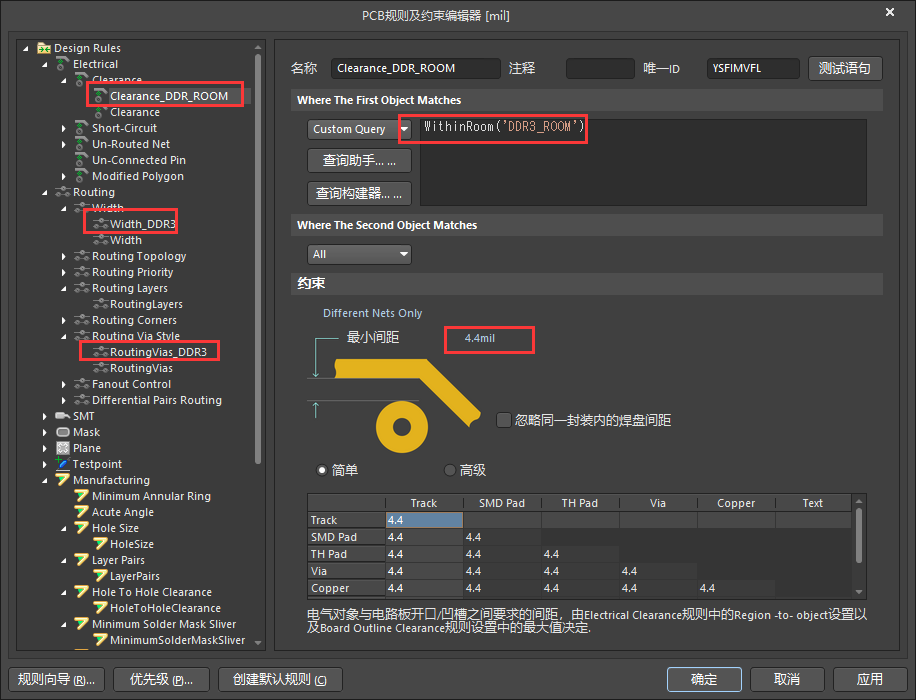

2、给DDR3芯片绘制ROOM区域,并设立区域规则,主要包括线宽和间距,并运用规格 WithinRoom('DDR3_ROOM'),具体的线宽要根据阻抗计算结果来设置;

3、同步骤一,给DDR区域设置过孔内径和外径;

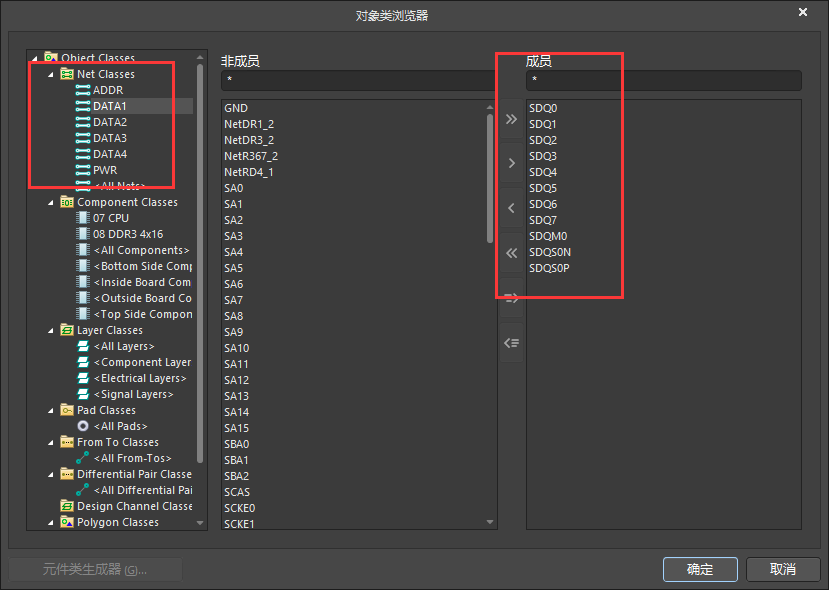

4、设计类规则,DDR3的所有线主要分别为三大类:电源类一组,数据类一组,控制命令和时钟为一组;(具体分类可参照我上一篇文章)

分类操作步骤:PCB界面,设计->类,在Netclass一栏添加类,也可以在画原理图的时候提前放置类标签进行分类,推荐这一种方式。

5、进行时钟和控制类的小T点的设计:注意DDR2的控制时钟走的是T型结构,需要绘制大T点,DDR3走FLY-BY结构,不需要大T点

DDR的封装很有特点,他的控制和时钟基本位于下半部分,数据位于上半部分,所以小时钟和控制等T点的扇出方式为朝着肚皮下方中间没有BGA球的地方,总的走线位于线片下半部分,上半部分留给数据类,然后在再底层将两个DDR的这部分连接。注意差分时钟的走线

注意的是多片DDR将一片线走了之后复制到另外几片DDR

6、设置差分对,在规则里面设置差分对线宽和间距

7、先走时钟差分线,连接几片DDR,顺序大概为先连接时钟差分对,然后依次连接其他的地址和控制线

8、CPU扇出,选怎布线-扇出-器件,选择前两项

9、连接数据类,先将差分对SDQS从中间拉出来