Cortex-M0(+)内核的处理器架构简介

系统架构

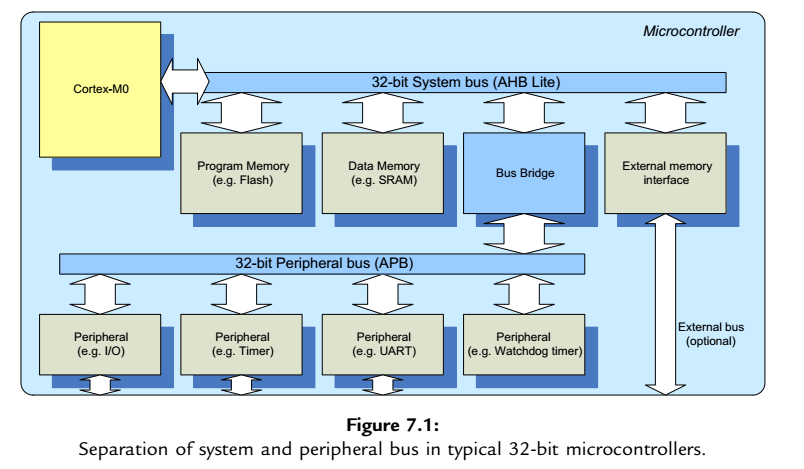

Cortex-M0处理器具有32位系统总线接口,以及32位地址线,即有4GB的地址空间。

- 1

- 2

系统总线基于AHB_Lite高级高性能总线协议。外设总线基于APB高级外设总线协议,通过一个转换桥连接到AHB上。这只是Cortex-M0内核的大概模式,Cortex-M0+的存储器系统与Cortex-M0基本相同。但是厂商根据需要会进行调整。

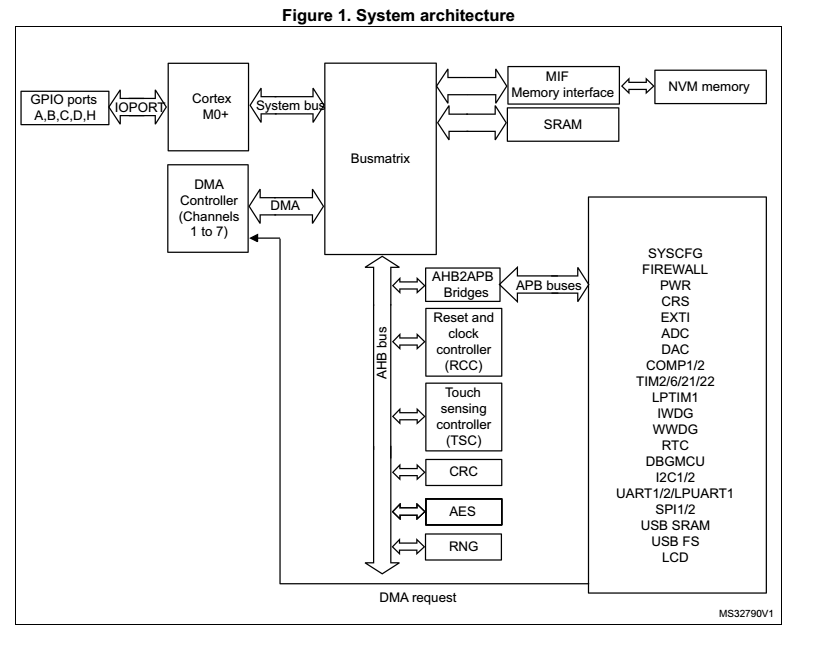

以下的是基于cortex-M0+内核的stm32L053的内部架构图。

可以看到GPIO口挂在了内核上,由BusMartix负责AHB,DMA,SRAM,MIF之间的数据交换

主总线和外设总线是分离的,所以很多情况下时钟频率也不同。我们可以使外设运行在较低的频率上,或者关闭不用的外设时钟,这样可以降低功耗。

存储器映射

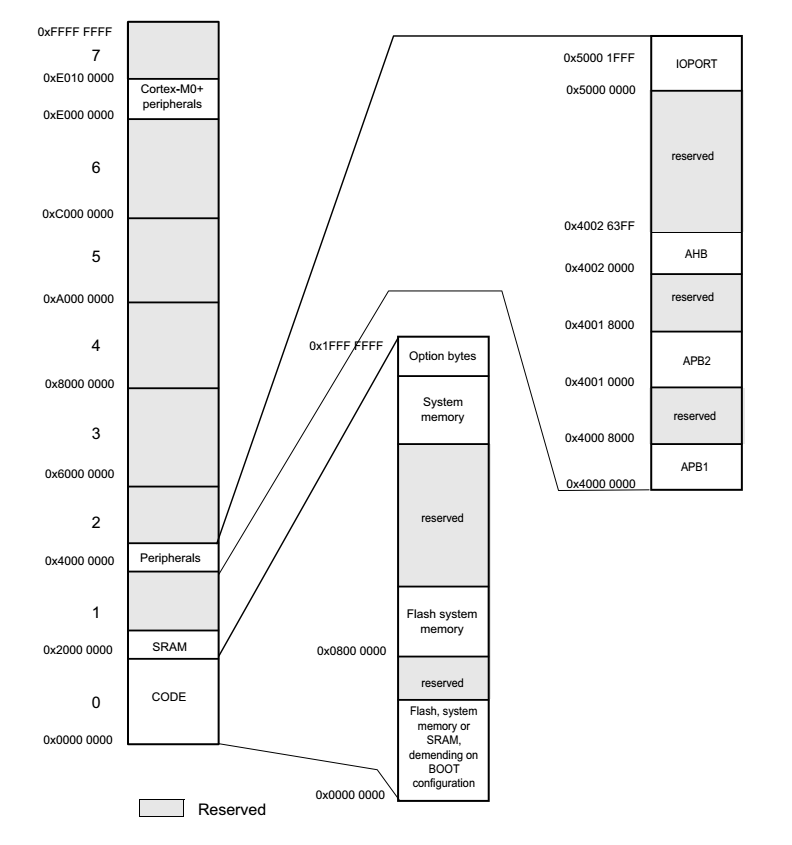

Cortex-M0(+)处理器的4G存储空间从架构上被分为多个区域。总的被分成8个大部分,每个部分512M。

虽然映射已经被架构预先定义,但是实际分配却是很灵活的。

1.代码区域 (0x0000 0000~0x1FFF FFFF) 512M,主要用于存储代码

2.SRAM区域 (0x2000 0000~0x3FFF FFFF) 512M,主要用于数据存储

3.外设区域 (0x4000 0000~0x5FFF FFFF) 512M,主要用于外设及数据存储。不允许执行程序

4.RAM区域 (0x6000 0000~0x9FFF FFFF) 1GB,外部RAM区域,由两个512M区域组成

5.设备区域 (0xA000 0000~0xDFFF FFFF) 1GB,由两个512M组成。属性不同。主要用于外设和IO口,不允许程序执行,但是可以用作通用数据存储。

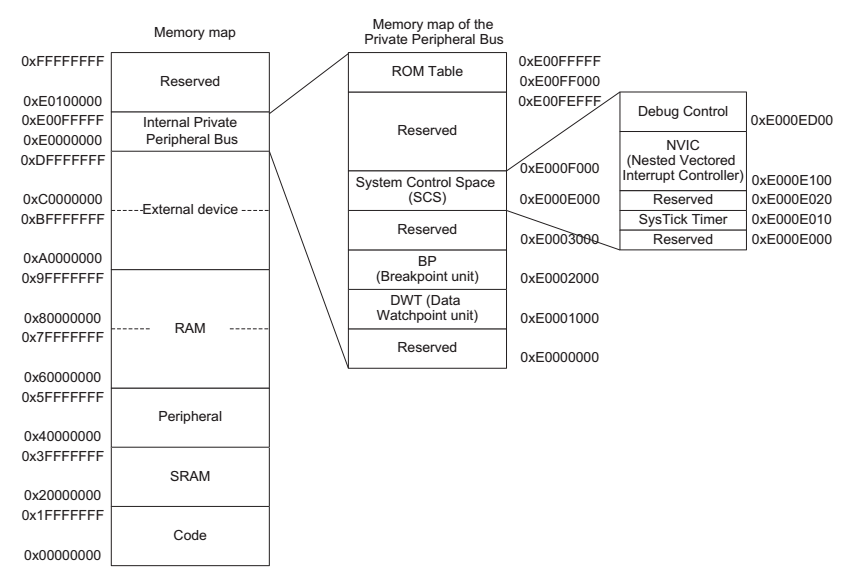

6.内部私有总线区域(0xE000 0000~0xE00F FFFF) 1MB。用于处理器内部的外设,包括中断控制器NVIC和调试部件,还有systick。不允许程序执行。

7.保留存储器空间 (0xE010 0000~0xFFFF FFFF) 511M用于保留。

上图为基于Cortex-M0+的stm32L053的存储器映射图。我们可以看到基本是与Cortex-M0内核是符合的。但是具体的分配具有很大的灵活性。

片上FLASH在0x0800 0000,SRAM在0x2000 0000。

IO口在0x5000 0000-0x5000 1FFF,占用了8K。

APB1上的器件基地址为0x4000 0000;

APB2上的外设基地址为0x4001 0000;

AHB上的外设基地址为 0x4002 0000。