1 CRG的SPEC参考

1.1 时钟设计需求

(1)生成AHB时钟,APB时钟,RTC时钟;(2)AHB最高时钟频率为98MHz;(3)APB时钟为AHB同步时钟,且可以配置AHB时钟的1/2,1/4,1/8;(4)RTC时钟单独控制时钟,时钟频率1KHz;(5)各外设时钟可以单独门控,满足低功耗要求。

1.2 时钟设计要点

(1)DFT可控,隔离,可观测。(2)上电工作外部参考时钟,PLL稳定后,时钟自动切换。(3)低功耗要求,在系统不工作时,时钟自动关闭。(4)各个外设时钟均能门控。

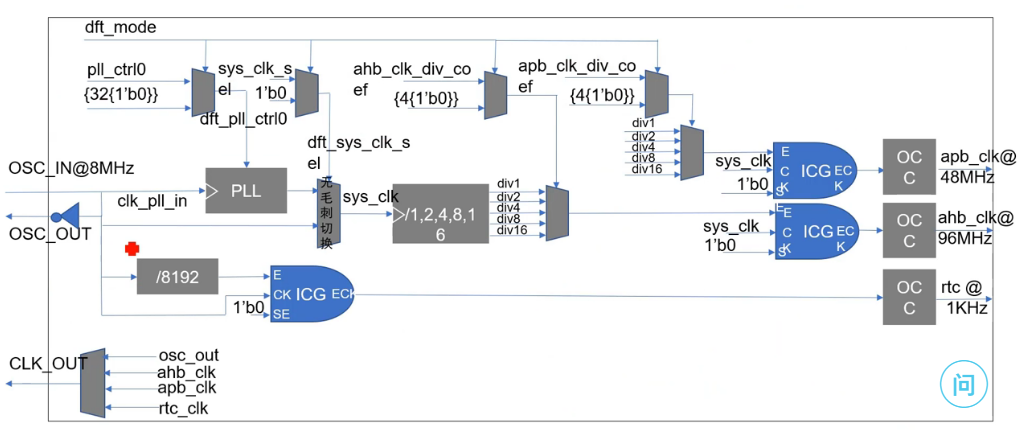

1.3 时钟设计电路

看上图,首先进来的是8M时钟,给PLL倍频。OSC_OUT是OSC_IN取反得到的,这是外部时钟要求的。经过无毛刺切换后,就产生sys_clk系统时钟,然后进入一个分频模块;分频之后的时钟进入ICG,产生apb和ahb时钟。这个ICG看做是一个buffer,对sys_clk做门控,时钟路径时钟是sys_clk系统时钟,注意这里出来是不是分频时钟,而是sys_clk出来的,分频时钟只是控制作用而已。

2 时钟的无毛刺切换

2.1 毛刺的产生

两个时钟频率可以彼此完全无关,或者它们可以是彼此的倍数。在任何一种情况下,都有可能在切换时在时钟线上产生毛刺。时钟线上的毛刺对整个系统是危险的,因为它可能被某些寄存器解释为捕获时钟边沿而被其他寄存器忽略。毛刺的处理分为两种,当时钟是彼此的倍数时是一种,完全无关的两个时钟处理又是一种。

2.2 倍数关系的时钟毛刺解决方案

着一篇文章很值得参考!

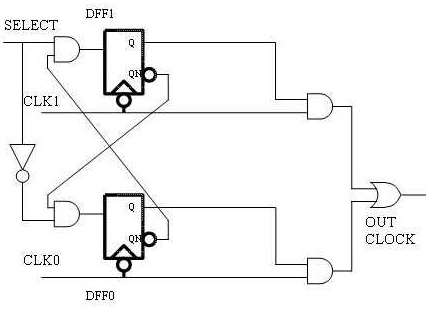

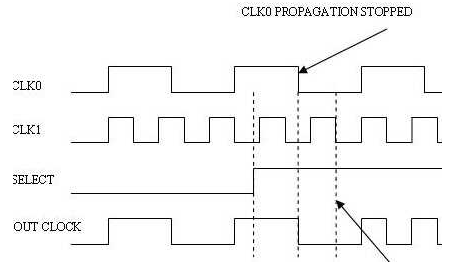

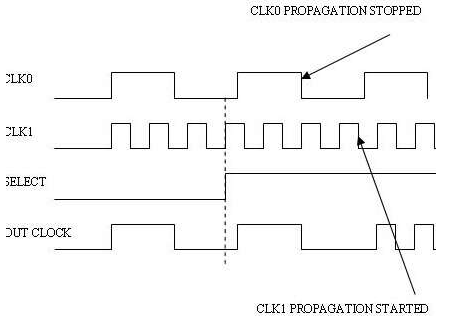

其原理是,先gating住之前选择的时钟,然后再放开将要选择的时钟。下图显示了防止源时钟相互倍数的时钟开关输出出现毛刺的解决方案。在每个时钟源的选择路径中插入一个负边沿触发的D触发器。

2.3 针对无关时钟源的毛刺保护

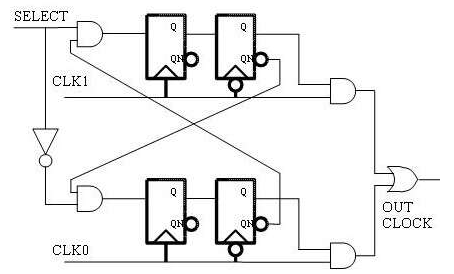

先前避免时钟开关输出处的毛刺的方法需要两个时钟源彼此的倍数,在该实现中没有处理异步信号的机制。当两个时钟源彼此完全无关时,异步行为的源可以是SELECT信号或从一个时钟域到另一个时钟域的反馈。同步器只是两级触发器,其中第一级通过锁定数据来帮助稳定数据,这一级可以用上升沿,也可以用下降沿,用上升沿是为了节省时间然后将数据传递到下一级,后一级的DFF必须使用clock下降沿,因为是用AND门进行gating。

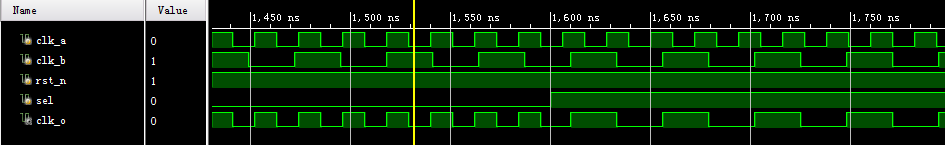

2.4 RTL代码

module clk_sw( input wire clk_a, input wire clk_b, input wire rst_n, input wire sel, output wire clk_o ); reg clk_a_en ; reg clk_b_en ; always @(posedge clk_a or negedge rst_n) begin if(~rst_n) clk_a_en <= 1'b0 ; else clk_a_en <= ~sel & ~clk_b_en ; end always @(posedge clk_b or negedge rst_n) begin if(~rst_n) clk_b_en <= 1'b0 ; else clk_b_en <= sel & ~clk_a_en ; end assign clk_o = (clk_a & clk_a_en) | (clk_b & clk_b_en) ; endmodule