数字后端 fix hold timing 的常见方法是垫 buffer 或者调 tree,其实还有一种修 hold 的方法: 插入 lockup latch

假设下图中的电路存在较大的 hold violation

为了修掉这条 hold,我们可以在data path 上插入一个 低电平有效的 latch

在 data path 上插入一个 latch 后,由于 latch 低电平期间保持透明,高电平期间则保持原值不变,所以相当于将数据向后延迟了半个周期,这样就不会再有 hold violation 了

这里插入的 latch 就 叫做 lockup latch,因为其功能就像是把数据锁定了半个周期一样

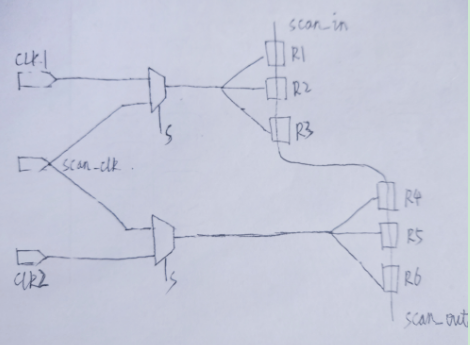

Lockup Latch 最常见的应用场景是在修 scan mode 下的 hold violation:

上图中的clk1 与 clk2 是两个相互独立的时钟域,做完cts 后 clk1 的 latency 较小, clk2 的 latency 较大;由于在scan mode 下所有的 reg 会串成一条 scan chain,所以在 scan mode 下, R3 与 R4 之间是需要 check timing,又因为二者 clock latency 相差较大,所以这条path 很可能出现较大的 hold violation,为了修掉这条 hold,如果我们直接在 R3 R4 之间垫buffer,可能需要垫很多buffer,很浪费,此时就可以考虑使用 lockup latch,使 R3 输出的数据向后延迟半个周期,这样应该就不会有 hold 问题了,可能有人担心:这样会不会导致 R3 到 R4 之间出现 setup 问题呢? 这个不用担心,因为在 scan mode 下时钟比较慢,时钟周期足够长,不太可能出现 setup violation。

|----------------------------------------|