喜大普奔,公司要评估用SOC做产品,我就自然而然的被安排了学习和评估的工作,于是,每天的工作就是开始研究soc了。其实,只要能静下心来学习,一切都还是能够弄出来的。

以前像个无头苍蝇一样到处乱撞,搞了两三个月没把fpga和arm给联通起来,尽然只是因为教程用的Quartus II13.1软件和我自己电脑上装的Quartus II14.1软件在生成dts时调用的一个文件不一样导致的。当然,这个只是外在原因,真正内在的原因还是因为内在对linux的恐惧,因为是零linux基础,所以全部linux下命令都是第一次接触,于是各种错误各种不通,最后就放弃了。但是,心里总是不愿就这么放弃了,总想学会这门新技术。于是前两天又花钱买了周立功的ARM9开发板,然后跟着他提供的教程慢慢学习。终于是能够简单的进行一些linux下的命令操作了,昨天再次上手DE1—SOC,终于成功的生成了preloader和DTS,并通过HPS控制了FPGA端的LED。

相信很多参加此次活动或者自学SOC的筒子也都有过我以上这段经历,这里,我愿意把我遇到的问题和解决方法提出来,希望那些还卡在这些问题的地方的筒子能够快速走出困境。

我此次学习是跟着友晶提供的培训教材一步一步来进行的,该培训教材中,使用的是Quartus II13.1的软件,而我在使用的时候,直接安装的Quartus II 14.1。而也正是这样一个选择,让我被坑了好几天,最终放弃沉寂了好久,直到昨天,在网友"微末凡尘"的指导下,才执行成功。

首先,在教材的第49页,在hps clock选项卡上,需要进行一下更改,具体我也是看了骏龙科技的一篇文章《在SoCEDS环境下编译和更新preloader和uboot程序的方法》才知道的,原文如下:

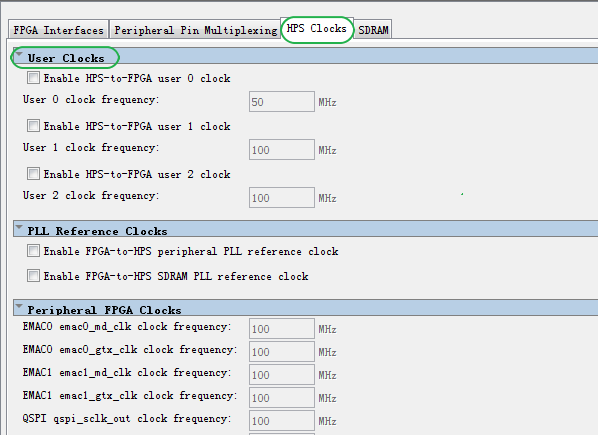

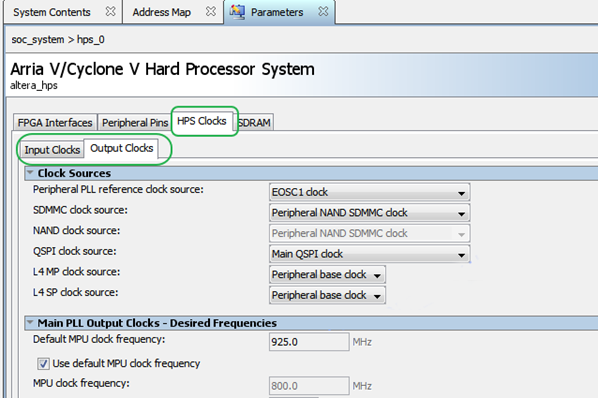

相对于13.0主要变化是有了HPS Clocks窗口分为了Input Clocks 和Output Clocks!对比如下图:

Quartus 13.0 HPS Clocks窗口

Quartus 14.0 HPS Clocks窗口

14.0软件中Cyclone V 器件MPU 默认时钟为925Mhz,而13.1版为800M。这里编译不改变MPU的Clock,所以去掉use default MPU clock frequency选项!不用改其他的选项,Clock即为800MHz。重新generate 关闭就好了。使用Quarut编译编译完成后会有hps_isw_handoff中的文件会更新,这些文件时连接HPS硬件配置与preloaderr软 件接口文件。

这里文中说的14.0,但是14.0和14.1在这一点上没有区别,因此,直接按照文中的内容操作即可。

第53页最后一行,说要求将pio_0重命名为led_pio,这里一定要注意并保持一致,否则生成dts时会报错。同理,button_pio也是一样,名字最好不要错。个人感觉,初学,尽量不要标新立异,尤其是对环境不熟的,否则都不知道死在哪里。

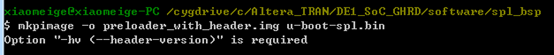

第83页最后一句话,我直接按照文档中的命令内容敲进去,会报错,提示我少了-hv参数,如下图所示:

这里我也不懂是怎么回事,既然说少了个参数,就加个参数呗,于是我将命令内容改为:

mkpimage –hv 0 –o preloader_with_header.img u-boot-spl.bin

然后就能成功了。

第85页,生成DTS的时候,这个地方是变化最大的一个地方,我就是因为这个地方,才被卡了很久。这页的最后一段,说生成dts需要的四个文件为

-

soc_system.sopcinfo

-

hps_clock_info.xml

-

soc_system_board_info.xml

-

Makefile

那么,如果我们直接使用这三个文件,用原来的Makefile文件来生成dts和dtb,都会报错,dts能够生成,但是有错误,dtb直接无法生成。原因就在于,在Quartus II14.1的软件中,第二个使用的不再是hps_clock_info.xml文件,而是hps_common_board_info.xml。这个文件我们可以在SOCEDS软件安装目录下的exampleshardwarecv_soc_devkit_ghrd 文件夹下找到,我的电脑中的绝对位置为

D:altera14.1embeddedexampleshardwarecv_soc_devkit_ghrd。

我们将其中的两个xml文件hps_common_board_info.xml、soc_system_board_info.xml和一个Makefile复制出来,粘贴到我们自己的工程目录下,并将原来的三个文件删除即可。再次make dts,就能够成功了,当然这个过程比较长,需要2到5分钟。然后,待dts生成完成后,再次make dtb,就很快,也能成功了。

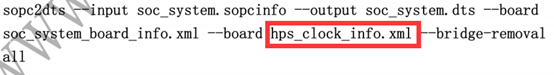

注意,如果按照第86页最后一段来自己敲命令进行生成dts,则需要将命令中对应的

hps_clock_info.xml替换为hps_common_board_info.xml。为了简便推荐大家直接使用"make dts"命令来操作。后面生成dtb的也是一样,直接使用"make dtb"命令就行了,详见教材88页最后一段。

自此,后面的就没有其他问题了,对着该教材一步一步的进行,最终都能运行出正确的结果。只是,在做de1_soc_sw_lab3中的实验时,原本提供的main.c文件里面使用的fpga端的led的名字叫pio_led,而我们的Qsys系统中命名为led_pio,因此直接使用该c文件生成可执行文件时会报错,需要将其中的第40行的"PIO_LED_BASE"改为"LED_PIO_BASE"。第59行的"PIO_LED_DATA_WIDTH"改为"LED_PIO_DATA_WIDTH"。然后就能生成成功了。

执行实验3生成的可执行文件,能够看到开发板上FPGA端的10个红色LED灯流水60次,然后停止。

好了,就写到这里,文字不够详细,若有疏漏或错误,欢迎各位指出。具体效果,就不上图啦。