偶然在 QQ 群里看到一个大佬发的 Modelsim 波形显示字符,闲着没事拿来玩玩,并将改良过程也整理一下。

一、字符点阵产生

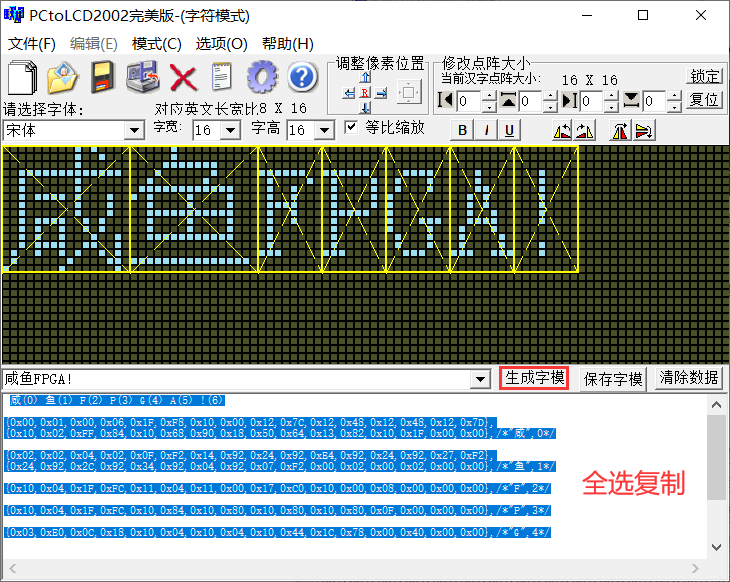

软件采用 PCtoLCD2002,打开后不需要设置,直接打字然后点击【生成字模】,然后复制产生的字模。

二、字模调整

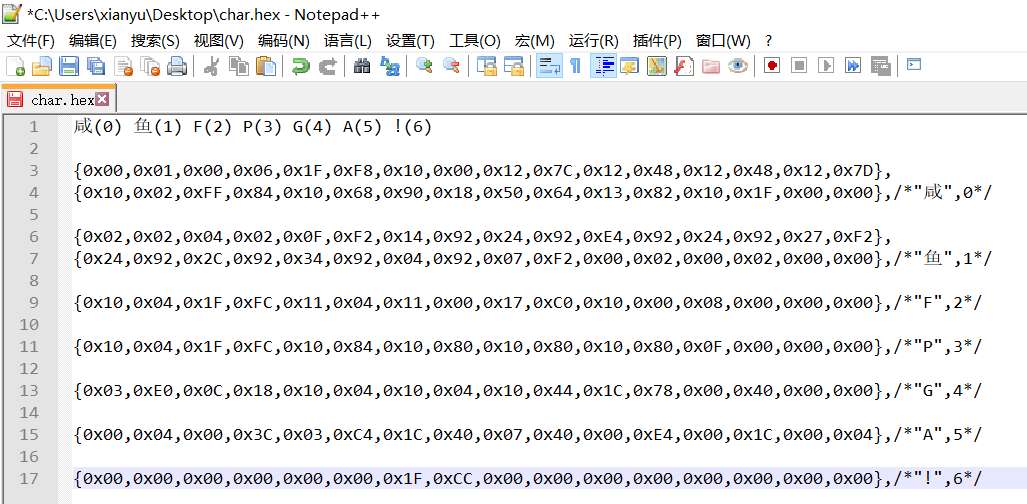

复制之后的字模如下所示:

将字模中的提示信息、标点符号、注释都删除。并且将相邻两个数据调整为一个数据,并将调整后的所有数据调整为一列,如下所示:

调整完后将该文件重命名并修改后缀为【char.hex】,供后面 Verilog 读取该文件。

三、代码设计

原文的设计有 2 个 Verilog 设计文件和 1 个 testbench 文件,我将其合并为 1 个,如下所示:

1 `timescale 1ns/1ps //时间精度 2 3 module char_display; 4 //========================< 信号 >========================================== 5 reg clk = 0 ; //时钟,初始为0 6 reg [15:0] ram[2**8-1:0] ; //数组 7 reg [15:0] cnt = 0 ; //计数器,初始为0 8 wire [ 7:0] rd_addr ; //读地址 9 reg [15:0] rd_data ; //数组读数据 10 wire [15:0] char ; //字符显示 11 //========================< 代码 >========================================== 12 //时钟 13 always #10 clk = ~clk; 14 15 //数组初始化,读取字符数据 16 initial $readmemh("char.hex", ram); 17 18 //数组读地址 19 always@(posedge clk) begin 20 cnt <= cnt + 1'b1; 21 end 22 23 assign rd_addr = cnt[15:8]; 24 25 //数组读数据 26 always @(posedge clk) begin 27 rd_data <= ram[rd_addr]; 28 end 29 30 //波形输出(rd_data已经有形状了,再把它加粗) 31 assign char = rd_data[15:0] & {16{clk}}; 32 33 34 endmodule

四、仿真波形

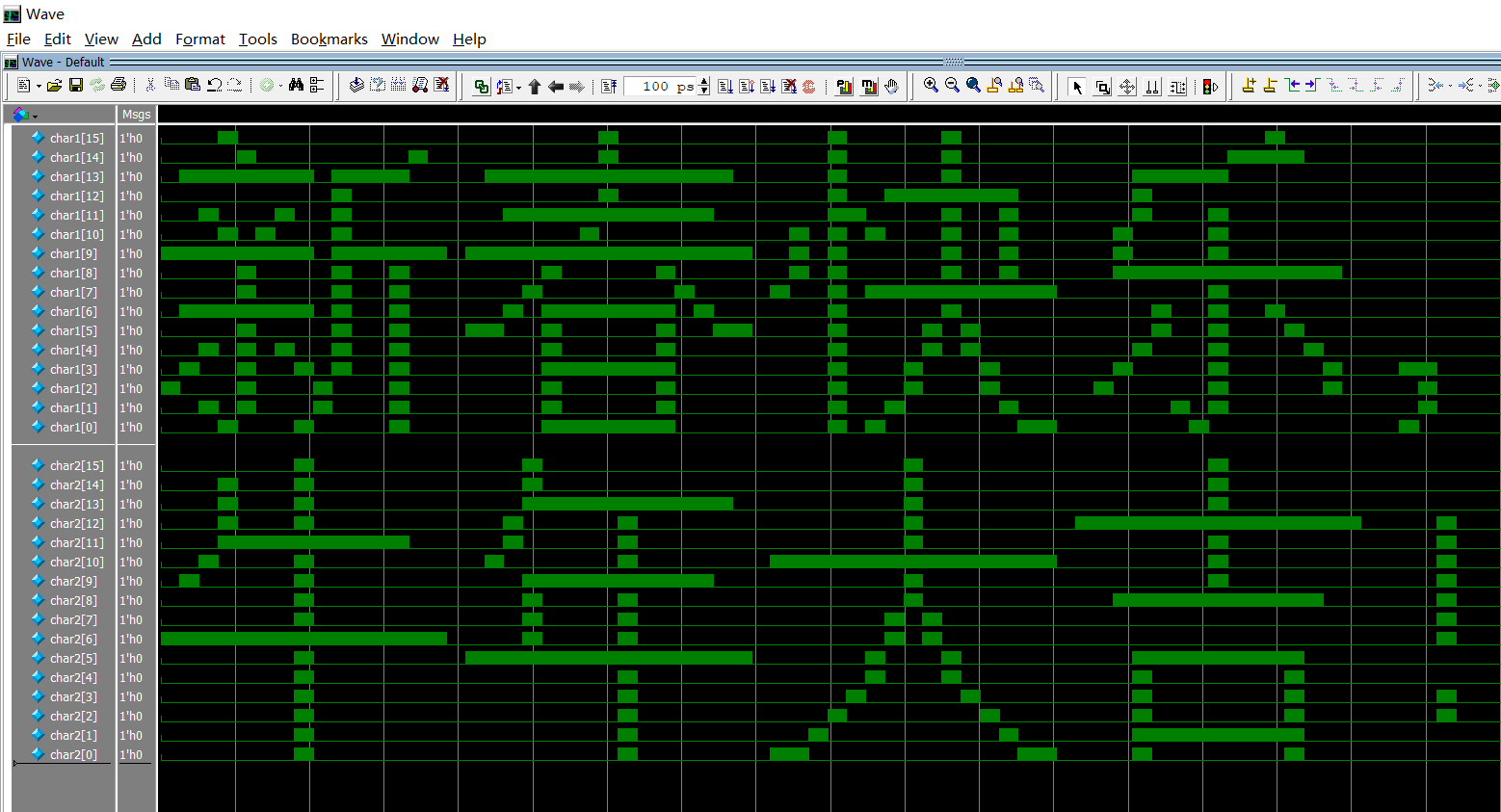

建立 Modelsim 工程并显示 char 信号的波形,展开 char 信号即可看到字符了。当然也可以写个脚本自动化仿真,脚本文件如下所示:

1 # ========================< 清空软件残留信息 >============================== 2 3 # 退出之前仿真 4 quit -sim 5 6 # 清空信息 7 .main clear 8 9 # =========================< 建立工程并仿真 >=============================== 10 11 # 建立新的工程库 12 vlib work 13 14 # 映射逻辑库到物理目录 15 vmap work work 16 17 # 编译文件 18 vlog *.v 19 20 # 启动仿真:10.7之前版本的仿真请将"-voptargs=+acc换成-novopt" 21 vsim -voptargs=+acc work.char_display 22 23 # ============================< 加载波形 >================================== 24 25 # 添加标签和波形 26 add wave -position insertpoint 27 {sim:/char_display/char[15]} 28 {sim:/char_display/char[14]} 29 {sim:/char_display/char[13]} 30 {sim:/char_display/char[12]} 31 {sim:/char_display/char[11]} 32 {sim:/char_display/char[10]} 33 {sim:/char_display/char[9]} 34 {sim:/char_display/char[8]} 35 {sim:/char_display/char[7]} 36 {sim:/char_display/char[6]} 37 {sim:/char_display/char[5]} 38 {sim:/char_display/char[4]} 39 {sim:/char_display/char[3]} 40 {sim:/char_display/char[2]} 41 {sim:/char_display/char[1]} 42 {sim:/char_display/char[0]} 43 44 # 跑400us 45 run 400us

最后的结果如下所示:

也可以发挥创造力,弄个两行的字符波形出来,只需要将关键代码多设置一份就行了。

五、工程链接

链接:https://pan.baidu.com/s/1kKI0d2TzDfh78Ed_RAMcAA

提取码:867g

参考资料:公众号《数字积木》