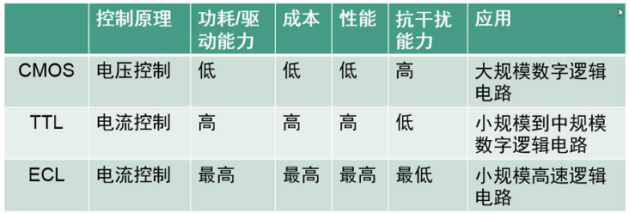

1、CMOS/TTL/ECL电路的比较

补充:CMOS和TTL电路的区别是什么?

- 结构:CMOS电路由场效应管,TTL由双极性晶体管构成。

- 电平范围:CMOS逻辑电平范围大(5~15V),TTL只工作在5V以下,因此CMOS噪声容限比TTL大,抗干扰能力强。

- 功耗与速率:CMOS的功耗比TTL小,但工作频率低于TTL。

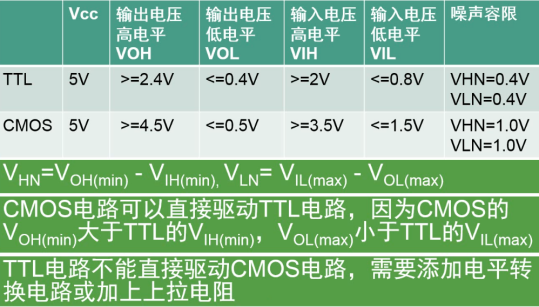

2、TTL和CMOS逻辑之间能互联吗?

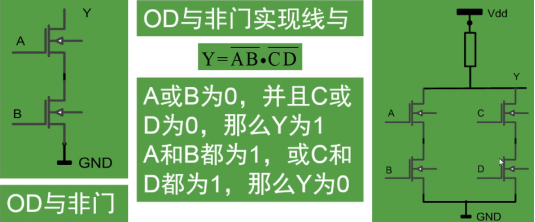

3、硬件电路如何实现线与功能?

线与:将两个门的输出信号并联实现“与”的功能。通常用OD来实现,同时在输出端口加一个上拉电阻。(OC门也可以线与)

注意:不接上拉电阻的话会造成短路烧坏电路。(例如IIC的SCL和SDA)

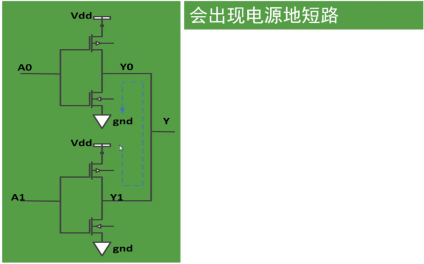

4、CMOS门为什么不能线与?

5、画出CMOS非们电压电流传输特性?

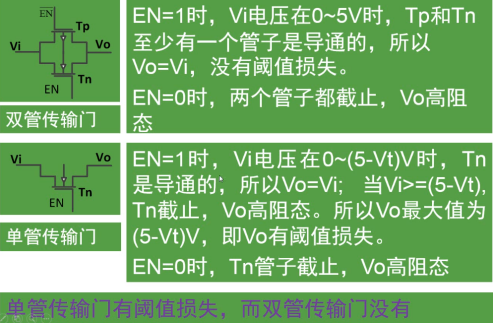

6、单管传输门和双管传输门的区别?

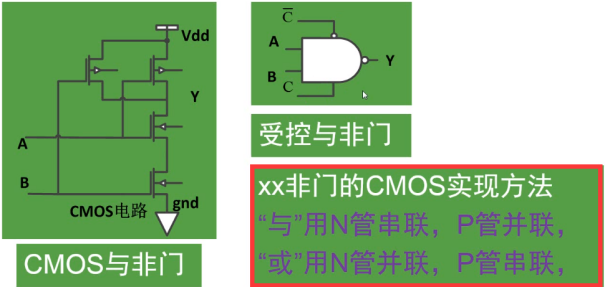

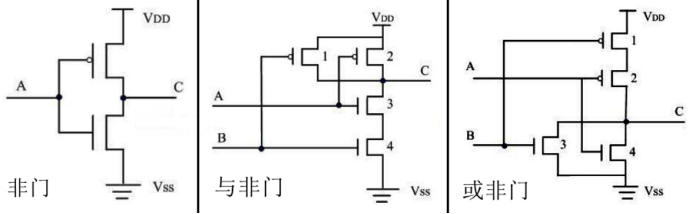

7、画出非门和受控非门的CMOS电路?

8、画出与非门和受控与非门的CMOS电路

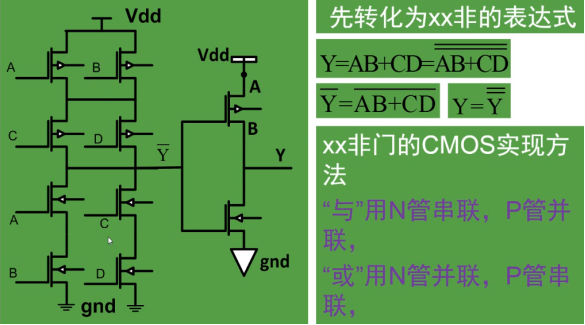

9、用PMOS和NMOS搭出Y=AB+CD的电路?

10、什么是NMOS、PMOS、CMOS?什么是增强型、耗尽型?什么是PNP、NPN?他们有什么差别?(仕兰微面试题目)

NMOS:这种类型的MOS管采用P型衬底,导电沟道是N型。

PMOS:这种类型的MOS管采用N型衬底,导电沟道是P型。

增强型与耗尽型的区别:

(1)原理不同:耗尽型在G端不加电压都存在导电沟道,而增强型只有在开启后,才会出现导电沟道。

(2)控制方法不一样:耗尽型UGS可以用正、零、负电压控制导通,而增强型必须使得UGS>UGS(th)才行,一般的增强型NMOS,都是正电压控制的。

11、描述CMOS电路中闩锁效应产生的过程及最后的结果?

闩锁效应是CMOS工艺所特有的寄生效应,严重会导致电路的失效,甚至烧毁芯片。 闩锁效应是由NMOS的有源区、P衬底、N阱、PMOS的有源区构成的n-p-n-p结构产生的,当其中一个三极管正偏时,就会构成正 反馈形成闩锁。避免闩锁的方法就是要减小衬底和N阱的寄生电阻,使寄生的三极管不会处于正偏状态。静电是 一种看不见的破坏力,会对电子元器件产生影响。ESD 和相关的电压瞬变都会引起闩锁效应(latch-up)是半导体器件失效的主要原因之一。如果有一个强电场施加在器件结构中的氧化物薄膜上,则该氧化物薄膜就会因介质击穿而损坏。很细的金属化迹线会由于大电流而损坏,并会由于浪涌电流造成的过热而形成开路。这就是所谓的“闩锁效应”。

在闩锁情况下,器件在电源与地之间形成短路,造成大电流、EOS(电过载)和器件损坏。

12、在CMOS数字设计中,为什么PMOS的尺寸通常高于NMOS的尺寸?

在PMOS中,载流子是空穴,其迁移率小于NMOS中的载流子,电子。这意味着PMOS比NMOS慢。在CMOS技术中,NMOS将输出下拉至地,PMOS将输出上拉至VDD,如果PMOS和NMOS的大小相同,则PMOS需要更长时间才能对输出节点充电。所有这些都是为了输出节点的上升时间和下降时间相等。

13、相同面积的CMOS与非门和或非门哪一个更快?

电子迁移率是空穴的2.5倍,运算就是用这些大大小小的MOS管驱动后一级的负载电容,翻转速度和负载大小的前一级驱动能力相关。为了上升延迟和下降延迟相同,PMOS需要做成NMOS两倍多大小。

载流子的迁移率,对PMOS而言,载流子是空穴,对NMOS而言,载流子是电子。

PMOS采用空穴导电,NMOS采用电子导电,由于PMOS的载流子的迁移率比NMOS的迁移率小,所以同样尺寸条件下,PMOS的充电时间要大于NMOS的充电时间长,在互补CMOS电路中,与非门是PMOS管并联,NMOS管串联,而或非门正好相反,所以同样尺寸条件下,与非门速度快,所以,在互补CMOS电路中,优先选择与非门。

14、为什么一个标准的倒相器中P管的宽长比要比N管的宽长比大?

和载流子有关,P管是空穴导电,N管是电子导电,电子的迁移率大于空穴,同样的电场下,N管的电流大于P管,因此要增大P管的宽长比,使之对称,这样才能使得两者上升时间下降时间相等、高低电平的噪声容限一样、充电放电的时间相等。

15、CMOS反相器电路由(B)器件组成

A、一个NPN管和一个PNP管 B、一个NMOS管和一个PMOS管

C、两个NMOS管 D、一个NMOS管和NPN管

16、画出AB+C的CMOS电路的晶体管级电路图?

这类问题无疑例外都是一样的解法,算式化成非门、与非门、或非门形式即可画出。

(1)算式分析Y=AB+C=((AB)’C’)’;

(2)AB输入与非门;

(3)C输入反相器

(4)(2)(3)结果再输入与非门

画电路图的时候,为了节省时间,可以用简便画法,是不会扣分的,如下所示:

17、CMOS的功耗组成是什么样的?

功耗组成:动态功耗和静态功耗组成;

1、动态功耗:开关功耗和短路功耗;

开关功耗:电路在开关过程中对输出节点的负载电容充放电所消耗的功耗。

短路功耗:电源到地的直流导通电流

2、静态功耗:主要是漏电流引起的功耗

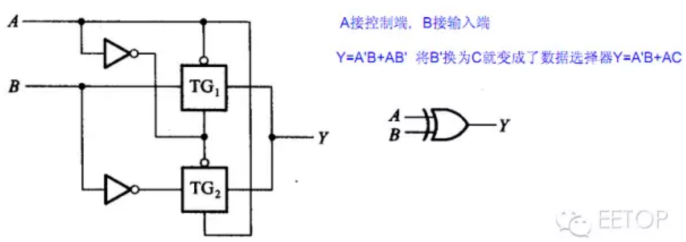

18、画出CMOS的图,画出tow-to-one muxgate.?

Y=SA+S’B 利用与非门和反相器,进行变换后Y=((SA)’*(S’A)’)’,三个与非门,一个反相器。也可以用传输门来实现数据选择器或者是异或门。

19、提高CMOS场效应管频率的方法有哪些?

(1)减小沟道长度;

(2)增大沟道表面的电阻迁移率;

(3)减小栅电容;

20、CMOS反相器的功耗主要包括哪几部分?分别于哪些因素相关?

P_dynamic 是电路翻转产生的动态功耗

P_short是P管和N管同时导通时产生的短路功耗

P_leakage 是由扩散区和衬底之间的反向偏置漏电流引起的静态功耗

(1)静态功耗:CMOS反相器在静态时,P、N管只有一个导通。由于没有Vdd到GND的直流桐庐,所以 CMOS的静态功耗应该等于零。但实际上,由于扩散区和衬底的PN结上存在反向漏电流,所以会产生静态功耗。

(2)短路功耗:CMOS电路在“0”和“1”的转换过程中,P、N管会同时导通,产生一个由Vdd到VSS窄脉冲电流,由此引起功耗

(3)动态功耗:C_L 这个CMOS反相器的输出负载电容,由NMOS和PMOS晶体管的漏扩散电容、连线电容和扇出门的输入电容组成。

21、CMOS管的含义是什么?(哈哈我同学被问到过)

互补金属氧化物半导体型场效应管