之前的博客详细介绍了 VGA 的原理和基本使用,这次换成 HDMI,增加一个技能点。

一、HDMI 基本介绍

二、HDMI 图像发送原理

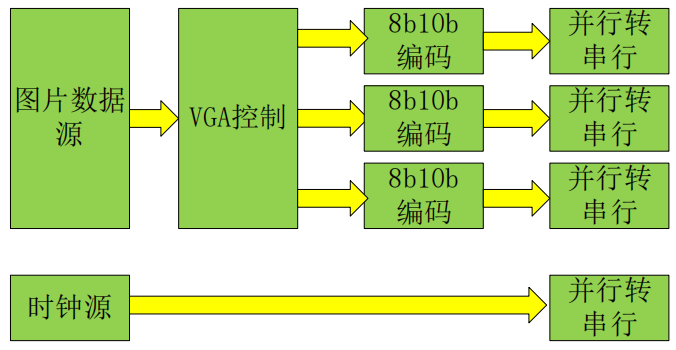

HDMI视频发送包含三个部分,VGA控制时序,8B/10B编码,并串转换,再将串行数据转换成一对差分信号传输到FPGA的引脚。总体框图如下图所示,由VGA控制器将图片源传来的数据转为R、G、B三个通道,每个通道的数据位宽均为8bit,然后由8B/10B编码码模块将8bit数据转为10bit,此目的主要是为了保证直流平衡,最后由并行转串行模块将10bit数据转成串行数据,再有单端转差分模块,将数据一对差分信号输出到FPGA的引脚端时钟源不需要进行8B/10B编码,可以由固定的数据代替,即10’b11111_00000。

三、HDMI 模块构成

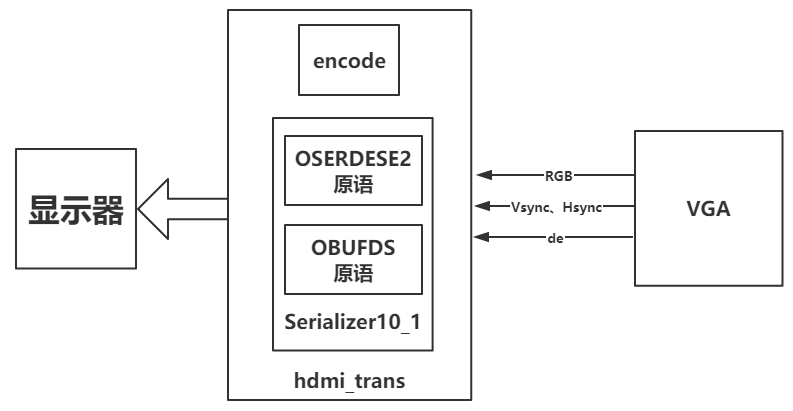

HDMI 模块可以封装成一个独立模块方便后面的使用。如图所示:

1、VGA模块

之前的博客已经有详细叙述了,直接拿来用即可,注意根据分辨率不同,需要更改一下参数。

2、hdmi_trans模块

设计一个专门的 VGA 转 HDMI 模块,封装一下 8B/10B 编码模块和并转串差分输出模块,后面用起来就方便多了。

(1)8B/10B编码:encode

8B10B 编码是可以从 Xilinx 官网下载到此模块,模块名为 encode,此模块把 8 比特的数据进行从新映射为 10bit 数据,防止连续的 0 和 1 出现导致直流不平衡造成误码率升高。

//========================================================================== //== encode 例化,RGB三个通道 //========================================================================== encode inst_encode_red ( .clkin (clk1x ), .rstin (sysrst ), .din (vga_r ), .c0 (1'b0 ), .c1 (1'b0 ), .de (vga_de ), .dout (dored ) ); encode inst_encode_green ( .clkin (clk1x ), .rstin (sysrst ), .din (vga_g ), .c0 (1'b0 ), .c1 (1'b0 ), .de (vga_de ), .dout (dogreen ) ); encode inst_encode_blue ( .clkin (clk1x ), .rstin (sysrst ), .din (vga_b ), .c0 (vga_hsync ), .c1 (vga_vsync ), .de (vga_de ), .dout (doblue ) );

(2)并转串差分输出模块:Serializer10_1

① 并转串模块:OSERDESE2原语

详细介绍见Xilinx官方提供的UG768手册。

OSERDESE2 原语模型:

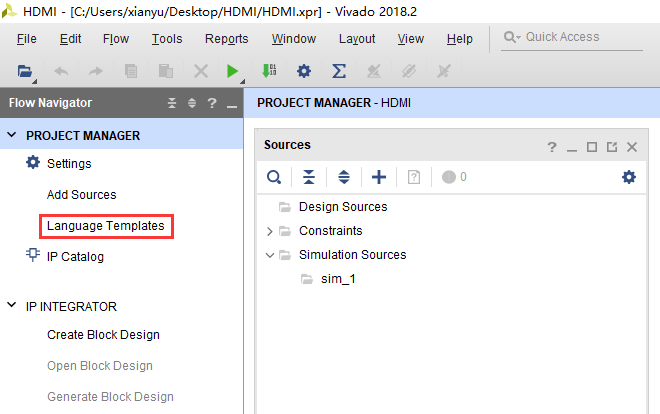

OSERDESE2 获取途径:

OSERDESE2 级联:

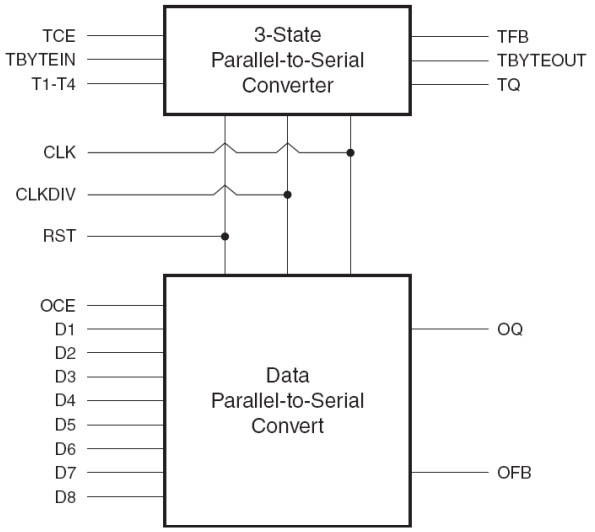

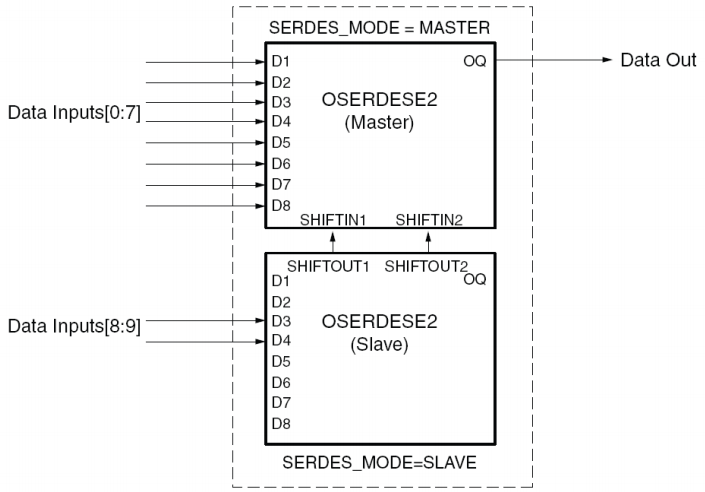

OSERDESE2原语的文档中介绍有:该原语可以进行8:1、10:1、14:1转换,当进行8:1转换的时候,采用一个原语即可,当采用10:1或者14:1转换的时候,需要采用两个原语级联的方式。我们需要将10bit数据进行串行化,因此根据文档说明,我们需要使用两个OSERDESE2原语进行级联,级联后的框图如下图所示。OSERDESE2 原语的 master 端承接 10bit 数据的低8位,OSERDESE2 原语的 slave 端的D1,D2不使用,D3 和 D4 承接10bit数据的高 2bit,(若是14:1则可以继续使用D5,D6,D7,D8,依然不使用D1,D2)。并将 slave 的输出 SHIFTOUT1, SHIFTOUT2 连接到 master 的 SHIFTIN1, SHIFTIN2,输入的 10bit 数据将会按照由低位到高位的顺序从 DataOut 端输出。

②差分输出模块:OBUFDS原语

详情见Xilinx官方提供的 UG471 手册。

OBUFDS原语模型

OBUFDS获取途径:

差分输出:

最后将串行的数据输入到 OBUFDS 原语的输入端,转换成对应的差分进行输出到 FPGA 引脚端即可。

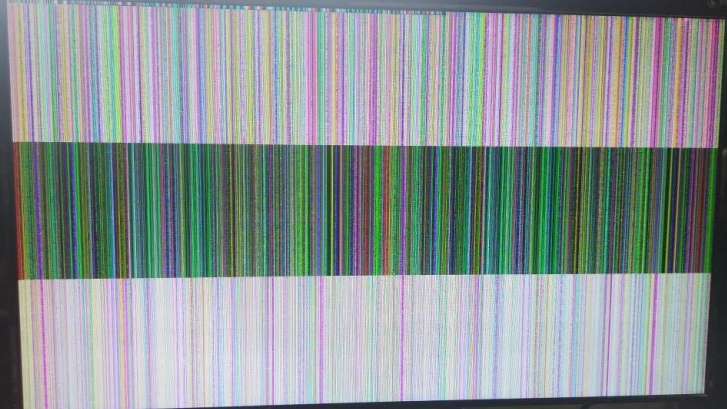

四、上板现象

如果成功,那么 HDMI 接口的屏幕会显示乱序的彩条,表明此次实验设计成功。

参考资料:威三学院FPGA教程