关于setup/hold

- 关于setup/hold,在整个LPS流程和DFV流程中都会碰到,可以讲是时序的核心问题;

- 本文针对setup/hold的产生原因和实质,做一个深入的分析和总结;

- Setup/hold属于时序设计中的基本问题,属于必须掌握的知识点;

- 希望对大家的面试和工作有帮助;

- 如有疑问,欢迎指正(请加xgcl_wei微信号联系)。

Setup/Hold基本定义

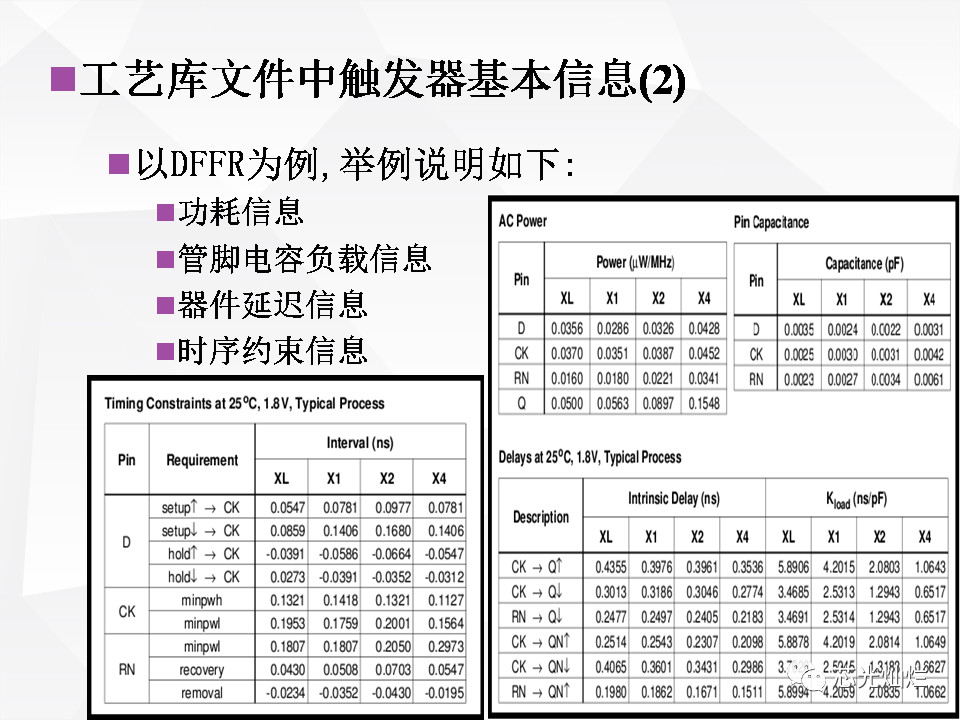

- 【Setup time】the minimum amount of timebefore the clock’s active edge that the data must be stable for it to be latchedcorrectly.(建立时间就是时序器件有效沿到来之前数据必须稳定的最少时间,建立时间违规会造成数据捕获出错)

- 【Hold time】 the minimum amount of timeafter the clock’s active edge during which data must be stable.(保持时间是时序器件有效沿之后数据必须保持稳定的最少时间,保持时间违规会造成数据在器件内保存出错)

经验总结

- Setup和hold属于时序中的基本问题,必须熟练掌握

- 要学会画波形图和时序图,时序是ASIC工程师沟通的桥梁

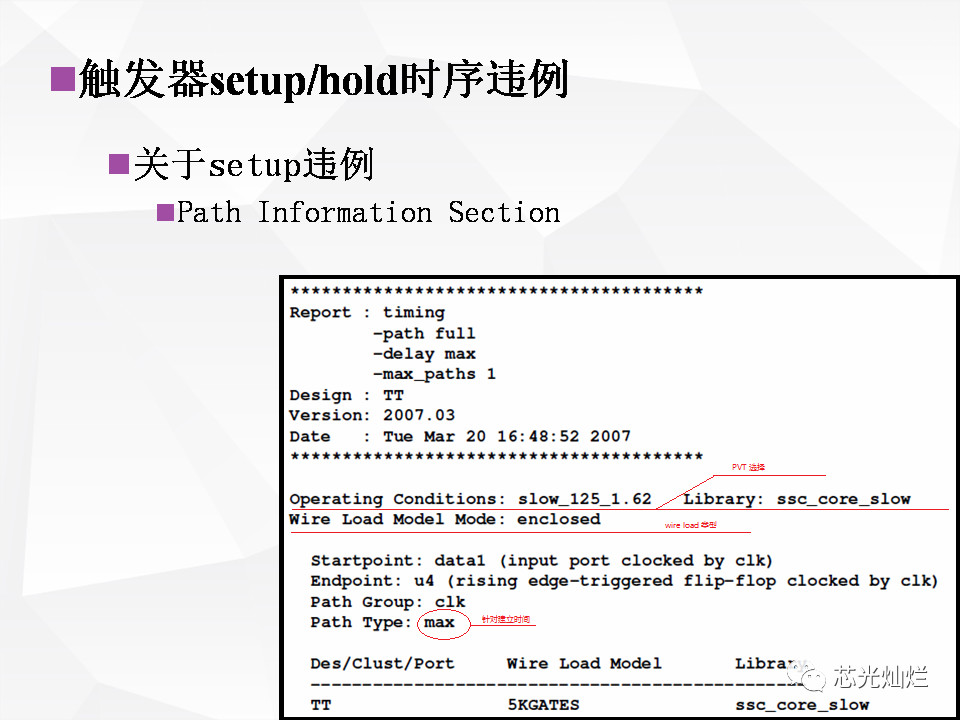

- 在严格定义和区分PVT( operating condition)的条件下讨论setup/hold才有意义

- 在严格定义约束文件(合理的DRC)的条件下讨论setup/hold才有意义

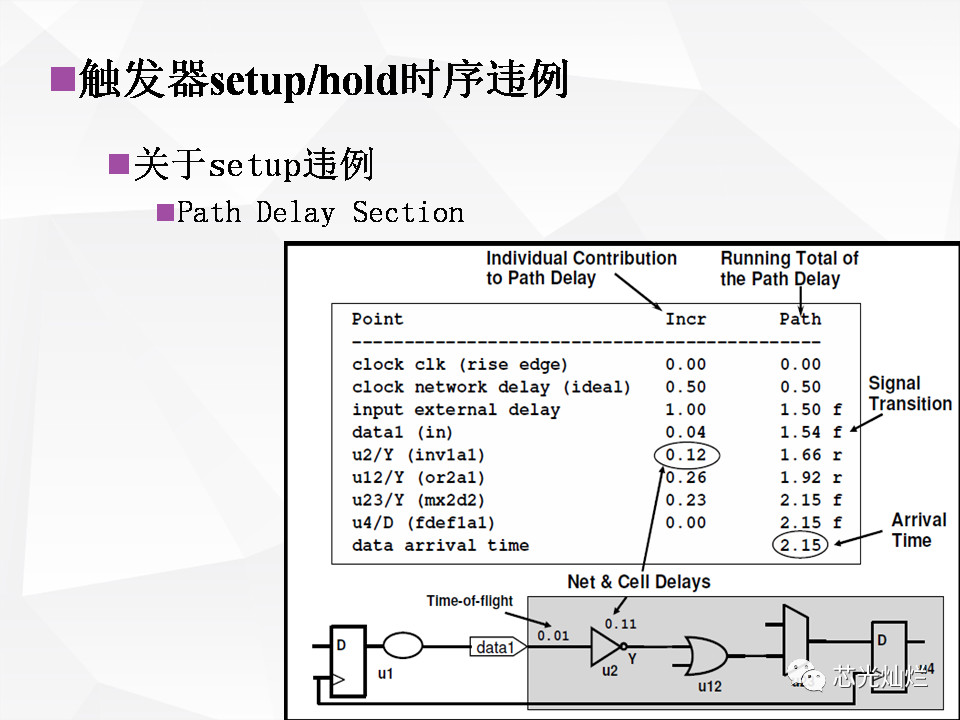

- 一般来说Setup 针对max corner,违例一般表示速度太慢

- 一般来说Hold 针对min corner,违例一般表示速度太快

- 相对来讲,setup难修,hold容易些

- Setup 难满足的,hold一定没有问题(请用心体会这句话)