https://blog.csdn.net/CrazyUncle/article/details/86164830

主要区别

共同点

1、任务和函数必须在module内定义和调用

2、在任务和函数中不能声明wire

3、所有输入/输出都是局部寄存器

4、任务/函数执行完成后才返回结果。例如,若任务/函数中有forever语句,则永远不会返回结果

任务

1、通常用于调试,或对硬件进行行为描述

2、可以包含时序控制(#延迟,@, wait)

3、可以有input,output,和inout参数

4、可以调用其他任务或函数

函数

1、通常用于计算,或描述组合逻辑

2、不能包含任何延迟;函数仿真时间为0

3、至少含有一个input参数并由函数名返回仅一个结果

4、可以调用其他函数,但不能调用任务

测试代码

`timescale 1ns / 1ps

module task_and_function(

);

reg [1:0] a;

reg [1:0] b;

reg clk;

reg [2:0] sum;

reg [2:0] sub;

reg [2:0] sum_func;

reg [31:0] factorial_res; // 阶乘结果

initial begin

clk = 0;

a = 0;

b = 0;

sum_func = function_1(a,b); //第一次调用函数计算和

task_1(a,b,sum,sub); //第一次调用任务计算和和差

@(negedge clk);

a = 2;

b = 1;

sum_func = function_1(a,b); //第二次调用函数计算和

task_1(a,b,sum,sub); //第二次调用任务计算和和差

factorial_res = factorial(3); //调用阶乘函数

end

always #20 clk = ~clk;

//============ 任务和函数的共同点 =========

/*

任务和函数必须在module内定义和调用

在任务和函数中不能声明wire

所有输入/输出都是局部寄存器

任务/函数执行完成后才返回结果。

例如,若任务/函数中有forever语句,则永远不会返回结果

*/

//============ 任务 =========

/*

1、通常用于调试,或对硬件进行行为描述

2、可以包含时序控制(#延迟,@, wait)

3、可以有input,output,和inout参数

4、可以调用其他任务或函数

*/

task task_1;

input [1:0] a;

input [1:0] b;

output [2:0] sum;

output [2:0] sub;

reg [1:0] i;

begin

for(i=0;i<=2;i=i+1) begin

@(posedge clk);

$display("i=%d",i); // 经历3个上升沿出结果

end

sum = a + b;

sub = a - b;

end

endtask

//============ 函数 =========

/*

1、通常用于计算,或描述组合逻辑

2、不能包含任何延迟;函数仿真时间为0

3、至少含有一个input参数并由函数名返回仅一个结果

4、可以调用其他函数,但不能调用任务

*/

function [2:0] function_1;

input [1:0] a;

input [1:0] b;

begin

function_1 = a + b; // 延迟为0

end

endfunction

// 阶乘函数

function [31:0] factorial;

input [3:0] opa;

integer i;

begin

factorial = 1;

for(i=2;i<=opa;i=i+1)

factorial = factorial * i;

end

endfunction

endmodule

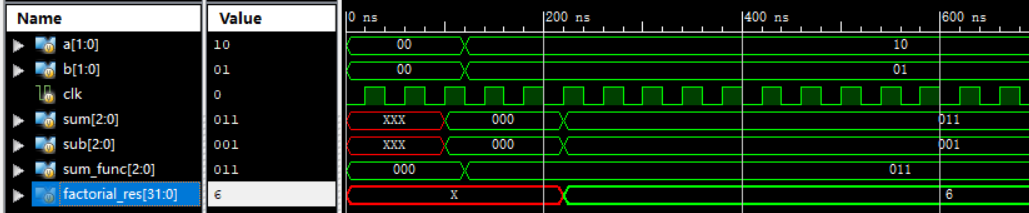

测试波形