逻辑综合工具Design Compiler使用教程

图形界面design vision操作示例

逻辑综合主要是将HDL语言描述的电路转换为工艺库器件构成的网表的过程。综合工具目前比较主流的是synopsys公司Design Compiler,我们在设计实践过程中采用这一工具。Design compiler有两种工作模式,一种是tcl模式,另一种为图形模式。在设计中为增强直观性,采用图形界面design vision。TCL命令行模式可在设计过程中摸索熟悉,并使之成为习惯。tcl模式在启动工具之前,准备工作有四项:设计的HDL源文件、采用的工艺库文件、设计的约束文件、工具的启动文件。图形界面模式最少需要前两项,这里不作多说明。

1. 启动工具

登陆Linux之后进入的目录即是用户的家目录,在家目录下建立dcLab作为本次实验dc的操作主目录。在dcLab目录下,建立设计存放目录如source、约束文件目录如constrn、输出网表文件目录ntlst、报告输出目录rpt、log文件目录log、dc启动目录work,等等。

实验室中的工作站存放有umc公司和tsmc公司的0.18um标准单元库的所有文件,存放在目录:/usr/eda/designKit/下面,设计过程中需要查找的话注意路径与示例中的图片上所示路径稍有不同。

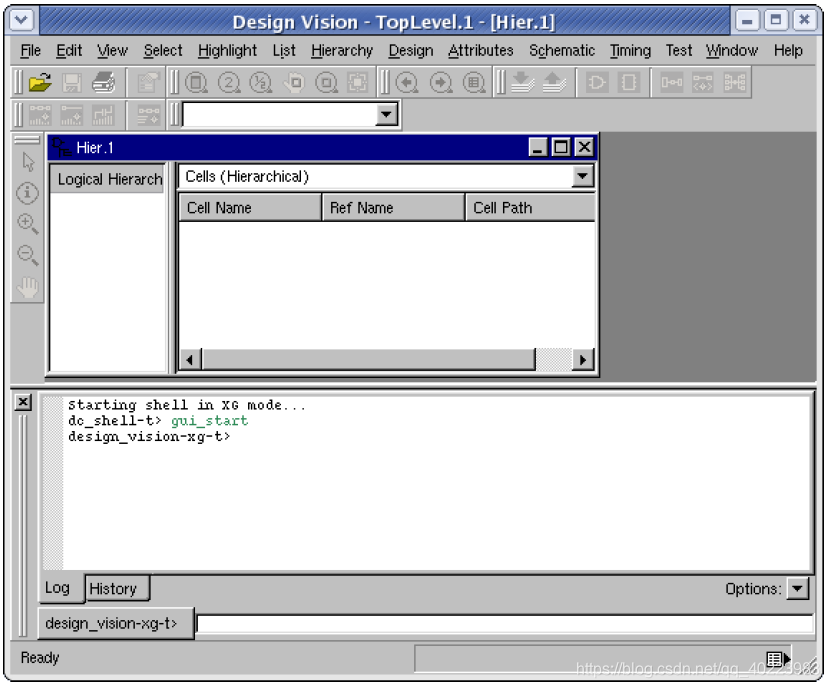

Design compiler工具在工作站中已经安装完毕,且用户的环境变量和license也已设置完成,登录之后直接启动工具即可。如果打开终端之后无法启动工具,可能就是license没有启动,需要首先采用命令:start_slic启动license,然后design vision才能正常开启与工作。建立相关的工程目录之后,进入本次实验的工作目录:~/dcLab/work后,采用启动命令:design_vision&,启动工具后相应的界面如下图1所示。

在该界面中,最上方为菜单项和工具栏,用于设计过程中的各项操作。当窗口中选中不同的对象时,不同的菜单项和工具项会被激活。工具栏下面就是主窗口,用于显示不同的设计对象、各种报告等。再下方为log/history窗口,log

页面显示操作响应,history界面回显菜单操作相应的tcl命令,操作过程中一定要对照查看,尽快熟悉tcl模式。最下方有design_vision-xg-t提示的就是tcl命令输入的位置,可以尝试将history页面的回显键入,查看响应。

图1 design vision启动界面

启动工具之后就可以工作了,主要可分为四部分内容:对工程进行启动项设置、对设计进行面积/功耗/时序/环境/drc等约束、对设计进行综合、查看报告并保存结果。

2. 配置工程启动文件

工具启动之后,需要设置相应的工程启动文件,用于设定搜索路径、相关库文件等内容,对应工作目录下的.synopsys_dc.setup文件(该文件应该位于工具启动目录~/dcLab/work下,dc启动过程中会自动读取该文件的内容用来配置工程启动项。

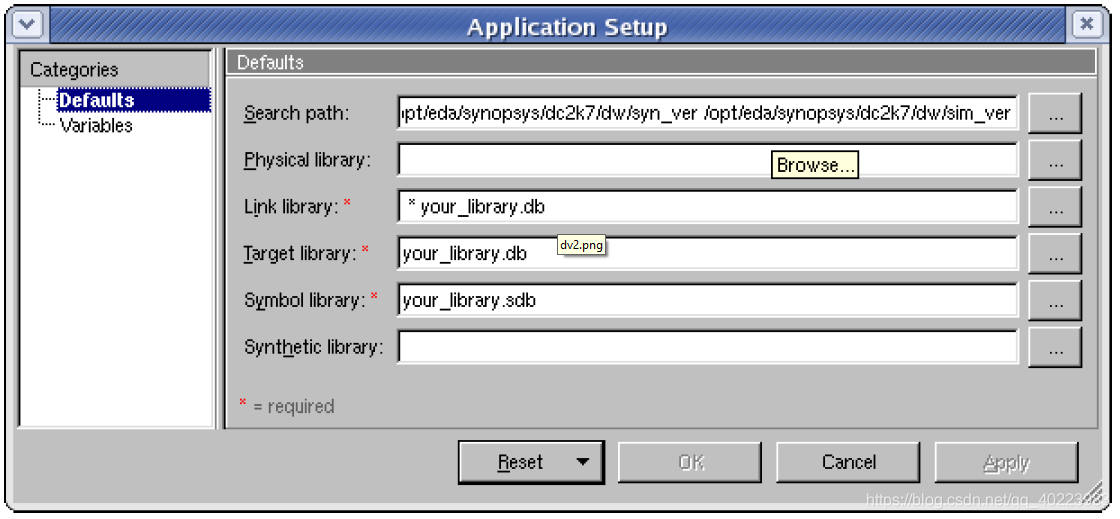

我们此时假设该文件不存在,当设置完成之后,可以将之保存,以后重启工具就可以不必设置了)。选择菜单项File—>Setup…,出现Application Setup窗口,如下图2所示。启动项相关的内容就在该表项中设置,用户可以直接填入相关内容,或者点击各栏右侧的查找按钮(标有…的小框)找到相应路径或

者文件的位置。

图2 setup设置窗口

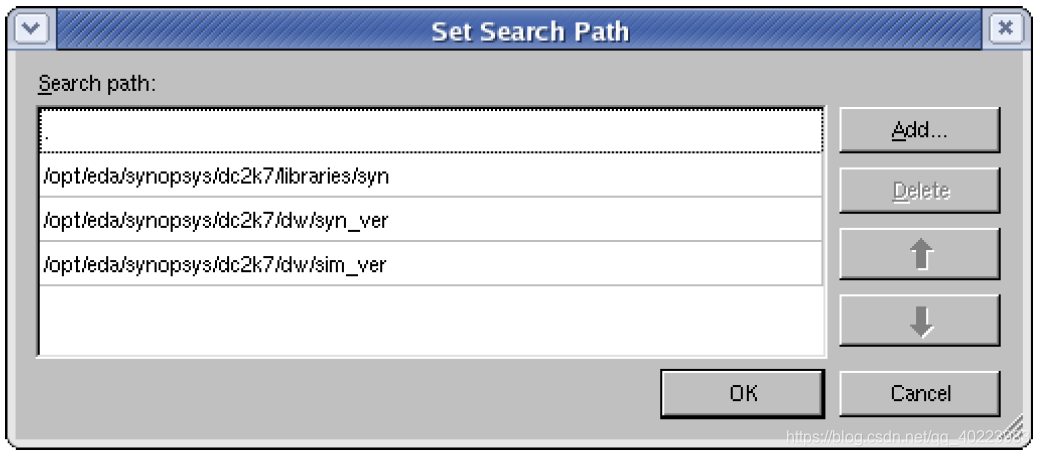

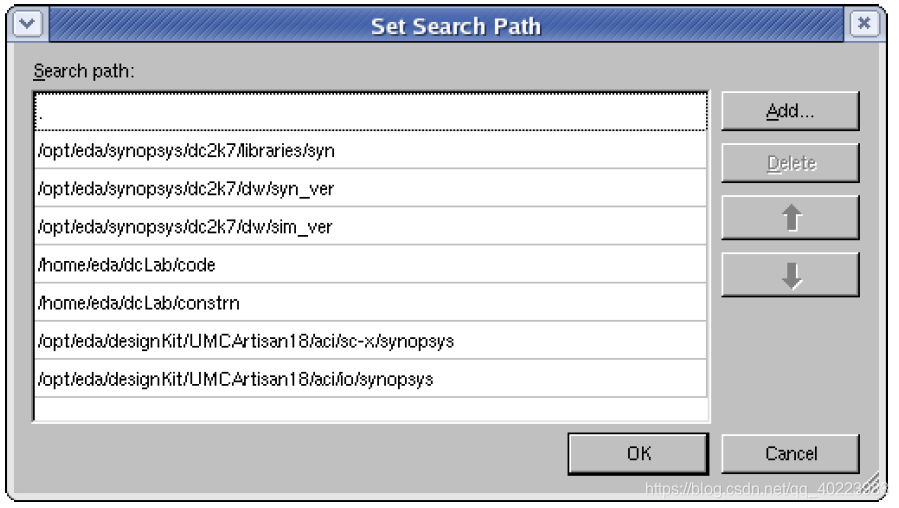

在该窗口中可以看到打有红星()标号的项目是必须设置的,但是一般填上四项:search path、Link library、Target library*、symbol library*。首先来设置搜索路径,该项主要用来指明设计中工具所需文件的路径,应该包括源代码文件路径、工艺库文件(如果源代码有pad,则也应该包括pad库文件所在路径)、工具提供的中间库文件(gtech、designWare)路径、以及操作过程中需要读取的中间文件所在路径等。点击search path条目右侧的查找按钮,就会出现set search path 表格窗口,如下图3所示。

图3 search path设置窗口

表格窗口已有的几项保留不动,其中第一项的点符号(.)表示当前工作目录,其余3项为工具提供的通用(gtech)库、ip单元库(design ware)以及符号(symbol)库和仿真模型库所在位置。点击Add…按钮,添加搜索路径(注意

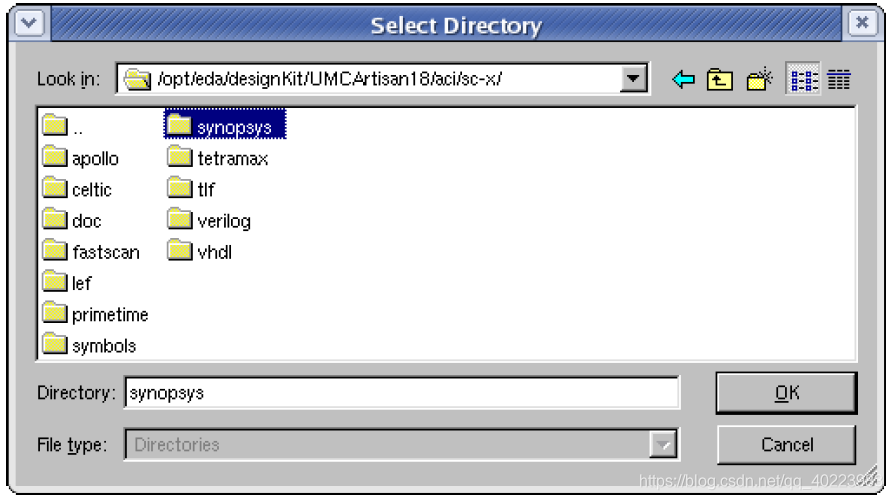

工作站上的软件工具、库文件均存放在/usr/eda目录下,与本例位置/opt/eda/稍有不同),如下图4所示。

图4 添加search path窗口

选择标准单元工艺库所在的目录,点击OK完成一条搜索路径的设置,回到图3 界面,此时表格窗口中会多出一项刚刚添加的路径。同样,点击Add…按钮添加其余的搜索路径:symbol所在路径、设计代码所在路径、约束文件所在路径、io工艺库所在路径等。完成路径设置后,图3 所示的search path设置窗口会变成如下图5所示。点击OK按钮完成set search path工作。

图5 完成search path的表格窗口

以上工作对应的tcl命令:set search_path “path”,其中path内容就是上

述的路径(如”…/code …/constrn /usr/eda/designKit/umn18/sc-x/synopsys”)。

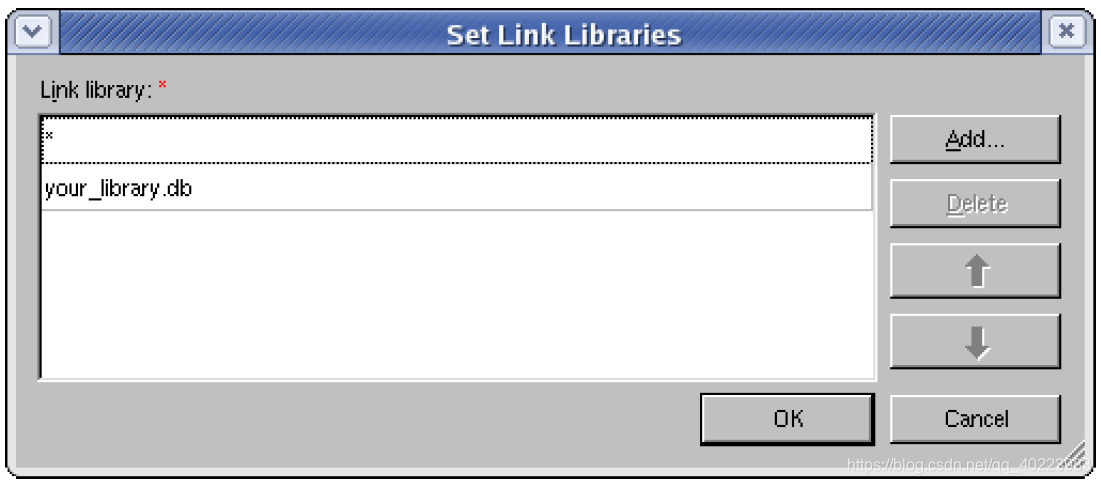

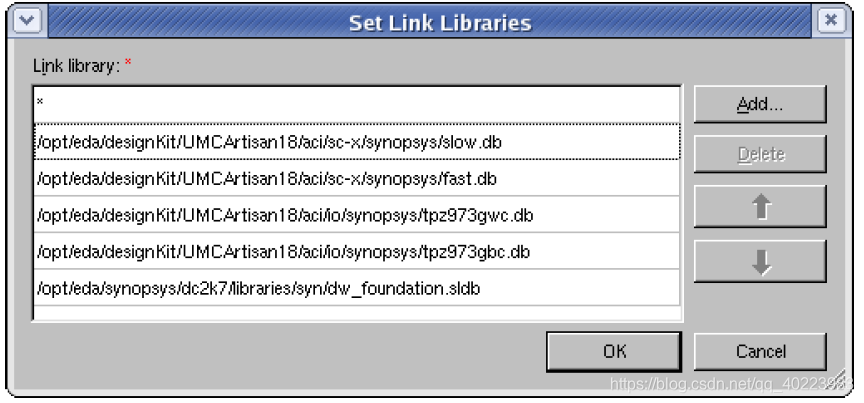

完成搜索路径的设置后,要进行工艺库相关的文件配置。其实配置好搜索路径后可以直接将相应的库文件写入对应的表格项,同一项中各文件中间用空格分开即可。这里为了熟悉工具,仍然逐项查找填写。在图2界面中,点击Link library右侧的查找按钮,出现Set Link Libraries的表格窗口,如下图6所示。

图6 链接库的表格窗口

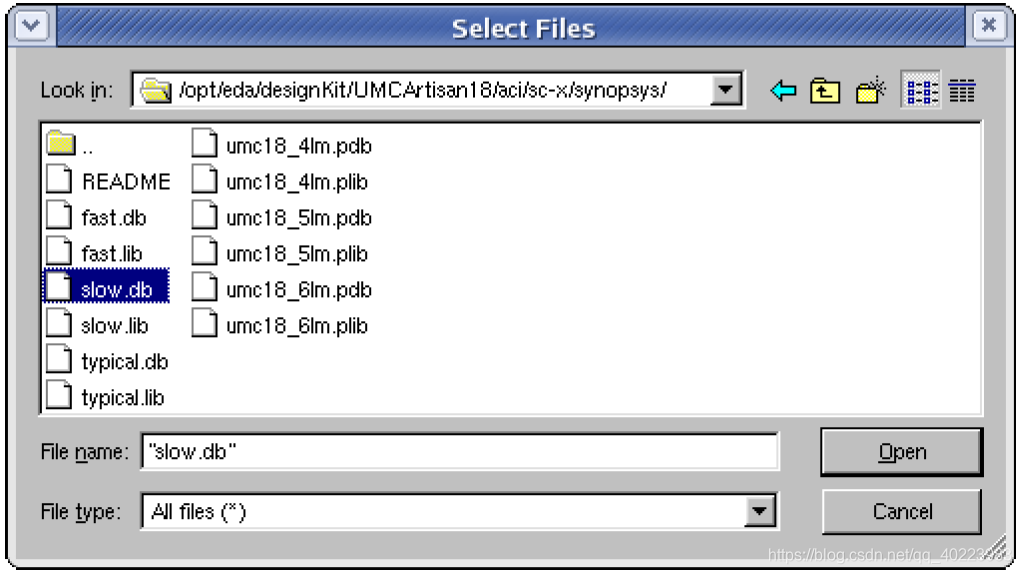

在上图中第一项不要改动,表示的是链接对象为当前内存。同上面设置search path一样,点击Add…按钮,查找库文件(注意工作站上的路径位置与本例不同),出现的界面如下图7所示。

图7 链接库的查找与选择

选中库文件后(注意link library和后面的target library采用的是synopsys的数据库文件格式db或者ddc,该文件是二进制格式;欲了解其内容可以察看

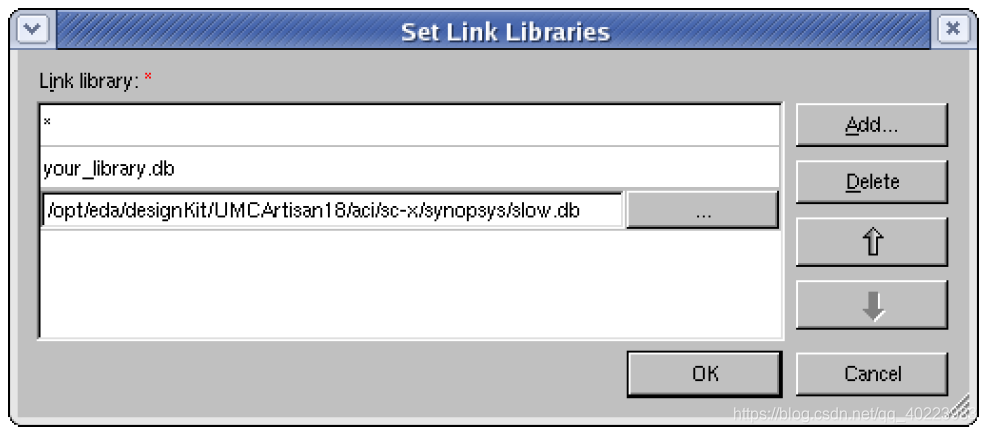

相对应的lib文本文件,试着读一下会了解更多),点击open按钮,回到图6的界面,其中增加了一项刚刚选择的库文件,如下图8所示的界面,至此完成一个库文件的设定。

图8 选定slow.db链接库

在标准单元库中选定slow.db和fast.db两个库文件,io单元库中也一样。一般在逻辑综合中最大延时是最重要的约束,因此也可以直接采用slow或者worst case库,而不标明fast或者best case库。本例中将其加上,主要用于对照时序报告察看二者的区别。

设置完成链接库之后,形成如下图9所示的表格图窗,其中最后一项为工具自带的design ware IP库,用于复杂功能逻辑优化(?)。

图9 链接库文件选定图窗

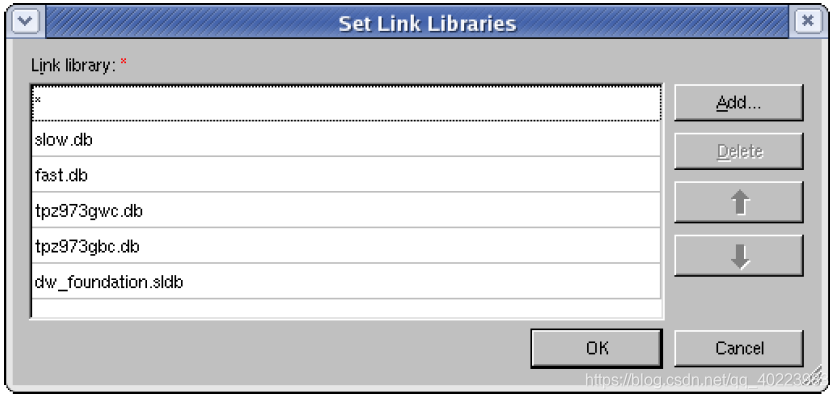

因为在前面设置了search path,其中包括了上述工艺相关库的路径,因此在设置link library和后面的target library的时候,可以直接写上库的文件名称而略

去路径,工具可以自动完成相应文件的搜索,去除路径之后的链接库文件如下图10所示。

图10 无路径的链接库文件选定图窗

在上图10或者图9中,点击OK按钮完成连接库的设定。设置链接库的操作可以直接采用tcl命令set link_library ”library” 来完成,其中引号中的就是刚才设定的几个库文件,用空格分开,简单吧。

目标库的设定(target library)同link library操作一样,而且除了没有表示内存的星号(*)之外,内容也是完全一样的。选定或者填写结果如下图11所示。

图11 目标库的设定图窗

目标库设置采用的tcl命令为:set target_library “lib”,其中lib的内容即为刚才设置的几个库文件(例“fast.db slow.db”)。

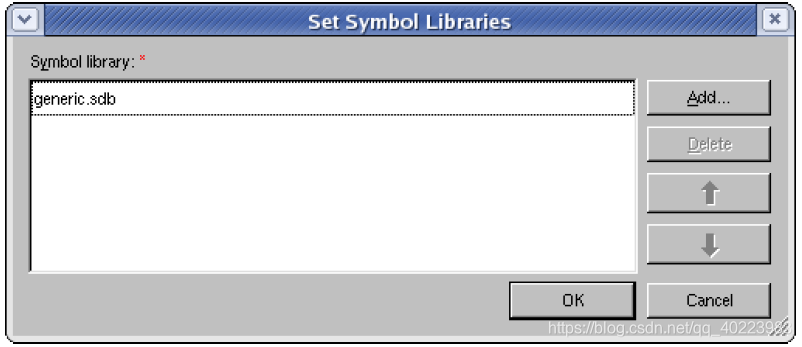

然后再进行符号(symbol)库的设定,符号库主要是用来在gui窗口中查看电路时使用的,表示基本单元器件的视图。同target library一样,也可以直接写

入库名,忽略路径。因该umc库中没有symbol文件,故采用工具中自带的symbol库文件。选择窗口、库名称见下图12。

图12 目标库的设定图窗

符号库设置的tcl命令为:set symbol_library “lib”。在图12中点击ok按钮,完成设置symbol库。

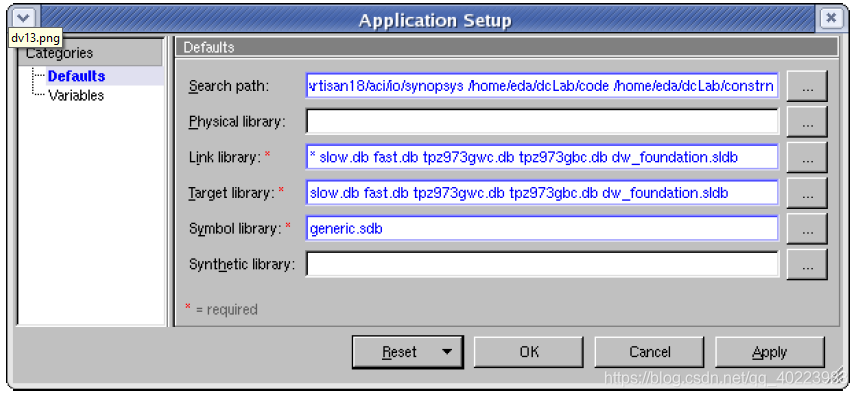

至此setup内容已经完成设置,结果如下图13所示。

图13 setup设定窗口

在图13中,点击OK按钮,完成启动项内容的设置。随后该设置可以在菜单命令中导出:File—>Save info—>Design Setup,将该文件保存为设计启动配置文件.synopsy_dc.setup,直接放在work目录下。下次再在该目录下启动工具的时候就不必重新配置,点击File—>Setup…,就可以看到表格中的各项已经配置完成了。

3.设计读入

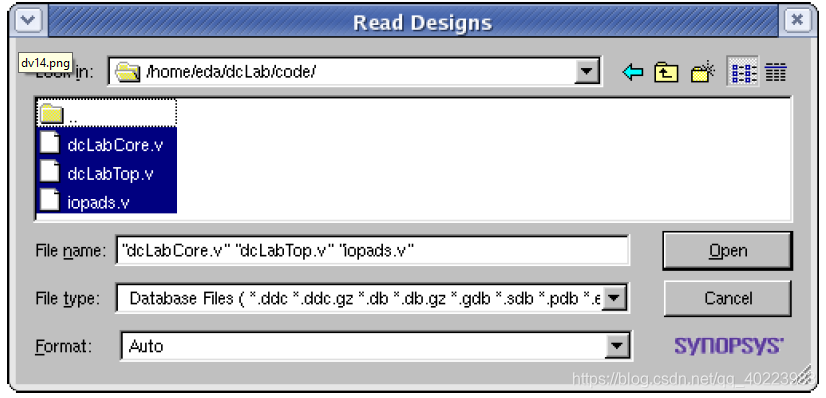

完成启动项配置后就要将设计倒入工具,选择菜单命令:File—>Read…,出现Read Design窗口。查找设计代码所在路径,选中所有需要的设计代码,如下图14所示。点击Open按钮,完成代码读入。

图14 setup设定窗口

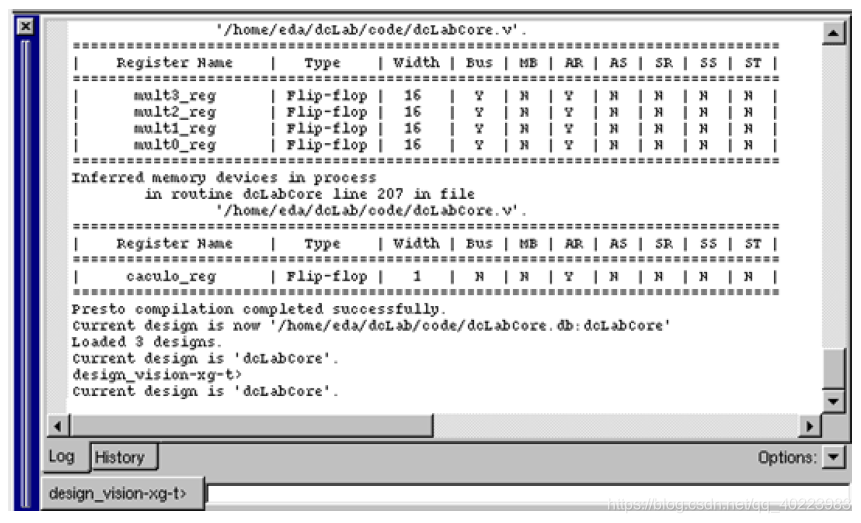

在读入代码的过程中,注意dv下方的log窗口回显与报告,如下图15。同时点选history键,查看相应的tcl命令:read(或者read_verilog)。

图15 读入设计时的窗口

读入设计之后,当前的设计会是读如过程中最后一个代码文件对应的设计,

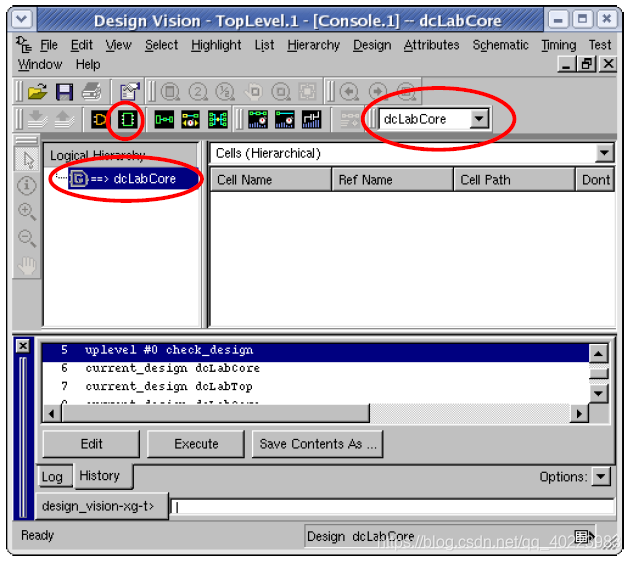

要将顶层设计设为当前设计。在dv主界面的工具栏下方的工具条下下拉选项选中、设置当前设计,我们这里是dcLabCore。同样注意history栏中的tcl命令:set current_design dcLabCore,记住对应的操作。

图16 当前设计设定

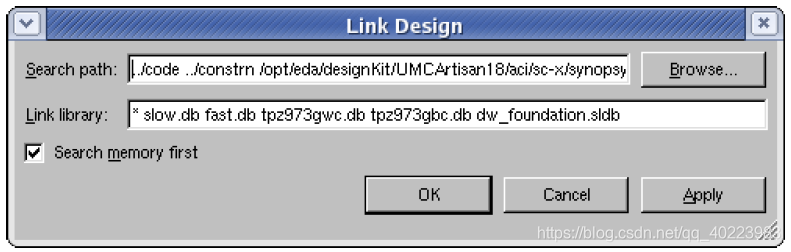

完成当前设计的设定后,以后的操作就是针对该设计进行的。下面要做的就是将设计与库链接起来。选择菜单命令:File—>Link Design。出现Link Design窗口,如下图所示。注意Search path与Link library两项与前述启动项中的设置是否一致。

图17 Link Design窗口

点击OK按钮完成设计与库的链接。此时要注意log窗口的链接过程的操作回显,及时修改错误与告警。

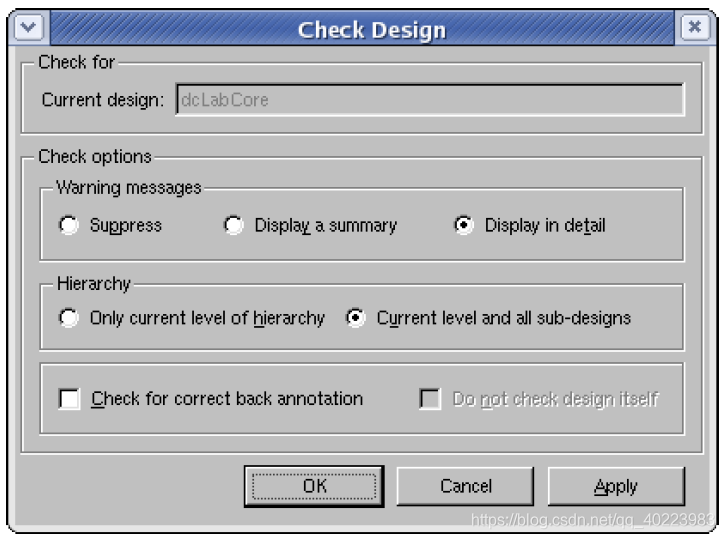

完成链接后要对设计进行检查。选择菜单命令:Design—>Check Design,出现如下窗口,点击OK按钮,对设计进行检查。注意log栏中的报告。

图18 Check Design窗口

至此,读入设计的工作完成。在这过程中,源代码中的各种与综合相关的问题都会被检查出来,注意随时查看报告并修改直到被综合器接受。下面就要对设计进行约束了。

4.设计约束与编译

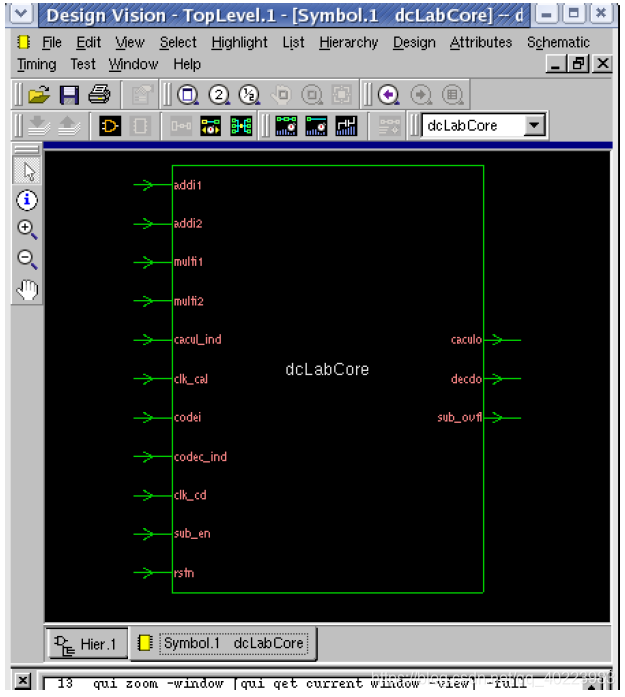

在dv的主界面中,因为已经读入设计,此时很多菜单和工具栏已经激活。在图16中,先选中Logical Hierarchy中的dcLabCore项,点击工具栏中的Create Symbol View(或者菜单项Schematic—>New Symbol View 选项),出现当前设计的symbol,我们的约束就要在当前设计中添加。

这里之所以先创建一个symbol,因为很多设计的约束,比如创建时钟(create clock)、输入输出延时(set input_delay/output_delay)、驱动与负载(set drive/load)、时钟无关路径(set false_path)等等,都是针对设计的端口的(port),图形化的

界面操作起来容易些。得到的symbol如下图19所示。

图19 创建当前设计的symbol

首先创建时钟,在symbol中选中clk_cal端口,然后选择菜单项Attributes—> Specify Clock…,注意灰色的Port name项应该为clk_cal;如果不是,不要关闭Specify Clock窗口,再在symbol上选中该端口,就会发现port name相应改变。

时钟的约束这里设定主要有四项,一项是时钟的名称,要方便易记、意义明确就好;二项是时钟的周期,由频率决定,这里clk_cal为50M,故周期20ns(时间单位在库中定义);三项是时钟的波形,定义一个时钟周期内高电平所处的时间区间;四项是将时钟网络设定为don’t touch,也就是在综合的过程中,时钟线上不要添加包括驱动buffer在内的任何器件。时钟信号clk_cal的选择与填写过

程如下图20所示。

图20 创建时钟clk_cal

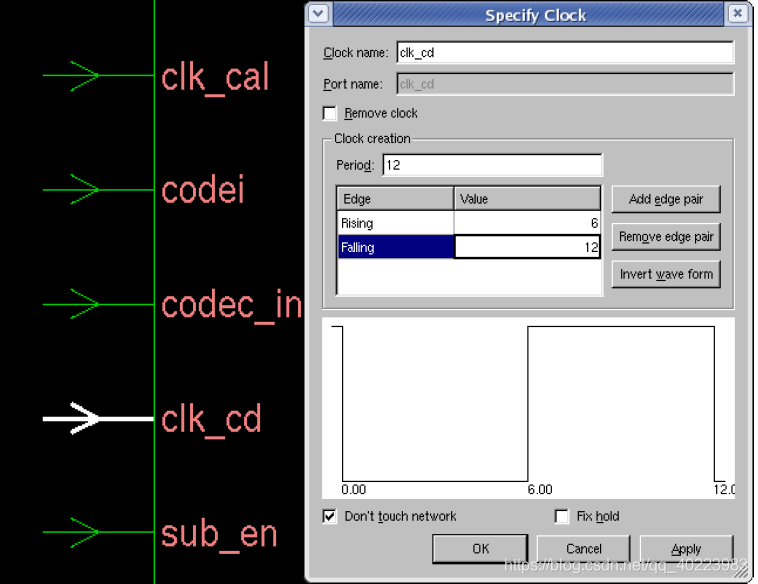

注意在Don’t touch network选项前打勾。点击OK按钮完成时钟clk_cal的创建。时钟的参数这里就不解释了。同样的方法创建时钟clk_cd,如下图。

图21 创建时钟clk_cd

时钟信号clk_cd频率80M,故此周期12ns,同clk_cal一样,将上升沿设定在波形中间。以上操作对应tcl命令:create_clock。

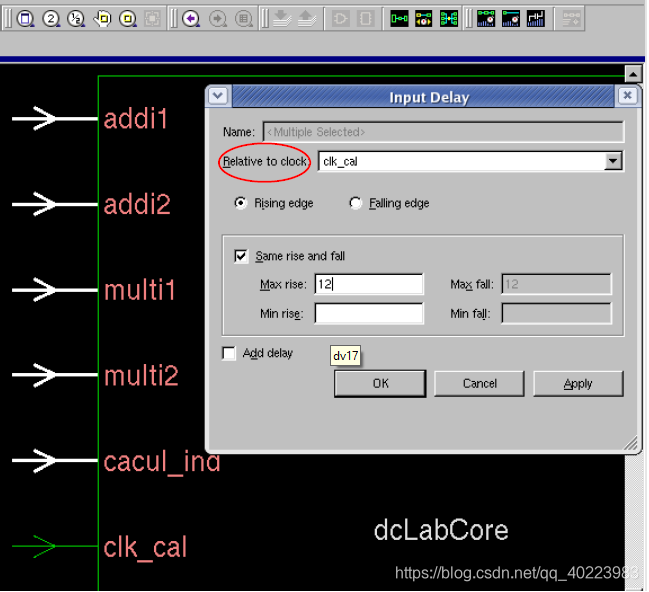

创建完成时钟之后,就要进行输入(set input_delay)和输出延时(output_delay)的约束,因为该约束是相对于时钟信号的。在symbol界面中,按住键盘ctr键,用鼠标选择addi1/addi2/multi1/multi2/cacul_ind端口(因为这些端口是和同一时钟clk_cal绑定的,设计中输入由时钟clk_cal驱动的触发器中),选择Attributes—> Operating Environment —>Input Delay菜单项,填写、选中相应的项目。如下图所示。

图21 创建相对时钟clk_cal的输入延时

通常输入延时计算为时钟周期的60%,也就是说留出60%的外部裕量。注意图中Relative to clock项的时钟选择要与设计中的定义一致。

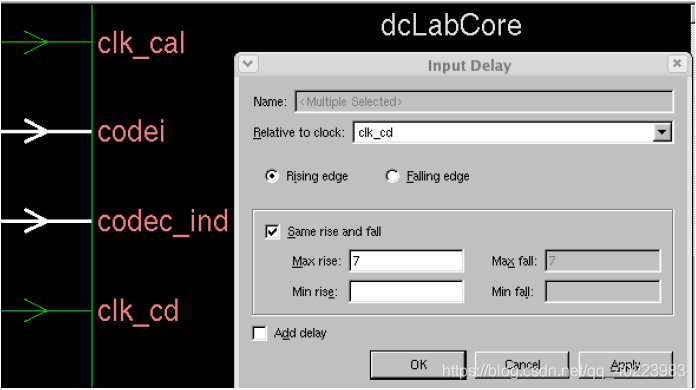

同样完成相对于时钟信号clk_cd的端口codei、codec_ind的输入延时,选择、填写后的界面如下图21所示。上述操作对应的tcl命令为:set input_delay “port”,

其中port即为相应于时钟的端口。

图21 创建相对时钟clk_cd的输入延时

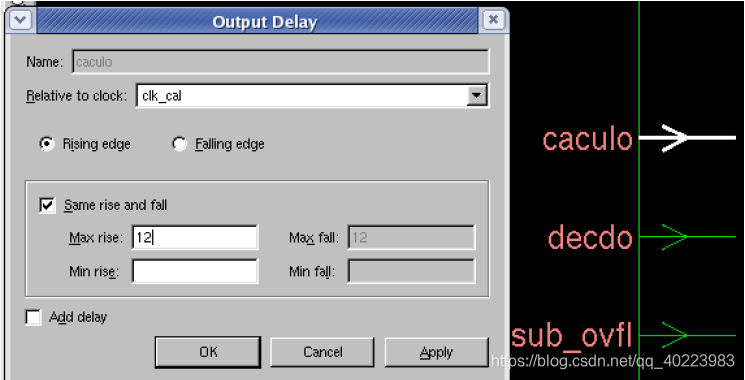

完成输入延时之后进行输出延时的设定(output_delay)。选中symbol中的端口caculo(它是由时钟信号clk_cal驱动输出),选择菜单项Attributes —> Operating Environment —>Output Delay,填写、选择如下图的内容,点击Apply按钮完成设置。

图21 创建相对时钟clk_cal的输出延时

同样完成输出信号decdo的输出延时的设定,注意该信号是和时钟clk_cd绑定的。以上操作定应tcl命令:set output_delay。

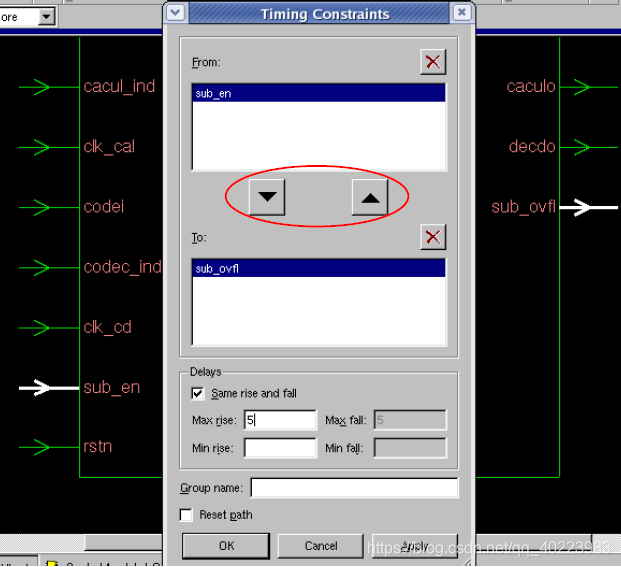

现在除了输入信号sub_en和输出信号sub_ovfl以外,所有的信号(除rstn)都进行了约束。现在来进行余下这两个端口信号的约束。在symbol中选中这两个端口,选择菜单项Attributes—>Optimization Constraints—>Timing Constraints,出现Timing Constraints窗口,如下图所示选择填写,完成约束。对应的tcl命令为:set max_delay。

图22 约束输入与输出间的最大延时

这里采用set max_delay的方法是因为输入端口信号sub_en到输出信号端口sub_ovfl之间没有时序逻辑,只有组合逻辑,因此要约束输入端口到输出端口之间的最大延时(最小延时除非有需要,否则可以不加以约束)。

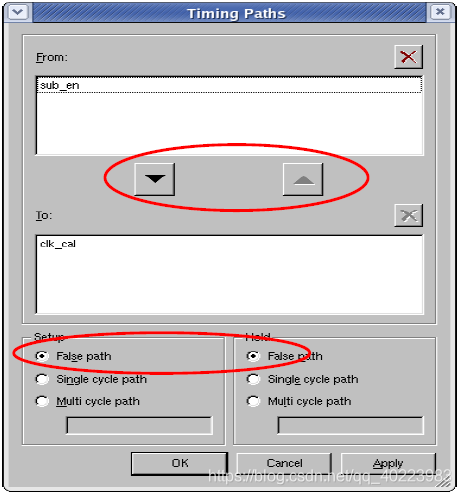

时序约束中还需要将无关路径区分开来,采用set_false_path的方法。所谓无关路径,就是告诉综合器某两条或者多条路径之间没有时序关系,可以不必理会、优化这些路径间的电路。设计中。sub_en端口的信号送入纯组合逻辑,而且与时钟clk_cal和clk_cd不存在相位依赖关系,故此这里设置为false path。在symbol界面中选定sub_en端口和clk_cal、clk_cd端口,选择菜单项:Attributes

—>Optimization Directive—>Timing Paths,出现如下窗口,From栏中留有sub_en项,To栏中留有clk_cal和clk_cd两项,选中False path项。

图23 无关路径设置

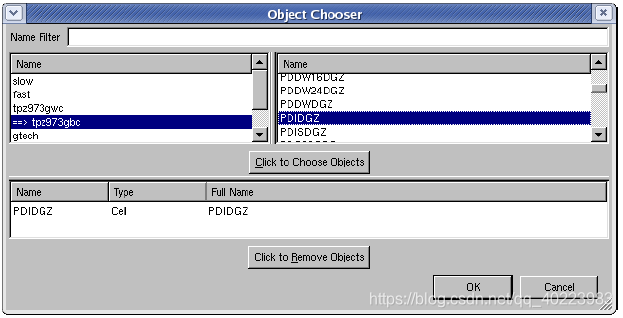

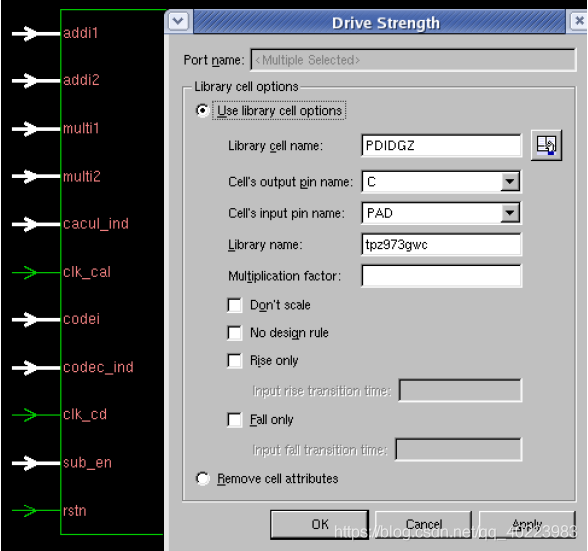

下面来设置驱动与负载(drive/load)。首先选中symbol中的输入信号端口,如下图所示。选择菜单项Attributes—> Operating Environment—>Drive Strength,出现Drive Strength窗口。按照下图填写、选择相应的内容,完成驱动设置。

图24-a 配置输入驱动

图24-b 配置输入驱动

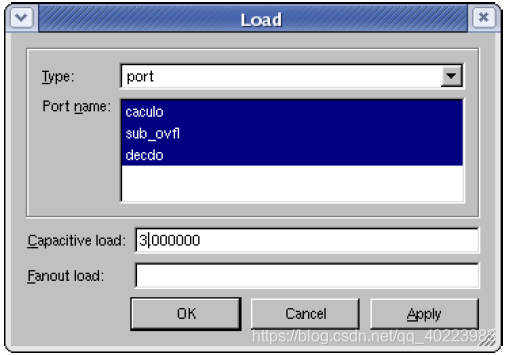

在symbol界面选中三个输出端口,选择菜单项Attributes—> Operating Environment—>Load,出现Load窗口。注意选中三个输出信号端口。在Capacitive load栏中填容性负载数值。

图25 输出负载约束

以上操作对应tcl命令:set drive/load。

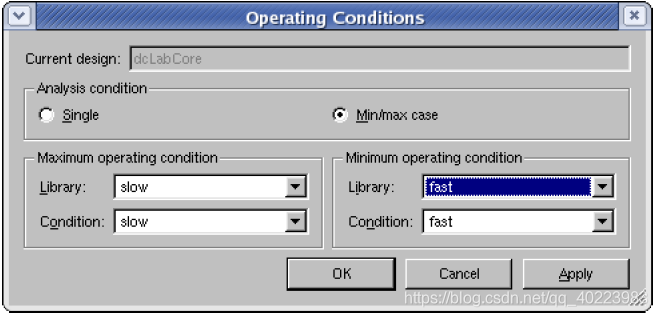

现在来设置操作环境(Operating Conditions)的设置。选择菜单项Attributes—> Operating Environment—> Operating Conditions,出现如下窗口。

图26 操作环境的设置

按照图示选择相应的内容,按按钮OK完成操作环境的设置。对应的tcl命令为:set operating_conditions。

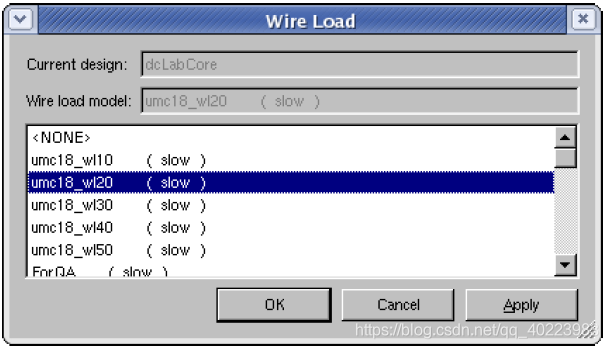

同样的,完成wire Load的设置:选择Attributes—> Operating Environment—> Wire Load菜单项,选择umc18_wl20模型。对应的tcl命令:set wire_load。

图27 线载模型的设置

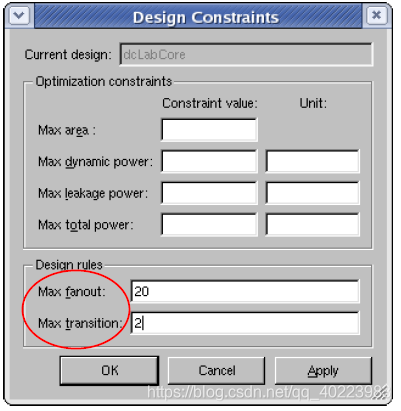

下面进行design rule的设定,主要是fanout和transition。选择菜单项Attributes—> Optimization Constraints—> Design Constraints,出现下图所示界面,只填写图示的两项即可。对应的tcl命令:set max_fanout/transition。

图28 fanout与transition的设置

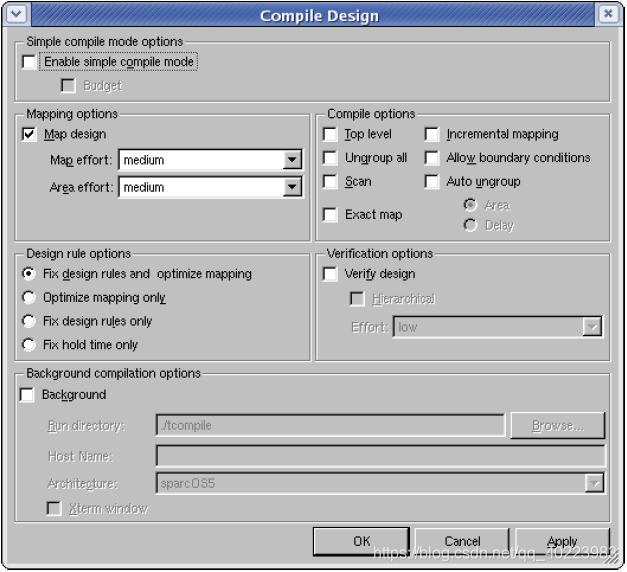

至此,设计相关约束设置完成,可以对设计进行综合了。选择菜单项Design—> Compile Design,出现设计编译窗口,如图选择,点击OK按钮编译设计。

图29 设计编译界面

编译的过程会随着设计的复杂变慢,编译的过程中注意log窗口的输出。完成编译后,需要查看各种报告。

5.查看报告与设计输出

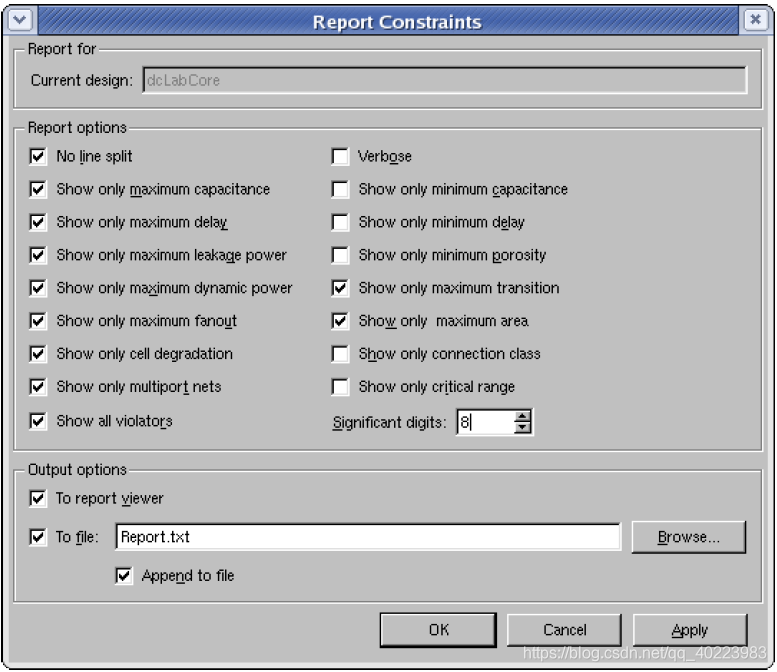

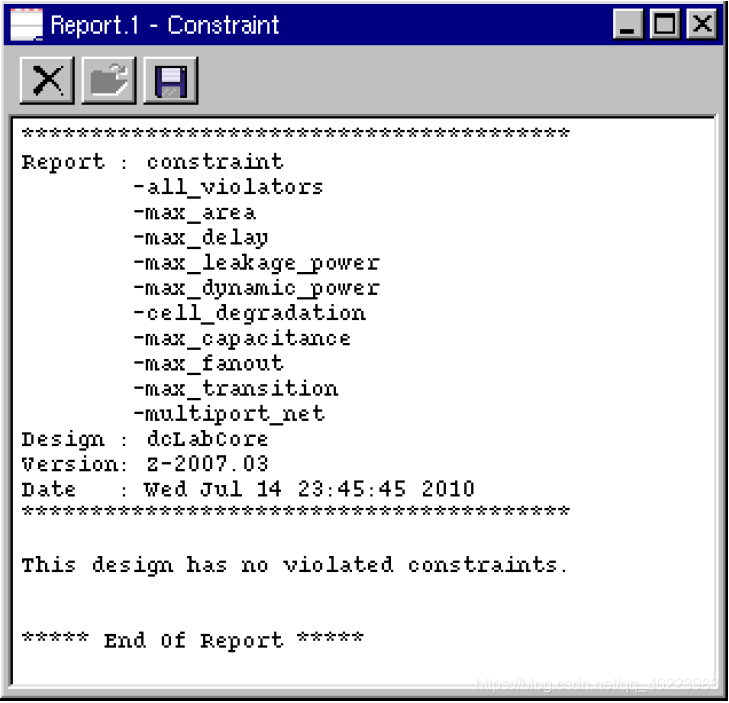

很多时候综合并不是一次就通过的,在这过程中有可能时序不满足约束要求,或者约束设置的不合理,或者设计本身有问题等,需要查看报告、调试。这里最重要的一个报告是约束报告。选择菜单项Design—>Report Constraints,出现如下图30所示的界面。

图30 约束报告选择界面

勾选想要查看的内容,点击OK按钮,可以看到与约束相关的报告。简单的一个报告如下图31所示。

查看报告的选项大多位于菜单Design和Timing之下。在完成综合之后,如果Report Constraints没有发现错误和不期望的告警,可以尝试将这些报告项输出,具体查看一下,非常有助于了解设计、熟悉工具。同时可以对照库中的.lib

文件查看一些参数。

图31 约束报告结果

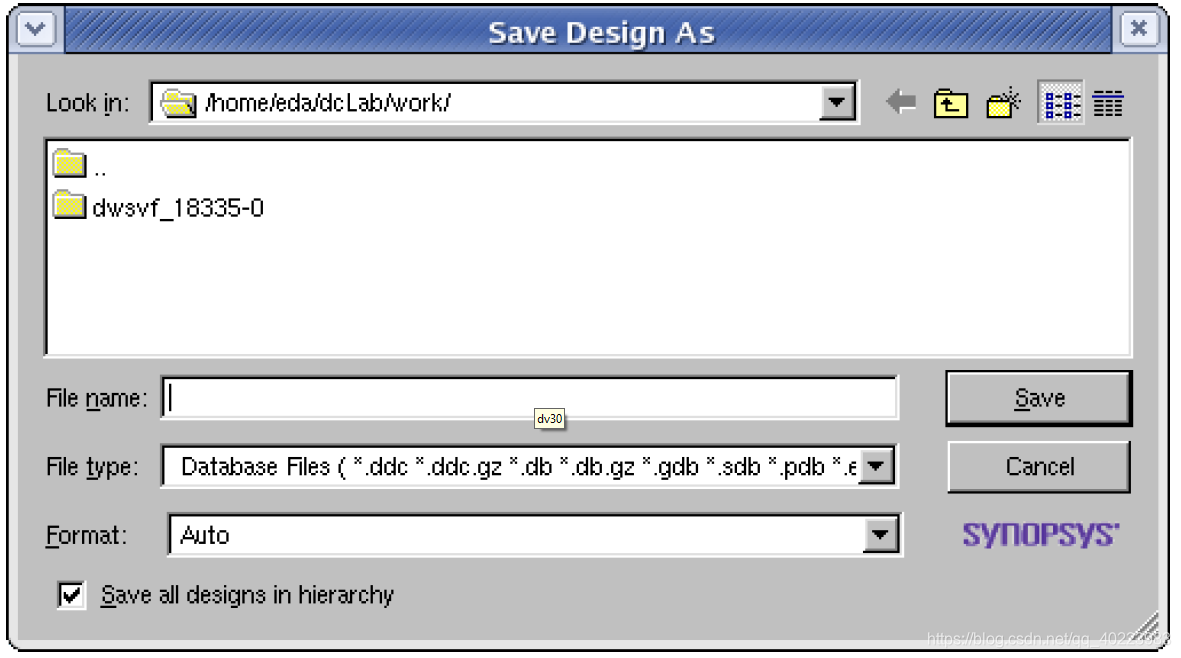

如果没有报告错误,就可以将设计保存下来。选择菜单项File—>Save as,可以将设计保存为各种格式。

图32 保存设计界面

同样可以保存启动项文件和约束文件:选择菜单项File—>Save info—> Constraints/Design setup,保存相应文件。

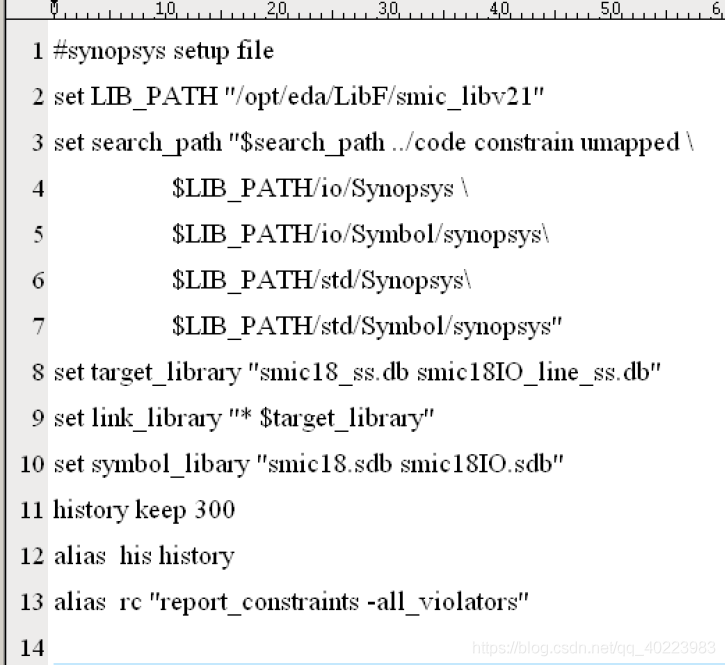

6..synopsys_dc.setup文件与dcLab.con文件

a. 启动项文件

文件.synopsys_dc.setup应位于当前的工作目录中,Linux/Unix下为隐含文件。这里先给出一典型的.synopsys_dc.setup文件,如下所示。

文件.synopsys_dc.setup第一项内容设定工具工作过程中需要搜索的路径位置(search_path),一般包括源代码的目录、库文件(工艺库模型文件、symbol文件)的目录、约束/运行脚本的目录、某些中间文件的目录以及在工具的安装目录配置的启动搜索目录,包括gtech库等目录。

文件.synopsys_dc.setup第二项内容一般用来设定目标库(target_library),也就是工艺库的名称,综合过程中工具会自动在搜索目录中寻找,来完成综合工作。第三项内容一般用来设定链接库(link_library),用于解析设计电路中的最小颗粒单元,其中,*,用来表示内存。

文件.synopsys_dc.setup第四项内容用来设定symbol库,也就是design vision

可以看到的网表图形。其余的内容还可以包括命名规则、别名定义等,可以任意设定,示例中没有一一给出。

b.设计的约束文件

约束文件主要用于优化设计电路的,主要内容有:读入/分析源文件、设定设计的工作条件/环境/设计规则、时序条件、面积约束、综合策略等。

首先是读入源代码,也就是HDL文本描述的设计文件,此处不用制定目录,design compiler会在搜索目录($search_path)中搜索。tcl语句如下:

read_verilog {dcLabCore.v dcLabTop.v iopads.v}

读入设计原文件后,一般设定当前设计,这样约束条件才可有针对性施加:

current_design dcLabCore

设定当前设计后,要完成链接,也就是将设计与库链接起来,用于映射过程中搜寻相应的单元,完成综合。tcl语句: link

检查设计,主要是检查完成转换(translate)的设计: check_design。然后设定输出网表的格式规则,输出未优化的设计:

set verilogout_no_tri true

change_names -rule verilog -hier

write -f ddc -hier –out ../output/dcLabCore.ddc

然后对设计设定时序约束,这是最重要的一项约束,用于设定设计的工作速度的。针对不同的设计部分,有不同的约束方法。这里假设设计为全同步设计,单时钟工作,复杂情况参考design compiler的手册即可。以下语句设定时钟及属性、输入信号的时间裕量:

create_clock –name clk_cal -period 20 [get_ports clk_cal]

#名称clk_cal,对应端口clk_cal,50M工作频率

set_clock_uncertainty -setup 0.2 [get_clocks clk_cal] #时钟的不确定时间

set_clock_latency -source -max 0.3 [get_clocks clk_cal]#时钟输入延时

set_clock_latency -max 0.1 [get_clocks clk_cal]#时钟延时

set_clock_transition -max 0.2 [get_clocks clk_cal]#时钟上升/下降时间

set_dont_touch_network [get_ports "clk* rstn"]

#不对时钟复位信号优化

set_ideal_network [get_ports "clk* rstn"] #延时分析时认为时钟复位无延时

set_input_delay -max 12 -clock clk_cal [get_ports "add* mult*"]#输入信号裕量

set_output_delay -max 12 -clock clk_cal [get_ports "caculo"] #输出时间裕量

完成时序约束后,要对设计的工作环境、设计规则等进行约束,如下约束语句:

set_wire_load_mode top

#设定线载模型的模式

set_wire_load_model -library slow -name umc_wl20 -max

#线载模型,要粗略综合一下估出面积,再设定

以下是设计规则的约束:

set_driving_cell -lib_cell FFEDQHD4X -pin Q [get_ports all_inputs]

#驱动能力的约束

set max_cap [expr [load_of slow/AND2HD4XSPG/A] * 5]

set_load [expr 3 * $max_cap] [all_outputs] #设计负载设定

set_fanout_load 10 [all_outputs] #扇出负载

然后是综合的策略,简单的设计比较容易,这里不展开:

compile -map_effort medium -incremental_mapping

输出综合报告、输出综合网表、综合数据以及标准延时文件:

rc > log/rc.log #时序报告

write -f verilog -hier -out output/dcLabTop.sv #输出网表

write -f ddc -hier -out output/dcLabTop.ddc#综合数据文件

write_sdf -version 2.1 mapped/light_controller.sdf #标准延时文件

上述内容为约束文件主要内容,同学们可以讲示例中的约束保存下来自己细看一下。