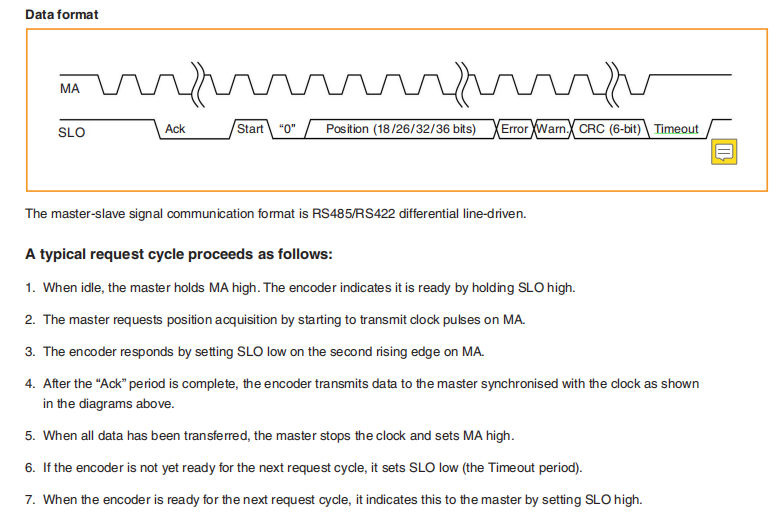

BISS通信协议是一种全双工同步串行总线通信协议,专门为满足实时、双向、高速的传感器通信而设计,在硬件上兼容工业标准SSI(同步串行接口协议)总线协议。具体可参考BISS通信协议概述https://wenku.baidu.com/view/d0faf64fc850ad02de804164.html,下面直接来看下它的时序图:

时序图

注意事项

程序设计思路

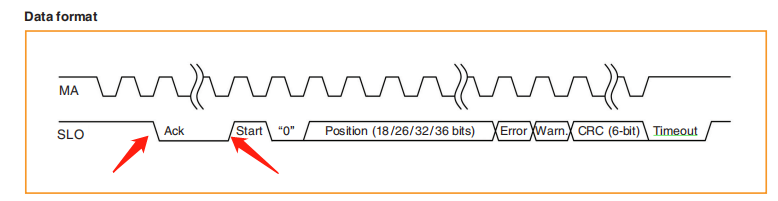

MA是时钟,SLO是数据,我们要做的就是给时钟,然后采集数据。观察时序,SLO有9个状态,分别是等待状态、Ack状态、Start状态、0状态、Position状态(根据我自己的实际硬件参数,这里取26bit)、Error状态、Warn状态与CRC状态。当Error为1(表示数据可信)并且crc校验正确时,将Position阶段采集到的SLO数据保存输出即可。

问1:如何区分SLO的9个状态?

解答1:巧用状态机,这里用状态机标记SLO的9个状态。

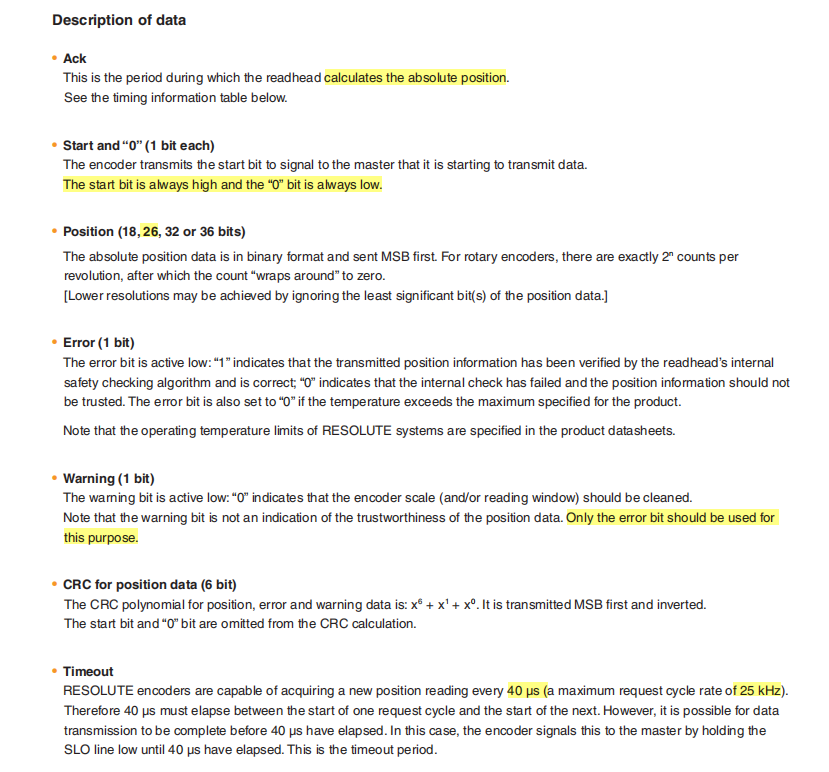

问2:等待状态跳转Ack状态以及Ack状态跳转Start状态跳转时间都是不确定的时长,针对不确定的时长如何设计转移条件呢?

解答:可采用检测SLO下降沿和上升沿的检测方法。

参考代码:

1 assign slo_in_posedge = slo_in_ack_ff2==0&&slo_in_ack_ff1==1; //check the slo posedge;

2 assign slo_in_negedge = slo_in_ack_ff2==1&&slo_in_ack_ff1==0; //check the slo negedge;

3

4

问3:SLO属于外部器件输进来的信号,直接使用可能会造成亚稳态,那如何避免亚稳态的发生呢?

解答:打拍子缓存,常规做法是至少打3拍。

问4:输进来的是串行数据,如何对数据进行缓存组合成26bit数据输出?

解答:串转并即可。

问5:如何进行crc-6检验?

解答:对于常规的crc-16,crc-32,crc-8,都有现成的网站在线生成代码可以调用http://www.metools.info/code/c15.htm,对于crc6校验我会单独写一篇文章详细阐述设计思路。

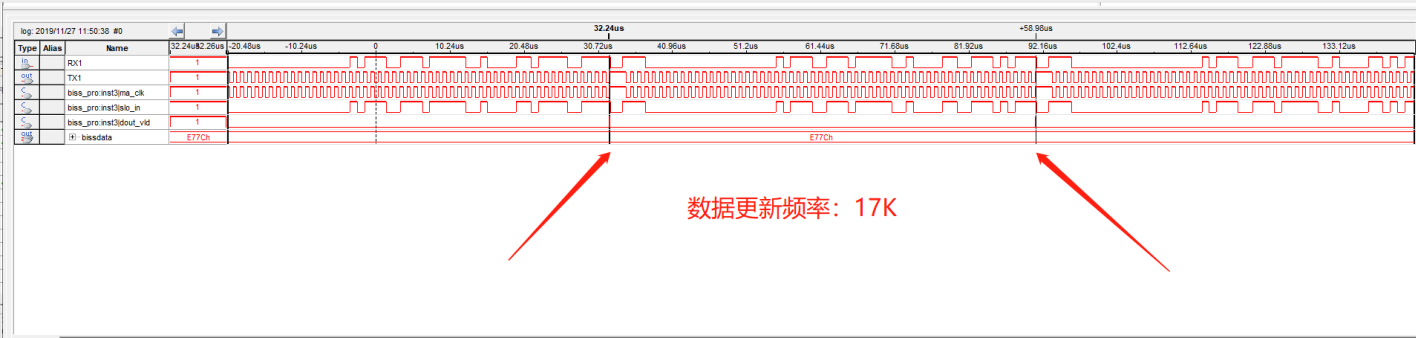

上板验证

注意:未经允许,禁止转载,违法必究!