1、中断

①轮询方式和中断方式

轮询(Polling)方式:CPU主动对外设进行查询,外设处于被动地位,执行效率低下,等待时间长。

中断(Interrupt)方式:CPU通过响应中断请求为外设提供服务,外设处于主动地位,CPU在外设没有发起中断时可以专心执行其他程序或进入休眠,执行效率高。

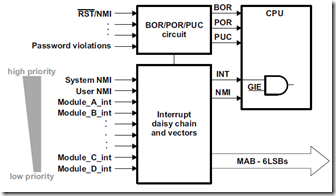

②430中断系统

三种中断:系统中断(System reset)

非可屏蔽中断(Nonmaskable)

可屏蔽中断(Maskable)

中断优先级(Priority)

Warning:此处的可屏蔽与非可屏蔽指GIE对中断触发的影响,NMI和MI都有可能被自身独立的中断开关关闭。

③中断响应过程

1、完成当前指令

2、将PC入栈

3、将SR入栈

4、当有多个中断请求时,响应高优先级中断,GIE清零,屏蔽其他中断发生

5、清零单源中断的中断请求标志位,多源终端不会自动清除标志位

6、除了SCG0外,SR的其他位都被初始化,使单片机从低功耗模式进入活动模式。

7、将中断向量注入PC,转入中断服务子程序

④中断返回过程

when RETI

1、SR出栈

2、PC出栈

⑤C430中断服务子程序书写格式

#pragma vector=中断矢量向量

__interrupt void 函数名(void)

{...}

2、MSP430时钟系统(UCS)

UCS->Unified Clock System 统一时钟系统

①三种时钟类型

ACLK:辅助时钟Auxiliary clock

MCLK:主时钟Masker clock

SMCLK:子系统时钟Subsystem masker clock

②五种时钟源

XT1CLK:低频或高频通用时钟源(32768Hz or 4MHz~32MHz)。

Low-freq or High-freq oscillator, can be used with 32768Hz watch

crystals, standard crystals, resonators, or external clock sources in the 4MHz

to 32MHz.

VLOCLK:内部超低功耗低频振荡器(10kHz)->RC振荡器,稳定性较差。

Internal very low power, low frequency oscillator with 10 kHz

typical frequency.

REFOCLK:内部低频振荡器(32768Hz),用作参考时钟源。

Internal, trimmed, low-freq oscillator with 32768 Hz typical

frequency, with the ability to be used as a clock reference into the FLL.

DCOCLK:数控振荡器输出时钟,可用锁频环(FLL)设置批量,DCOCLKDIV为DCOCLK的1,2,4,8,16,32分频输出。

Internal digitally-controlled oscillator(DCO) that can be stabilized by

the FLL.

XT2CLK:可选高频振荡器(4MHz~32MHz)

Optional high-freq oscillator that can be used with standard crystals,

resonators, or external clock sources in the 4MHz to 32MHz range.XT2CLK

can be used as a clock reference into the FLL.

③数控振荡器输出频率设定

FLL参考时钟进入FLL后,通过FLLREFDIV分频后输入10位频率计数器的正端,计数器输出计数值控制DCO频率发生器,产生DCOCLK,DCOCLK经FLLD分频得到

DCOCLKDIV,再经FLLN分频后输入频率计数器的负端,当正负端频率一致时,计数器输出值不变,FLL稳定输出DCOCLK和DCOCLKDIV。

计算公式:FLLREFCLK/n=DCOCLKDIV/(N+1)

④UCS初始配置情况

XT1CLK处于Low-freq模式,ACLK选用XT1CLK,若XT1CLK出错,则自动切换至REFOCLK。

MCLK和SMCLK选用DCOCLKDIV。

FLLREFCLK选用XT1CLK。若XT1CLK出错,则自动切换至REFOCLK。

XT2CLK默认不使能。

3、低功耗

Active:CPU,MCLK,ACLK and SMCLK are active,DCO is enabled if sources ACLK,MCLK, or SMCLK.FLL is enabled if DCO is enabled.

LPM0:ACLK and SMCLK are active.CPU and MCLK are disabled.DCO is enabled if sources ACLK,MCLK, or SMCLK.FLL is enabled if DCO is enabled.

LPM1:ACLK and SMCLK are active.CPU and MCLK are disabled.DCO is enabled if sources ACLK,MCLK, or SMCLK.FLL is disabled.

LPM2:ACLK is active.CPU,MCLK and SMCLK are disabled.DCO is enabled if sources ACLK,MCLK, or SMCLK.FLL is disabled.

LPM3:Same as LPM2

LPM4:CPU and All Clocks are disabled.->常用于软件关机,保存RAM内数据和IO状态,超低功耗。

中断会自动将单片机从低功耗模式中转换到活动模式,中断返回时SR寄存器恢复,单片机继续进入原低功耗状态。

__bis_SR_register(LPMx_bits);

__bic_SR_register(LPMx_bits);