http://kitebee.meibu.com/forum.php?mod=viewthread&tid=69654&extra=page%3D5

IC开短路测试(open_short_test)又叫continuity test 或contact test,它是一种非常快速发现芯片的各个引脚间的是否有短路,及在芯片封装时是否missing bond wires.通常都会被放测试程序的最前面.它还能发现测试时接触是否良好,探针卡或测试座是否有问题.

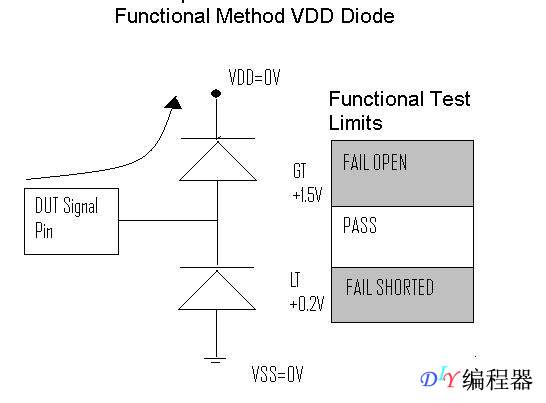

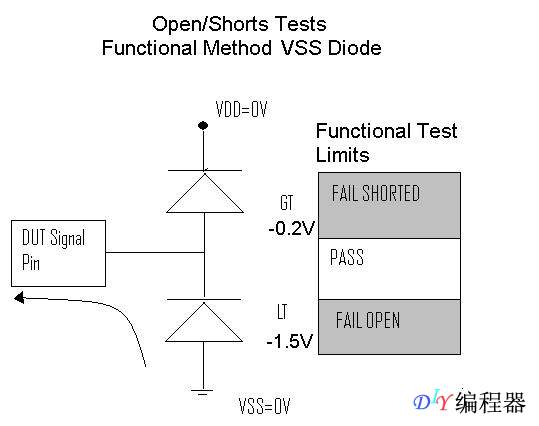

开短路测试的测试原理比较简单,分open_short_to_VDD 测试和open_short_to_VSS测试.一般来说芯片的每个引角都有泄放或说保护电路,是两个首尾相接的二极管,一端接VDD,一端接VSS。

信号是从两个二极管的接点进来.测试时,先把芯片的VDD引脚接0伏(或接地),再给每个芯片引脚供给一个100uA到500uA从测试机到芯片的电流,电流会经上端二极管流向VDD(0伏),然后测引脚的电压,正常的值应该是一个二极管的偏差电压0.7伏左右,我们一般设上限为1.5伏,下限为0.2伏,大于1.5伏判断为openfail,小于0.2伏判断为shortfail.这就是open_short_to_VDD测试.

open_short_to_VSS测试的原理基本相同.同样把先VDD接0伏,然后再给一个芯片到测试的电流,电流由VSS经下端二级管流向测试机.然后测引脚的电压,同样正常的值应该是一个二极管的偏差电压0.7伏左右,只是电压方向相反,上限还是为1.5伏,下限为0.2伏,大于1.5伏判断为openfail,小于0.2伏判断为shortfail.这就是open_short_to_VSS测试.

所以对测试机里的测试器件来说,只要能给电流测电压的器件都能做开短路测试.只是精度有差异,效率有高低.

编程器测试接触不良、开短路用的该是这个原理,通过检测那个电压变化,只是这个小电压测试起来有点麻烦,采用模拟方式倒是容易实现,数字方式必须进行放大处理1或者0

http://kitebee.meibu.com/forum.php?mod=viewthread&tid=98421&extra=page%3D5

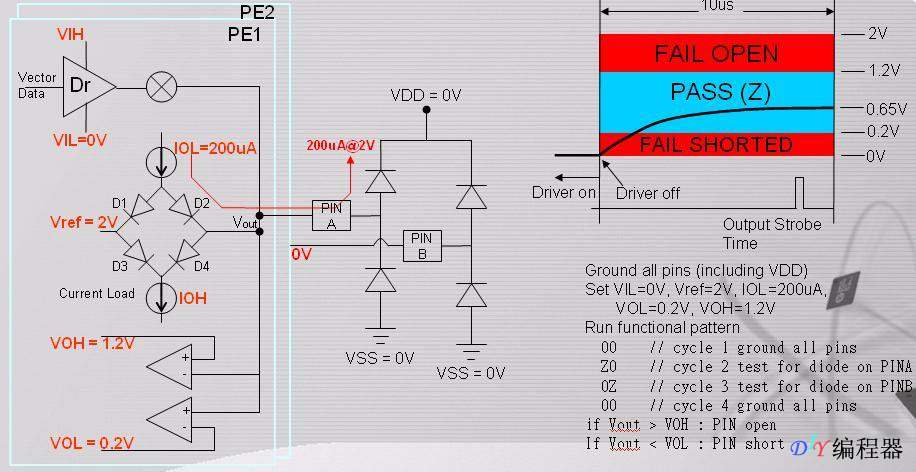

以 run pattern 方式測 open/short 的原理如下 :

1. 利用 tester pin electronics 的 dynamic load 來 force current, (VOH / VOH / VIL / IOL 設定如圖)

當 pinA 還未 connect to tester 時, Vout = Vref, 一旦 connect to tester 後, 200uA@2V 的電源

讓 IC diode 導通, Vout = 0.65V, 所以 pattern 為 compare "Z"

2. 假如 IC open, Vout=Vref, Vout=2V > VOH=1.2V, run pattern 時會 fail

3. 假如 IC short, Vout=0V (short 到其他 pin, 其他 pin voltage=0V), Vout=0V < VOH=0.2V, run pattern 時也會 fail

用的还是反向二极管特性