|

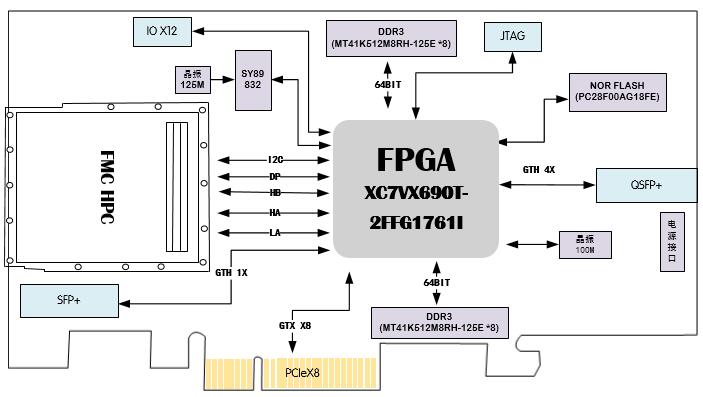

一、板卡概述 本板卡基于Xilinx公司的FPGA XC7VX690T-FFG1761 芯片,支持PCIeX8、64bit DDR3容量2GByte,HPC的FMC连接器,板卡支持各种接口输入,软件支持windows。

二、功能和技术指标: 1、标准PCI-E接口,支持PCI-E 8x,支持PCI-E 3.0。 2、标准FMC-HPC接口,VADJ电平为1.8V。 3、前面板引出1路SFP+光模块, 高设计速度10Gbps。 4、板卡后面引出2路SFP+光模块, 高设计速度10Gbps。 4、板卡后面引出2路SFP+光模块, 高设计速度10Gbps。 5、标准JTAG接口。 6、支持两组64bit,2GB的DDR3。 7、主频1GHz,支持1.2GHz 8、支持BPI模式快速加载。 9、器件支持商业级,工业级。 三、接口测试软件: 1、 DDR3 IP测试,PCIe IP测试; 2、万兆光纤网络开发 3、 FMC上接高速ADC,DAC子卡,并可提供演示程序。 四、基于Virtex7的 PCI-E 3.0 万兆以太网产品 IP开发 本板卡 基于Virtex7 XC7V690T-FFG1761,设计的PCIe 底板,板卡特点如下: 1、标准PCI-E接口,支持PCI-E 8x,支持PCI-E 3.0。 2、标准FMC-HPC接口,VADJ电平为1.8V。 3、前面板引出1路SFP+光模块, 高设计速度10Gbps。 5、标准JTAG接口。 6、支持两组64bit,2GB的DDR3。 7、主频1GHz,支持1.2GHz 8、支持BPI模式快速加载。 9、器件支持商业级,工业级。 三、接口测试软件: 1、 DDR3 IP测试,PCIe IP测试; 2、万兆光纤网络开发 3、 FMC上接高速ADC,DAC子卡,并可提供演示程序。 四、基于Virtex7的 PCI-E 3.0 万兆以太网产品 IP开发 本板卡 基于Virtex7 XC7V690T-FFG1761,设计的PCIe 底板,板卡特点如下: 1、标准PCI-E接口,支持PCI-E 8x,支持PCI-E 3.0。 2、标准FMC-HPC接口,VADJ电平为1.8V。 3、前面板引出1路SFP+光模块, 高设计速度10Gbps。 4、板卡后面引出2路SFP+光模块, 高设计速度10Gbps。 4、板卡后面引出2路SFP+光模块, 高设计速度10Gbps。 5、支持两组64bit,2GB的DDR3。 6、标准JTAG接口。 7、支持BPI模式快速加载。 高设计速度10Gbps。 5、支持两组64bit,2GB的DDR3。 6、标准JTAG接口。 7、支持BPI模式快速加载。

基于赛灵思的V7 的FPGA开发的PCIe DMA IP

- 支持8.0Gbps(Gen3)at x8,x4,x2和x1的硬核,包括Kintex-Ultrascale和Virtex-7 GTH类型的FPGA

- 支持5.0Gbps(Gen2)at x8,x4,x2和x1的硬核,包括Kintex-Ultrascale,Virtex-7 GTH,Virtex-7 GTX,Kintex-7 GTX和Zynq-7045类型的FPGA

- 支持5.0Gbps(Gen2)at x4,x2和x1的硬核,包括Artix-7和Zynq-7030类型的FPGA

- 兼容PCIE3.0协议;

大有效载荷256 Byte;支持MSI和INT消息 大有效载荷256 Byte;支持MSI和INT消息

AXI接口:

- 可以通过AXI4-Lite Slave接口来进行桥配置

- 可以通过AXI4-Lite Master接口来进行外部寄存器配置

多支持4个AXI4 Master接口 多支持4个AXI4 Master接口 多支持4个AXI4 Slave接口 多支持4个AXI4 Slave接口 多支持4个AXI4 Stream input 和Stream output接口 多支持4个AXI4 Stream input 和Stream output接口- AXI4 Master,Slave和Stream 接口支持64bit,128bit和256bit的数据

- AXI4 Master和Slave接口可配置成AXI3接口

配置:

- 通过PCIE和(或)AXI4-Lite Slave接口可操作桥配置空间

- 具有4KBytes的桥内部寄存器

- 具有4KBytes的PCIe配置空间

- 8KBytes用户定义的外部寄存器空间

DMA引擎:

- 支持

多8个完全独立的DMA引擎 多8个完全独立的DMA引擎

- 支持

多4GBytes或无限长的传输长度 多4GBytes或无限长的传输长度

- 支持

多16个outstanding读请求和写请求 多16个outstanding读请求和写请求

- 支持Completion重排序

- 可重配置源和目的,能在PCIe接口,AXI4 Master接口和Stream input和output接口之间进行转变

- 灵活的Scatter-Gather DMA模式,包括每个描述符可动态DMA控制

- 可选的DMA状态报告给描述符,方便软件管理设计

- 提供离散DMA功能、直接DMA功能和DMA通道管理

赛灵思V7 系列的FPGA开发的TCPIP 的IP core 特点: 1.支持多种的10G MAC 2.每个tcp硬核堆栈支持8个逻辑接口。每个接口可以只有一个IP,物理地址,VLAN ID,网关,子网掩码。 3.支持9K字节长包 4.支持VLANs 5.内嵌ARP 6.用XGMII高速接口连接10G PMA-PCS PHY 7.一个工作在156.25MHz的64bit的axi4—stream接口让用户调试使用 8.可通过一个32bit的axi4-Lite从机协议去配置ip核 9.用户接口为工作在156.25MHz的128bit的axi4-stream

10.多达128个并发客户机或服务器的TCP会话模式。每个会话都可以连接到任何逻辑接口 11.为每个会话打开特定的流控功能

12.用户可配置的TCP选项:MSS,时间戳, VLAN PCP , VLAN DEI 13.如果数据包的长度大于从用户应用程序接口远程配置(MSS)中的值则负载自动分割。 14.可配置TCP重操作记忆:宽度、深度、内部或外部

本设计方案 支持硬件板卡销售、IP销售 两种模式。也可以委托设计成品。 另外IP除了支持Virtex7系列,也可以支持更高等级芯片的开发 如Ultrascale系列。

五 应用领域 软件无线电处理平台 图形图像硬件加速器 Net FPGA |