4.1 全编程SOC(All Programmable SoC) 7

5.1如图所示为ZYNQ-7000CLG400 IOBANK 的分别情况 21

一、整体概述

此板卡是由南京米联电子设计团队设计的一款高性能SOC开发板。采用了美国XILINX公司开发的XC7Z020CLG484作为CPU,硬件设计方案参考了安富利公司的Zedboard,最大程度实现了软件和硬件的兼。同时本开发板的特色是采用了MiCore+Functional Board 的设计思路。核心板处理器和功能模块的分离,是学习、科研、项目开发、DEMO方案首选硬件。

二、应用领域及人群

n 机器视觉、机器人;

n 伺服系统、运动控制;

n 视频采集、视频输出、消费电子;

n MiniPC 运行于LIUNX;

n SOC感兴趣的爱好者;

n 电子信息工程、自动化、通信工程等电子类相关专业的大专生、本科生及其研究生入门学习;

n 项目研发前期验

三、硬件配置

· Xilinx® XC7Z010/7010-1CLG400 Zynq-7000 AP SoC

o Primary configuration = QSPI Flash

o Auxiliary configuration options

§ Cascaded JTAG

§ TF Card

· 内存

o 1024 MB DDR3 (128M x 32)

o 128Mb QSPI Flash

·接口

o USB-JTAG Programming

§ Accesses PL JTAG

§ PS JTAG pins connected through PS Pmod

o 10/100/1G Ethernet

o USB OTG 2.0

o TF Card

o USB 2.0 FS USB-UART bridge

o 36GPIO(PL)

o PMOM(PL)X2

o PMOM(PS)X1

o Two Reset Buttons (1 PS, 1 PL)

o Four Buttons (2 PL 2S)

o Nine User LEDs (1 PS, 4 PL)

o DONE LED (PL)

· 板载晶振

o 50 MHz (PS)

· 显示/音频

o HDMI In/out(PL)

o Audio Line-in, Line-out, microphone

· 电源

o On/Off Switch

o 5V @ 5A AC/DC regulator

MiZ701硬件资源

BANK资源分配

4.1 全编程SOC(All Programmable SoC)

4.1 全编程SOC(All Programmable SoC)

MiZ701核心板搭载了一颗XILINX 可全编程SOC芯片-Zynq XC7Z010-1CLG400/ XC7Z020-1CLG400。

Zynq XC7Z010-1CLG400/ XC7Z020-1CLG400集成了ARM A9双核的CPU 和28K/85K可编程逻辑单元,实现了硬件编程和软件编程同时具备的超级功能。

4.2 内存(Memory)

4.2.1 DDR3

Zynq的PS内存接口,包括了一个动态内存控制器(DDR控制器)接口和静态内存接口。

MiZ701核心板搭载了2片镁光(Micron)的MT41K256M16RE-125 M DDR3内存。单 片内存的大小是512MB 数据接口是16bit。两片内存一起组了32bit的数据接口,内存大小 1024MB.MiZ701开发板采用了高速布线,DDR3内存接口频率速度达到533MHZ(1066MHZ)。

MiZ701核心板搭载了2片镁光(Micron)的MT41K256M16RE-125 M DDR3内存。单 片内存的大小是512MB 数据接口是16bit。两片内存一起组了32bit的数据接口,内存大小 1024MB.MiZ701开发板采用了高速布线,DDR3内存接口频率速度达到533MHZ(1066MHZ)。

MiZ701的DDR3采用了1.5V电压标准,并且具备终端补偿电阻。PCB布线的 时候终端补偿电阻尽量靠近了DDR3内存,确保了最高速度可以达到 533MHZ(1066MHZ)

表4-2-1 MiZ701 DDR3引脚分配

| Signal Name | Description | Zynq pin | DDR3 pin |

| DDR_CK_P | Differential clock output | L2 | J7 |

| DDR_CK_N | Differential clock output | M2 | K7 |

| DDR_CKE | Clock enable | N3 | K9 |

| DDR_CS_B | Chip select | N1 | L2 |

| DDR_RAS_B | RAS row address select | P4 | J3 |

| DDR_CAS_B | RAS column address select | P5 | K3 |

| DDR_WE_B | Write enable | M5 | L3 |

| DDR_BA[2:0] | Bank address | PS_DDR_BA[2:0] | BA[2:0] |

| DDR_A[14:0] | Address | PS_DDR_A[14:0] | A[14:0] |

| DDR_ODT | Output dynamic termination | N5 | K1 |

| DDR_RESET_B | Reset | B4 | T2 |

| DDR_DQ[31:0] | I/O Data | PS_DDR_[31:0] | DDR3_DQ pins |

| DDR_DM[3:0] | Data mask | PS_DDR_DM[3:0] | LDM/UDM x2 |

| DDR_DQS_P[3:0] | I/O Differential data strobe | PS_DDR_DQS_P[3:0] | UDQS/LDQS |

| DDR_DQS_N[3:0] | I/O Differential data strobe | PS_DDR_DQS_N[3:0] | UDQS#/LDQS# |

| DDR_VRP | I/O Used to calibrate input termination | G5 | N/A |

| DDR_VRN | I/O Used to calibrate input termination | H5 | N/A |

| DDR_VREF[1:0] | I/O Reference voltage | H6, P6 | H1 |

MiZ701开发板DDR3内存部分数据接口采用了16X2组层了32bit数据总线,布线方式采用了FLY方式。XILINX的开发工具提供了优化PCB延迟时序的功能,XILINX的软件可以通过长度自动计算需要的延迟时间。计算方法:http://www.xilinx.com/support/answers/46778.html

表4-2-2 MiZ701的PCB延迟参数计算

| Pin Group | Length (mm) | Length (mils) | Package Length (mils) | Total Length (mils) | Propagation Delay (ps/inch) | Total Delay (ns) | DQS to CLK Delay (ns) | Board Delay (ns) |

| CLK0 | 55.77 | 2195.9 | 470 | 2665.9 | 160 | 0.427 | ||

| CLK1 | 55.77 | 2195.9 | 470 | 2665.9 | 160 | 0.427 | ||

| CLK2 | 41.43 | 1631.1 | 470 | 2101.1 | 160 | 0.336 | ||

| CLK3 | 41.43 | 1631.1 | 470 | 2101.1 | 160 | 0.336 | ||

| DQS0 | 51.00 | 2008.0 | 504 | 2512.0 | 160 | 0.402 | 0.025 |

|

| DQS1 | 50.77 | 1998.8 | 495 | 2493.8 | 160 | 0.399 | 0.028 |

|

| DQS2 | 41.59 | 1637.6 | 520 | 2157.6 | 160 | 0.345 | -0.009 |

|

| DQS3 | 41.90 | 1649.4 | 835 | 2484.4 | 160 | 0.398 | -0.061 |

|

| DQ[7:0] | 50.63 | 1993.3 | 465 | 2458.3 | 160 | 0.393 | 0.410 | |

| DQ[15:8] | 50.71 | 1996.4 | 480 | 2476.4 | 160 | 0.396 | 0.411 | |

| DQ[23:16] | 40.89 | 1609.9 | 550 | 2159.9 | 160 | 0.346 | 0.341 | |

| DQ[31:24] | 40.58 | 1597.8 | 780 | 2377.8 | 160 | 0.380 | 0.358 |

如上表所示,DQS 到CLK 必须设置正确的延时时间。

4.2.2 PROM SPI FALSH

MiZ701开发板有一个4bit SPI FLASH,型号是W25Q128FV可以用来保存数据,还有代码。FLASH可以用来初始化PS和PL 部分的子系统。

W25Q128FV主要技术参数

· 128Mbit

· x1, x2, and x4 支持

· 最高时钟 104 MHz, MiZ701 rates @ 100 MHz 4bit模式下可以达到 400Mbs

· 工作于 3.3V

为了正确使用Z SPI FLASH 工作于 4bit 模式,MIO[1:0,8]需要被正确设置。MIO[8]需要通过一个20K的上电阻上拉到3.3V,让4bit FLASH 可以工作于反馈模式。Zynq只支持24bit的寻址空间, 256Mb是通过内部bank的切换实现全部访问。目前IMPACT 还不支持S25FL256S。

表4-2-3 MiZ701 SPI FLASH 的管脚定义

| Signal Name | Description | Zynq Pin | MIO | QSPI Pin |

| DQ0 | Data0 | B8 (MIO Bank 0/500) | 1:6 | 5 |

| DQ1 | Data1 | D6 (MIO Bank 0/500) | 2 | |

| DQ2 | Data2 | B7 (MIO Bank 0/500) | 3 | |

| DQ3 | Data3 | A6 (MIO Bank 0/500) | 7 | |

| SCK | Serial Data Clock | D5 (MIO Bank 0/500) | 6 | |

| CS | Chip Select | A7(MIO Bank 0/500) | 1 | |

| FB Clock | QSPI Feedback | D5 (MIO Bank 0/500) | 8 | N/C |

4.2.3 TF 卡

4.2.3 TF 卡

MiZ701 PS 部分连接了TF卡,支持SDIO模式。TF卡可以用来保存数据和程序,比如LIUNX操作系统。PS部分相关的引脚是 MIO[40-47],其中包含了TF卡检测信号,和TF卡由于没有写保护功能,因此写保护不起作用。

由于TF卡工作在3.3V 而MiZ701工作于1.8V 因此使用了TXS02612 作为电平桥接芯片。

由于TF卡工作在3.3V 而MiZ701工作于1.8V 因此使用了TXS02612 作为电平桥接芯片。

Zynq只支持主机模式,为了能够从TF卡启动需要设置MIO[2:6].并且设置JE7接到GND.

TF卡原理图

表4-2-4 MiZ701 TF卡管脚定义

| Signal Name | Description | Zynq Pin | MIO | Level Shift Pin | TF Card Pin |

| CLK | Clock | d14 (MIO Bank 1/501) | 40 | Pass-Thru | 5 |

| CMD | Command | C17 ((MIO Bank 1/501) | 41 | Pass-Thru | 2 |

| Data[3:0] | Data | MIO Bank 1/501 D0: E12 D1: A9 D2: F13 D3: B15 | 42:45 | Pass-Thru | Data Pins 7 8 9 1 |

| CD | Card Detect | B14 (MIO Bank 1/501) | 47 | Pass-Thru | CD |

| WP(Not Used) | Write Protect | ((MIO Bank 1/501) | 46 | Pass-Thru | WP |

4.3 USB

MiZ701 USB OTG 采用了IT 的TUSB1210 芯片,在HOST和OTG模式模式下 需要短接JP8 以提供5V电源给设备。

需要短接JP8 以提供5V电源给设备。

表4-3-1USB OTG 管脚定义

| Signal Name | Description | Zynq Pin | MIO | TUSB1210 Pin | USB Conn Pin |

| OTG_Data[8:0] | USB Data lines | MIO Bank 1/501 | 28:39 | Data[7:0] | N/C |

| OTG_CLOCK | USB Clock | MIO Bank 1/501 | 26 | N/C | |

| OTG_DIR | ULPI DIR output signal | MIO Bank 1/501 | 31 | N/C | |

| OTG_STP | ULPI STP input signal | MIO Bank 1/501 | 29 | N/C | |

| OTG_NXT | ULPI NXT output signal | MIO Bank 1/501 | 2 | N/C | |

| OTG_CS · | USB Chip Select | 11 | N/C | ||

| DP | DP pin of USB Connector | N/C | 18 | 2 | |

| DM | DM pin of USB Connector | N/C | 19 | 3 | |

| ID | Identification pin of the USB connector | N/C | 23 | 4 | |

| OTG_RESET_B | Reset | MIO Bank 1/501 | 27 | N/C | |

| OTG_VBUS_OC | VBus Output Control | Bank 34 | L16 | TPS2051 |

4.3.2 MiZ701 USB TO UART

USB TO UART采用了PL2303HXD此芯片支持1.8V-3.3V的IO电平。这样在电脑上可以虚拟出一个RS232使用起来非常方便。

表4-3-2 MiZ701 USB TO UART 管脚定义

| unction in Zynq | Zynq Pin | MIO | Schematic Net Name | PL2303HXD | UART Function in CY7C64225 |

| TX, data out | C12 (MIO Bank 1/501) | 48:49 | USB_1_RXD | 5 | RXD, data in |

| RX, data in | B12 (MIO Bank 1/501) | USB_1_TXD | 1 | TXD, data out |

USB TO UART传输接口图

4.3.3 USB ESD 保护

USB D+/D-采用了一片TE SESD0402Q2UG-0020-090 进行ESD保护。

4.3.4 JTAG接口

4.3.4 JTAG接口

MiZ701的JTAG接口采用了10PIN 2.0间距的接插接口,请使用配套的接口线下载调试程序,以免损坏SOC芯片。

4.4 显示

4.4 显示

HDMI部分采用了PL部分的FPGA资源实现HDMI编解码,可以实现双向传输 。

HDMI 接口连接到了MiZ701的Bank 35,MiZ701没有使用音频输出功能, 信号采用TMDS IO标准。

表4-4-1 MiZ701 HDMI 接口管脚定义

| Signal Name | Description | Zynq pin | BANK |

| HDMI_HDP | Hot Plug Detect signal input | E13 | BANK:34(3V3) |

| HDMI_CEC | E19 | ||

| HDMI_SCL | I2C Interface. Supports CMOS logic levels from 1.8V to 3.3V | G17 | |

| HD_SDA | G18 | ||

| HD_CLKN | HDMI clock | H17 | |

| HD_CLKP | H16 | ||

| HDMI_D0_N | HDMI DATA | D20 | |

| HDMI_D0_P | D19 | ||

| HDMI_D1_N | B20 | ||

| HDMI_D1_P | G20 | ||

| HDMI_D2_N | A20 | ||

| HDMI_D2_P | B19 |

4.4.2 音频

音频解码采用了解码芯片SSM2603CPZ 实现了数字信号变为音频信号,和音频信号变为数字信号。

表4-4-3 MiZ701音频解码部分管脚分配

| Signal Name | Description | Zynq pin | Direction |

| AC-MCLK | Master Clock | T19 | Output |

| AC-BCLK | I2S (Serial Clock) | K18 | Output |

| AC-PBDAT | I2S (Playback Data) | M17 | Output |

| AC-PBLRC | I2S (Playback Channel Clock) | L17 | Output |

| AC-RECDAT | I2S (Record Data) | K17 | Input |

| AC-RECLRC | I2S (Record Channel Clock) | M18 | Output |

| AC-MUTEN | Digital Enable (Active Low) | P18 | Output |

| AC-SDA | I2C (Data) | N17 | Input/Output |

| AC-SCK | I2C (Clock) | N18 | Output |

4.5 系统时钟

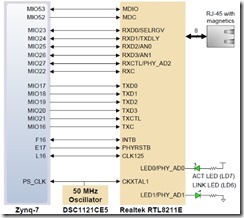

MiZ701 核心板上具备一颗50MHZ的时钟输入到PS和以太网芯片的晶振,以太网的晶振再输出125MHZ的时钟给ZYNQ的以太网部分。 MIZ701的系统时钟可以设置到650MHZ DDR的核心时钟设置到525MHZ(1050MHZ)。

MiZ701 核心板上具备一颗50MHZ的时钟输入到PS和以太网芯片的晶振,以太网的晶振再输出125MHZ的时钟给ZYNQ的以太网部分。 MIZ701的系统时钟可以设置到650MHZ DDR的核心时钟设置到525MHZ(1050MHZ)。

4.6系统复位资源

4.6.1 上电复位(PS_POR_B)

4.6.1 上电复位(PS_POR_B)

Zynq PS部分支持上电复位,此复位会复位整个芯片,此复位信号接到外部电源管理。

4.6.2 PL复位(PROG_B )

这部分是FPGA部分的逻辑资源复位,此管脚接到MiZ701核心板上SW1脚

4.6.3处理器子复位

此复位信号可以手动复位系统,包括PL部分。此管脚寄到MiZ701核心板上SW2脚

4.7用户IO

4.7.1 按钮输入

4.7.1 按钮输入

MiZ701底板具备4个按钮输入,其中2个在PS部分,2个在PL部分,默认上拉,当按钮按下时候接到GND。

表4-7-1 MiZ701按钮输入管脚定义

| Signal Name | Subsection | Zynq pin |

| BTN0 | PL | R18 |

| BTN1 | PL | T17 |

| SW0 | PS | MIO50 |

| SW1 | PS | MIO51 |

4.7.2 LEDS

MiZ701底板具备7个LED输出

表4-7-2 MiZ701 LED 输出

| Signal Name | Subsection | Zynq pin |

| LDA0 | PL | F7 |

| LDA1 | PL | J15 |

| LDA2 | PL | G14 |

| LDA3 | PL | D18 |

| LDB0 | PL | M14 |

| LDB1 | PL | M15 |

| LD9 | PS | MIO7 |

4.7.3 10/100/1000 M以太网

4.7.3 10/100/1000 M以太网

MiZ701采用的PHY型号为RTL8211E-VL,网口自带网络变压

MiZ701 PHY部分硬件接口

| Signal Name | Description | MIO |

| RX_CLK | Receive Clock | 16:27 |

| RX_CTRL | Receive Control | |

| RXD[3:0] | Receive Data | |

| TX_CLK | Transmit Clock | |

| TX_CTRL | Transmit Control | |

| TXD[3:0] | Transmit Data | |

| MDIO | Management Data | 52:53 |

| MDC | Management Clock |

表4-7-3 MiZ701 PHY 管脚定义

4.8 外扩IO

4.8.1 PMOD

4.8.1 PMOD

一共有3组PMOD 分别为PS部分IO、PL部分高速IO、PL部分差分ADC。

| JF1 | |

| PMOD PIN | ZYNQ PIN |

| 1 | MIO0 |

| 2 | MIO10 |

| 3 | MIO12 |

| 4 | MIO14 |

| 7 | MIO15 |

| 8 | MIO13 |

| 9 | MIO11 |

| 10 | MIO9 |

| JE1 | |

| PMOD PIN | ZYNQ PIN |

| 1 | F20 |

| 2 | G20 |

| 3 | H18 |

| 4 | H20 |

| 7 | F19 |

| 8 | G19 |

| 9 | J18 |

| 10 | J20 |

| JA1 | |

| PMOD PIN | ZYNQ PIN |

| 1 | K16 |

| 2 | L14 |

| 3 | K14 |

| 4 | N15 |

| 7 | N16 |

| 8 | J14 |

| 9 | L15 |

| 10 | J16 |

4.8.2 40PIN HEADER

40PIN HEADER 具备36个GPIO

表4-8-1 MiZ701 40PIN HEADER 管脚分配

| PIN Name | Subsection | Zynq pin |

| PIN1 | PL | 5V |

| PIN2 | PL | GND |

| PIN3 | PL | T11 |

| PIN4 | PL | T10 |

| PIN5 | PL | T12 |

| PIN6 | PL | U12 |

| PIN7 | PL | V12 |

| PIN8 | PL | W13 |

| PIN9 | PL | U18 |

| PIN10 | PL | U19 |

| PIN11 | PL | T14 |

| PIN12 | PL | T15 |

| PIN13 | PL | W14 |

| PIN14 | PL | Y14 |

| PIN15 | PL | V15 |

| PIN16 | PL | W15 |

| PIN17 | PL | Y16 |

| PIN18 | PL | Y17 |

| PIN19 | PL | U14 |

| PIN20 | PL | U15 |

| PIN21 | PL | V16 |

| PIN22 | PL | W16 |

| PIN23 | PL | Y18 |

| PIN24 | PL | Y19 |

| PIN25 | PL | P14 |

| PIN26 | PL | R14 |

| PIN27 | PL | P15 |

| PIN28 | PL | P16 |

| PIN29 | PL | R16 |

| PIN30 | PL | R17 |

| PIN31 | PL | T16 |

| PIN32 | PL | U17 |

| PIN33 | PL | V17 |

| PIN34 | PL | V18 |

| PIN35 | PL | W18 |

| PIN36 | PL | W19 |

| PIN37 | PL | V20 |

| PIN38 | PL | W20 |

| PIN39 | PL | GND |

| PIN40 | PL | GND |

4.8.3 20PIN HEADER

4.8.3 20PIN HEADER

20PIN HEADER 具备14个GPIO

表4-8-2 MiZ701 20PIN HEADER 管脚分配

| PIN Name | Subsection | Zynq pin |

| PIN1 | PL | 3V3 |

| PIN2 | PL | GND |

| PIN3 | PL | L20 |

| PIN4 | PL | M20 |

| PIN5 | PL | J19 |

| PIN6 | PL | K19 |

| PIN7 | PL | N20 |

| PIN8 | PL | P20 |

| PIN9 | PL | L19 |

| PIN10 | PL | M19 |

| PIN11 | PL | H15 |

| PIN12 | PL | G15 |

| PIN13 | PL | U20 |

| PIN14 | PL | P19 |

| PIN15 | PL | T20 |

| PIN16 | PL | R19 |

| PIN17 | GND | |

| PIN18 | NC | |

| PIN19 | PL | NC |

4.9 配置

Zynq 支持多种boot 方式,当上电后,zynq 会根据模式管脚的设定选用boot的方式。Zynq支持的boot方式有:NOR, NAND, Quad-SPI, SD Card or JTAG 。默认方式是从SD卡启动。

MIO[8:2] 是模式管脚1其功能如下

· MIO[2]/Boot_Mode[3]设置JTAG模式

· MIO[5:3]/Boot_Mode[2:0] 选择Boot模式

· MIO[6]/Boot_Mode[4] 使能内部PLL

· MIO[8:7]/Vmode[1:0] 用于配置

MiZ701模式选择通过拨码开关来实现,当拨码开关ON状态接通到GND 否则接通到3V3.

表4-9-1 MiZ701 模式位

这里有个疑问,众所周知zynq具有多种启动方式:NOR, NAND, Quad-SPI, SD Card 以及JTAG 。zynq如何判断到底从哪里启动呢?事实上,当上电后,zynq 会根据模式管脚的设定选用boot的方式。而这个管脚的设定是通过MiZ701按键旁的拨码开。

SD卡启动模式选择拨码开关1-2-5-6 为ON 接到GND 3-4 为OFF 上拉到VCC

QSPI FLASH启动模式选择拨码开关1-2-3-5-6为ON 接到GND 4 为OFF 上拉到VCC

MiZ701模式选择通过拨码开关来实现,当拨码开关ON状态接通到GND 否则接通到3V3.

MiZ701通过拨码开关设置MIO的电平状态

我们的开发板MiZ701默认拨码的顺序,就是默认的SD卡启动,具体参看模式位应该如何选择:

· MIO[2]/Boot_Mode[3]设置JTAG模式

· MIO[5:3]/Boot_Mode[2:0] 选择Boot模式

· MIO[6]/Boot_Mode[4] 使能内部PLL

· MIO[8:7]/Vmode[1:0] 用于配置

PUDC_B 管脚控制内部IO是上拉还是下拉,当配置成功后,核心板LD4、底板LD9会被点亮。

MiZ701的JTAG接口采用了10PIN 2.0间距的接插接口,请使用配套的接口线下载调试程序,以免损坏SOC芯片。

4.10 电源管理

输入电压5V 输出3.3V 1.8V 1.5V 1.0V 0.75V。电源方案采用了TPS62130,此芯片外围简单,转换效率高,电流可以达到3A。MAX1510ETB是专用的DDR电源管理芯片。

TPS62130电源管理方案

TPS62130电源管理方案图

MAX1510 DDR专用管理芯片方案图

五、 ZYNQ-7Z020 BANK分布

5.1如图所示为ZYNQ-7000CLG400 IOBANK 的分别情况

| 版本日期 | 版本号 | 修改原因 |

| 1.0 | 初始版本 | |

六、 联系方式

官方论坛:http://www.osrc.cn/

淘宝旗舰店铺:http://osrc.taobao.com/

QQ群:86730608 34215299