verilog中,一般:

input默认为wire型;

output信号可以是wire型,也可以是reg型(在always或initial中被赋值);

inout是双向信号,一般将其设为tri型,表示其有多个驱动源;

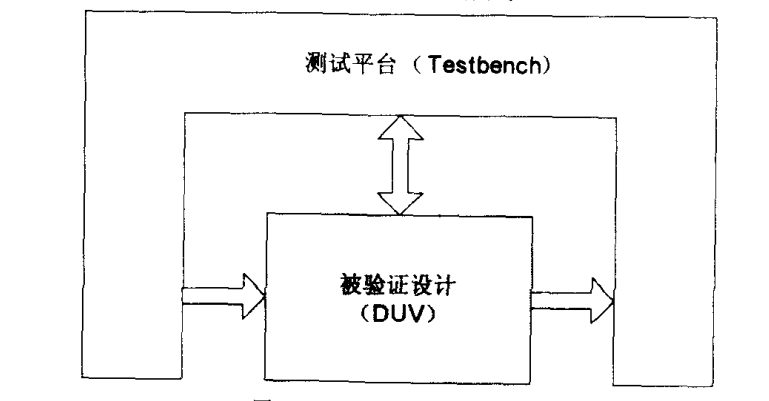

测试脚本编写步骤:1、例化 2、激励 3、结果

在测试脚本中:

input—>reg

output—>wire

inout—>wire

1、时钟信号产生

方法1:

parameter PERIOD = 20;

initial begin

clk = 0;

forever #(PERIOD/2) clk = ~clk;

end

方法2:

parameter PERIOD = 20;

always begin

#(PERIOD/2) clk = 0;

#(PERIOD/2) clk = 1;

end

2、复位信号产生

方法1:封装成一个task,复位的时候直接调用

initial begin

rst_task(100);//定义复位时间

$stop;

task reset_task;

input [15:0] reset_time;

begin

rst = 0;

#rst_time;

rst = 1;

end

endtask

方法2:

initial begin

rst = 0;

#100;

rst = 1;

#2000;

$stop;

举个例子:

1 `timescale 1 ns/ 1 ns 2 module tx_module_vlg_tst(); 3 4 reg CLK; 5 reg RSTn; 6 reg [7:0] TX_Data; 7 reg TX_En_Sig; 8 // wires 9 wire TX_Done_Sig; 10 wire TX_Pin_Out; 11 12 //-------------------------------------------------------- 13 tx_module i1 ( 14 .CLK(CLK), 15 .RSTn(RSTn), 16 .TX_Data(TX_Data), 17 .TX_Done_Sig(TX_Done_Sig), 18 .TX_En_Sig(TX_En_Sig), 19 .TX_Pin_Out(TX_Pin_Out) 20 ); 21 22 //-------------------------------------------------------- 23 initial 24 begin 25 RSTn = 0; #1000 RSTn = 1; 26 CLK = 1; forever #25 CLK = ~CLK; 27 end 28 29 //-------------------------------------------------------- 30 reg [3:0] i; 31 32 always@(posedge CLK or negedge RSTn) 33 if(!RSTn) 34 begin 35 TX_En_Sig <= 1'b0; 36 TX_Data <= 8'd0; 37 i <= 4'd0; 38 end 39 else 40 case(i) 41 42 0: 43 if(TX_Done_Sig) begin TX_En_Sig <= 1'b0;i <= i +1'b1;end 44 else begin TX_Data <= 8'b0101_0101;TX_En_Sig <= 1'b1;end 45 46 1: 47 i <= i; 48 endcase 49 50 //-------------------------------------------------------- 51 endmodule