06_基于FPGA的秒表数码管显示

实验原理

数码管就是由若干个LED灯组合而成的器件.如八段数码管就是由八个LED灯相互并联组成的,所以八个LED灯会有一个公共端点,如果是这个公共端点都是阳极,称为共阳数码管,如果公共端点是阴极,称为共阴数码管。

共阳八段数码管

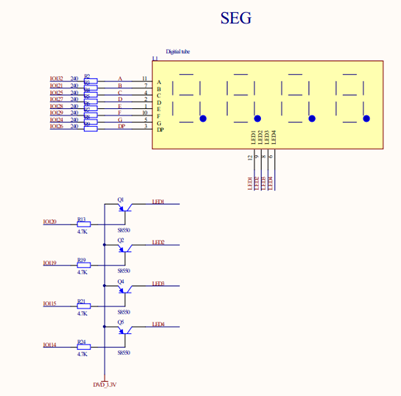

由于LED静态显示需要占用较多的I/O口,且功耗较大,因此在大多数场合通常不采用静态显示,而采用动态扫描的方法来控制LED数码管的显示。动态显示的特点是将8位数码管的段选线并联在一起,由位选线控制是哪一位数码管有效。点亮数码管采用动态扫描显示。

所谓动态扫描显示即轮流向各位数码管送出字形码和相应的位选,只要扫描显示速度够快,利用发光管的余辉和人眼视觉暂留作用,使人的感觉好像各位数码管同时都在显示。动态显示的亮度比静态显示要差一些,所以在选择限流电阻时应略小于静态显示电路中的。动态扫描显示时刷新频率最好大于50HZ,即显示一轮的时间不超过20ms,每个数码管显示时间不能太长也不能太短,时间太长会影响刷新率,导致总体显示呈现闪烁的现象,时间太短发光二极管的电流导通时间也就短,会影响总体的显示亮度。一般控制在1ms左右最佳。

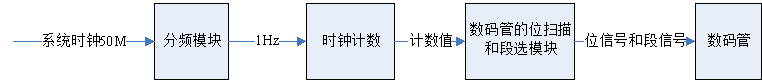

秒表的设计原理:首先通过分频器产生一个频率为1Hz的时钟作为计数源,设置两个寄存器分别用来存储计数值,一个为寄存个位数,一个寄存十位数。同时产生一个数码管位选时钟,用来对数码管的位选进行扫描,这里仅需要两位数码管。

设计的原理框图:

硬件原理图

实验代码

/********************************版权声明************************************** ** 大西瓜团队 ** **----------------------------文件信息-------------------------- ** 文件名称: second.v ** 创建日期: ** 功能描述:秒表数码管显示 ** 硬件平台:大西瓜第三代开发板,http://daxiguafpga.taobao.com ** 版权声明:本代码属个人知识产权,本代码仅供交流学习. **---------------------------修改文件的相关信息---------------- ** 修改人: ** 修改日期: ** 修改内容: *******************************************************************************/ module second( clk, //clk:50MHZ时钟输入 duan, //duan:数码管段码 wei //wei:数码管位码 ); input clk; output [7:0] duan; output [1:0] wei; reg [7:0]duan; reg [1:0]wei;

integer count; //1HZ时钟计数器 integer count2; //扫描时钟计数器 reg clk_1hz; //1HZ时钟信号

reg [3:0]ge; //数码管个位数BCD码 reg [2:0]shi; //数码管十位BCD二进制码

reg clk_scan; //数码管扫描时钟 reg select;

always @(posedge clk)//1HZ时钟进程 begin if(count==25000000) begin clk_1hz=~clk_1hz; count=0; end else count=count+1'b1; end

always @(posedge clk_1hz)//秒表功能进程 begin if(ge==4'b1001) begin ge=4'b0000; if(shi==3'b101) shi=3'b000; else shi=shi+1'b1; end

else ge=ge+1'b1; end

always @(posedge clk)//数码管扫描时钟产生进程 begin if(count2==50000) begin count2=0; clk_scan=~clk_scan; end else count2=count2+1; end

always @(posedge clk_scan) begin select=select+1'b1; end

always @(ge or shi or select) begin if(select==1'b1) begin wei=2'b10;//秒表个位数显示 case(ge) 4'b0000:begin duan=8'b1100_0000;end 4'b0001:begin duan=8'b1111_1001;end 4'b0010:begin duan=8'b1010_0100;end 4'b0011:begin duan=8'b1011_0000;end 4'b0100:begin duan=8'b1001_1001;end 4'b0101:begin duan=8'b1001_0010;end 4'b0110:begin duan=8'b1000_0011;end 4'b0111:begin duan=8'b1111_1000;end 4'b1000:begin duan=8'b1000_0000;end 4'b1001:begin duan=8'b1001_1000;end default duan=8'bx; endcase end else begin

wei=2'b01;//秒表十位数显示 case(shi) 3'b000:duan=8'b1100_0000; 3'b001:duan=8'b1111_1001; 3'b010:duan=8'b1010_0100; 3'b011:duan=8'b1011_0000; 3'b100:duan=8'b1001_1001; 3'b101:duan=8'b1001_0010; 3'b110:duan=8'b1000_0011; default duan=8'bx; endcase end end

endmodule |

实验操作

实验效果

大西瓜FPGA-->https://daxiguafpga.taobao.com

配套开发板:https://item.taobao.com/item.htm?spm=a1z10.1-c.w4004-24211932856.3.489d7241aCjspB&id=633897209972

博客资料、代码、图片、文字等属大西瓜FPGA所有,切勿用于商业! 若引用资料、代码、图片、文字等等请注明出处,谢谢!

每日推送不同科技解读,原创深耕解读当下科技,敬请关注微信公众号"科乎"。