一、移位器(shifter)

作用:移位器和循环移位器用于移动位并完成2的幂的乘法或除法。

分类:

逻辑移位器——左移(LSL)或右移(LSR),以0填充空位。11001 LSR 2 =00110; 11001 LSL 2 = 00100;(veilog 操作符号>> or <<)

算数移位器——算数左移(ASL)与逻辑左移相同,但算数右移(ASR)时会把原来数据的最高有效位填充在数据的最高有效位上,对于有符号数的乘法或除法有用。11001 ASR 2 = 11110; 11001 ASL 2 =00100;(verilog操作符号>>> or <<<)

循环移位器——循环移动数字,从一端移走的位重新填充到另一端的空位。11001 ROR 2 = 01110;11001 ROL 2 = 00111。

二、移位寄存器(shift register)

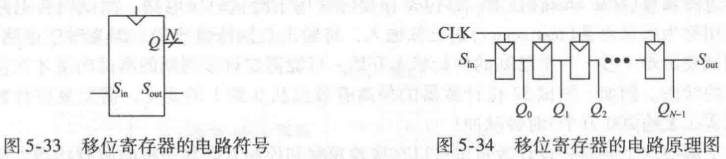

输入:包括时钟clk,串行输入Sin,串行输出Sout和N位并行输出QN-1:0。

工作原理:在时钟的边沿,从Sin移入一个新的位,所有后续内容都向前移动,最后一位在Sout中。

作用:可以作为串行到并行(serial-to-parrallel)的转换器,输入由Sin提供,经N个周期后,前面的N位输入可以在Q中进行并行访问。

组成:如图5-34所示,N位的移位寄存器由N个触发器串联而成,有些移位寄存器还有触发器的复位信号。

相关电路:包含并行到串行转换器(parrallel-to-serial)的移位寄存器,并行加载N位,然后依次移出一位。

工作原理:相比于移位寄存器增加了并行输入DN-1:0和控制信号Load。当Load信号有效时,触发器从D中并行加载数据;否则正常移位。

通用移位寄存器

作用:后续补全

//通用移位寄存器

module Universal_Shift_Reg#(parameter word_size = 8)( output reg[word_size-1:0] Data_out, output MSB_out, LSB_out, input [word_size-1:0] Data_in, input MSB_in, LSB_in, input s0, s1, clk, rst ); assign MSB_out = Data_out[word_size-1]; assign LSB_out = Data_out[0]; always @(posedge clk) begin if(rst==1'b1) Data_out <= 0; else case({s1, s0}) 0: Data_out <= Data_out; //maintain 1: Data_out <= {MSB_in, Data_out[word_size-1:1]}; //MSB shift 2: Data_out <= {Data_out[word_size-2:0], LSB_in}; //LSB shift 3: Data_out <= Data_in; //parallel input endcase end endmodule

移位寄存器

作用

module shift_reg#(parameter word_size = 4)( output reg_out, input clk, rst,reg_in ); reg [word_size-1:0] reg_data;

assign reg_out = reg_data[0]; always @(posedge clk, negedge rst) if(!rst) reg_data <= {word_size{1'b0}}; //nonblock assignment else reg_data <= {reg_in, reg_data[word_size-1:1]}; endmodule

桶形移位寄存器

作用

module barrel_reg #(parameter word_size = 8)( output reg [word_size-1:0] data_out, input [word_size-1:0] data_in, input load, clk, rst );

always @(posedge clk, posedge rst) begin if(rst) data_out <= {word_size{1'b0}}; else if(load) data_out <= {data_in[word_size-2:0], data_in[word_size-1]}; end endmodule

算术移位寄存器

// 移一位和八位的算数寄存器 module top_module( input clk, input load, input ena, input [1:0] amount, input [63:0] data, output reg [63:0] q); always @(posedge clk) if(load) q <= data; else if(ena) begin case(amount) 2'b00: q <= {q[62:0], 1'b0}; 2'b01: q <= {q[55:0], 8'b0}; 2'b10: q <= {q[63], q[63:1]}; 2'b11: q <= {{8{q[63]}}, q[63:8]}; endcase end else q <= q; endmodule

扫描链(scan chain)

作用:通过扫描链技术,移位寄存器经常用于测试时序电路。

原因:由于时序电路中存在状态,测试相对困难。从一个已知的初始装填开始,可能需要许多周期的测试向量才能使电路进入期望状态。为解决这一问题,希望可以通过增加测试模式来实现直接观察和控制有限状态机的所有状态。。然而由于系统中触发器太多以至于无法为每个触发器分配一个管脚进行读写。但是,系统中所有触发器都连接在扫描链的以为寄存器中。

测试模式:允许自由地向所有触发器的内容读出或者加载所需要的值。在测试模式中,扫描链通过Sin和Sout串行地移出内容或写入新的内容。