今天自己写bootloader做时钟初始化时遇到的问题,特记录下来。为了方便理解,我大部分都有截图, 在此我先说明下,图均来自数据手冊。也希望看了本篇文章的同志多多參看数据手冊才干理解的更加透彻,才干真正的锻炼自己的能力。以下程序部分我也拆分成了5个部分分别解释,最后也给出了整个程序。本文假设有什么错误的地方。欢迎各位批评指正。不甚感激。

6410有3个内部PLL(Phase Locked Loop:为锁相回路或锁相环,用来统一整合时脉讯号,使内存能正确的存取资料。PLL用于振荡器中的反馈技术。 很多电子设备要正常工作,通常须要外部的输入信号与内部的振荡信号同步。利 用锁相环路就能够实现这个目的。

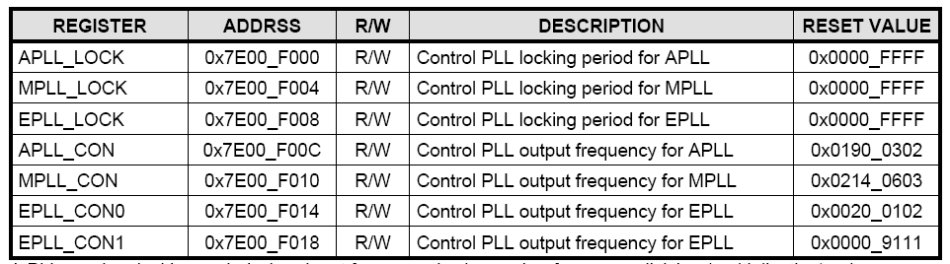

)各自是:APLL、MPLL、EPLL。他们被以下7个寄存器控制:

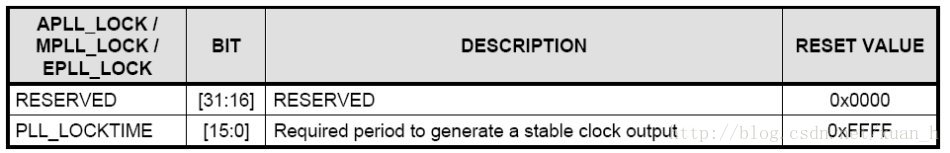

1、 当中前3个寄存器见下图:

所以相应的初始化代码为:

//set the clock time

ldr r0, =0x7e00f000 //APLL_CLOCK

ldr r1, =0xffff

str r1, [r0]

str r1, [r0, #0x4] //MPLL_CLOCK

str r1, [r0, #0x8] //EPLL_CLOCK

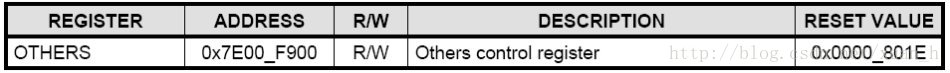

2、 接着设置时钟为异步模式,通过others寄存器设置。图和代码例如以下:

这是others被设置的相应的位。这里截取得当中用到的部分。

//set Async mode

ldr r0, =0x7e00f900 //OTHERS

ldr r1, [r0]

bic r1, #0xc0

str r1, [r0]

//wait for Async mode

loop1:

ldr r0, =0x7e00f900

ldr r1, [r0]

and r1, #0xf00

cmp r1, #0x00

bne loop1

3、6410有几个时钟分频器。以支持各种工作时钟频率。时钟分频比能够被CLK_DIV0、 CLK_DIV1、CLK_DIV2控制。如今我们设置CLK_DIV0。

注:CLK_DIV0 mainly controls the system clocks and special clocks of multimedia IPs。CLK_DIV1 controls MMC, LCD, TV scaler, and UHOST clocks;CLK_DIV2 controls SPI, AUDIO, UART, and IrDA clocks。寄存器的图太大,没附。希望大家自己參看数据手冊。上面有很具体的说明,搜索寄存器名字就可找到。

汇编代码例如以下:

//set the DIV

#define ARM_RATIO 0 //ARM_CLK=DOUTAPLL / (ARM_RATIO + 1)

#define MPLL_RATIO 0 //DOUTMPLL = MOUTMPLL / (MPLL_RATIO + 1)

#define HCLK_RATIO 1 //HCLK = HCLKX2 / (HCLK_RATIO + 1)

#define HCLKX2_RATIO 1 //HCLKX2 = HCLKX2IN / (HCLKX2_RATIO + 1)

#define PCLK_RATIO 3 //PCLK = HCLKX2 / (PCLK_RATIO + 1) <=66Mhz

ldr r0, =0x7e00f020 //CLK_DIV0

ldr r1, =(ARM_RATIO) | (MPLL_RATIO << 4) | (HCLK_RATIO << 8) | (HCLKX2_RATIO << 9) | (PCLK_RATIO << 12)

str r1, [r0]

4、接着我们设置输出频率,通过APLL_CON、MPLL_CON设置。

以下先给出计算公式和典型值。

(1) 典型值例如以下图:

(2) 计算公式:FOUT = MDIV * FIN / (PDIV X 2^SDIV)

汇编代码例如以下:

//init the frequence

#define SDIV 1

#define PDIV 3

#define MDIV 266 //final 532Mhz

ldr r0, =0x7e00f00c //APLL_CON

ldr r1, =(1 << 31) | (MDIV << 16) | (PDIV << 8) | (SDIV)

str r1, [r0]

ldr r0, =0x7e00f010 //MPLL_CON

str r1, [r0]

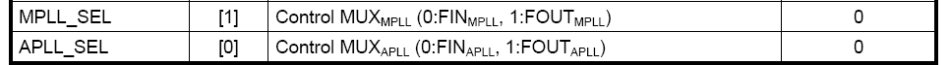

5、最后我们还得设置下clk_src这个寄存器。

6410有很多时钟源。当中包含3个PLL输出。外部振荡器。外部时钟。以及从GPIO配置的其它时钟源.CLK_SRC寄存器控制每一个时钟分频器的时钟源。

这里我么用到了它最低的两位,截图例如以下:

汇编代码例如以下:

ldr r0, =0x7e00f01c

ldr r1, =0x03

str r1, [r0]

完整程序代码例如以下:

//set the clock time

ldr r0, =0x7e00f000 //APLL_CLOCK

ldr r1, =0xffff

str r1, [r0]

str r1, [r0, #0x4] //MPLL_CLOCK

str r1, [r0, #0x8] //EPLL_CLOCK

//set Async mode

ldr r0, =0x7e00f900 //OTHERS

ldr r1, [r0]

bic r1, #0xc0

str r1, [r0]

//wait for Async mode

loop1:

ldr r0, =0x7e00f900

ldr r1, [r0]

and r1, #0xf00

cmp r1, #0x00

bne loop1

//set the DIV

#define ARM_RATIO 0 //ARM_CLK=DOUTAPLL / (ARM_RATIO + 1)

#define MPLL_RATIO 0 //DOUTMPLL = MOUTMPLL / (MPLL_RATIO + 1)

#define HCLK_RATIO 1 //HCLK = HCLKX2 / (HCLK_RATIO + 1)

#define HCLKX2_RATIO 1 //HCLKX2 = HCLKX2IN / (HCLKX2_RATIO + 1)

#define PCLK_RATIO 3 //PCLK = HCLKX2 / (PCLK_RATIO + 1) <=66Mhz

ldr r0, =0x7e00f020 //CLK_DIV0

ldr r1, =(ARM_RATIO) | (MPLL_RATIO << 4) | (HCLK_RATIO << 8) | (HCLKX2_RATIO << 9) | (PCLK_RATIO << 12)

str r1, [r0]

//init the frequence

#define SDIV 1

#define PDIV 3

#define MDIV 266 //final 532Mhz

ldr r0, =0x7e00f00c //APLL_CON

ldr r1, =(1 << 31) | (MDIV << 16) | (PDIV << 8) | (SDIV)

str r1, [r0]

ldr r0, =0x7e00f010 //MPLL_CON

str r1, [r0]

ldr r0, =0x7e00f01c

ldr r1, =0x03

str r1, [r0]

mov pc, lr