记录一下芯片时钟相关学习笔记

问题引入:

Q: CPU运行速度很快,但是外设运行的则比较慢,那它们的时钟源怎么匹配呢?

A: 它们有不同的时钟源。

CLOCKS

计算机的心脏,给主板的芯片提供时钟信号,与晶振连接给其他部件提供时钟信号。

WHAT

S3C2440有三种时钟源:

- FCLK(max freq = 400 MHz):用于CPU核。

- HCLK(max freq = 136 MHz):用于AHB总线上的设备,比如CPU核存储器控制器、中断控制器、LCD控制器、DMA和USB主机模块等高性能的设备。

- PCLK(max freq = 68 MHz):用于APB总线上的设备,比如WATCHDOG、IIS、I2C、PWM定时器、MMC接口、ADC、UART、GPIO、RTC和SPI等低速设备。

HOW TO WORK

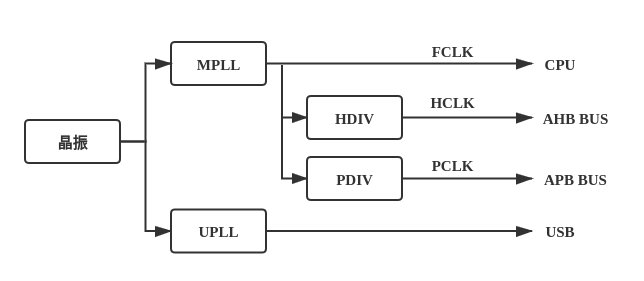

硬件电路上有个12M的晶振,作为时钟源产生12MHz的频率,经过SOC的PLL(锁相环)倍频产生Fclk、Hclk、Pclk。

产生这些时钟源的简要流程可以这样描述:

- 系统刚上电的时候,FCLK即等于外部输入的时钟。一般是12M或者24M的晶振。等待晶振输出稳定(此时FCLK=Fin),reset 信号恢复高电平,CPU 开始执行指令。

- 然后用软件的方式打开MPLL(锁相环电路,用于提高系统时钟频率),把12M或者24M的时钟频率提高到100-400M(针对于S3C2440)。

- 再然后,通过设置一些寄存器(设置分频器),可以改变FCLK、HCLK、PCLk的时钟频率比例(比如说1:2:2)

这样,其他的两个时钟源也就提高了。要明白的是,系统在运行的时候,是三个时钟源一起在工作,分别为不同的设备提供不同的时钟频率。

当然,有些设备对这些频率还不是很“满意”、它会自己进行异步模式的设置或一些倍频或者分频的工作。

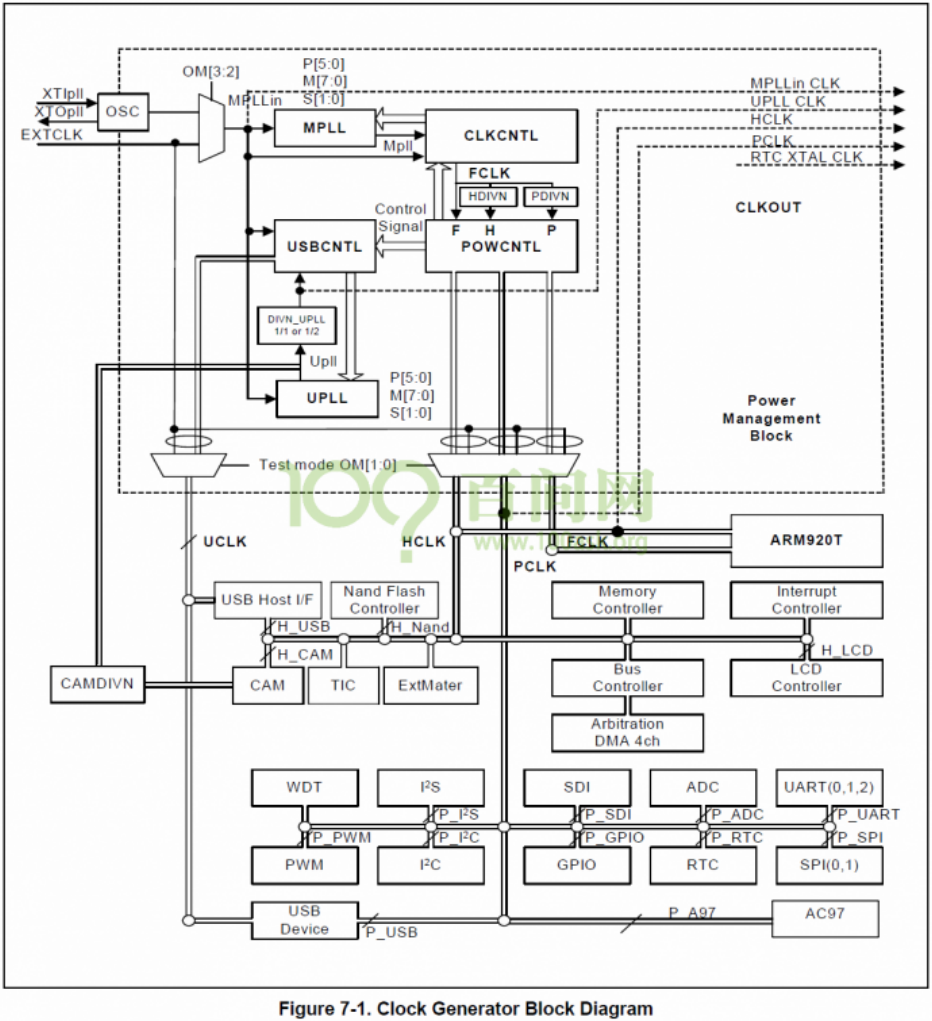

以S3C2440的Clock Generator Block Diagram为例:

可以看到,由于晶振和一个外部时钟接在一个选择器上,这个选择器通过OM[3:2]的值来决定选择哪个时钟源。

然后生成的MPLL(Main PLL)和UPLL(USB PLL),MPLL直接提供给FCLK,通过HDIVN分频给HCLK,通过PDIVN分频给PCLK,再传给下面的各个设备。

TIMER

系统给的时钟(一般是PCLK)进行计数,当数计满了,就会产生一次中断。