make命令作用:

对于一个包括几百个源文件的应用程序,使用make和makefile工具就可以简洁明快地理顺各个源文件之间纷繁复杂的相互关系。而且如此多的源文件,如果每次都要键入gcc命令进行编译的话,那对程序员来说简直就是一场灾难。而make工具则可自动完成编译工作,并且可以只对程序员在上次编译后修改过的部分进行编译。因此,有效的利用make和makefile工具可以大大提高项目开发的效率。

make命令下载:

先更新找到ubuntu-make

sudo apt-get update

sudo apt-get install ubuntu-make

再下载(我Ubuntu上直接有make命令,所以我没使用上面那两个命令,运行下面命令我的make命令更新到了最新版本)

sudo apt-get install make

gcc编译过程:

对一个test.c文件进行编译首先需要使用下面命令

gcc -c test.c

使源文件变成*.o文件

之后使用下面命令

gcc -o test.exe test.o

这条命令的作用就是指出test.exe可执行文件(因为Linux上可执行文件不需要exe结尾,所以你也可以换一个其他名字)的生成需要test.o文件(如果需要更多*.o文件在后面列出就可以)

make如何工作:

make在当前目录下寻找“Makefile”或“makefile”文件

若找到,查找文件中的第一个目标文件.o

若目标文件不存在,根据依赖关系查找.s文件

若.s文件不存在,根据依赖关系查找.i文件

若.i文件不存在,根据依赖关系查找.c文件,此时.c文件一定存在,于是生成一个.o文件,再去执行

makefile文件格式:

<target>: <prerequisites>

[Tab]<commands>

第一行冒号前为目标,冒号后为前置条件;第二行必须由一个Tab键起首,后接命令;目标是必须的,不可省略;前置条件和命令是可选的,但两者必须至少存在一个。

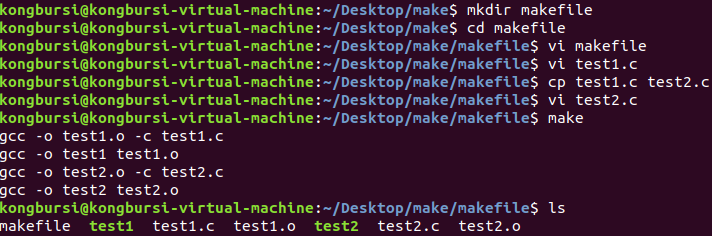

示例:

test2.exe: test2.o

gcc -o test2.exe test2.o

test2.o: test2.c

gcc -c test2.c

这意味着生成test.exe需要前置条件test2.o,生成test.o需要前置条件test2.c

1、test.c文件存在所以会执行下面的代码 gcc -c test2.c

2、test.o文件存在所以会执行下面代码 gcc -o test2.exe test2.o

这样写的限制:用一个Makefile同时编译多个.c文件并生成可执行文件需要添加一个伪可执行文件。makefile 默认只生成第一个可执行文件,所以可以用伪可执行文件,make 过程中并不生成 这个伪可执行文件,在如下代码中,all就是一个伪执行文件。

#makefile

CC=gcc

all:test1 test2

.PHONY:all

test2 :test2.o

$(CC) -o $@ $<

test1 :test1.o

$(CC) -o $@ $<

test2.o:test2.c

$(CC) -o $@ -c $<

test1.o:test1.c

$(CC) -o $@ -c $<

clean:

rm -rf test1 test2 test1.o test2.o

.PHONY:all clean

make的一些选项:

1、-f

直接运行make命令会在当前文件夹下寻找makefile或者Makefile文件,你可以通过-f选项来改变这种默认特性

make -f my_makefile

make 命令会选择扫描 my_makefile 来代替 Makefile。

2、-C

你可以为 make 命令提供不同的目录路径,在寻找 Makefile 之前会切换目录的。这是一个目录,假设你就在当前目录下:

$ ls

file file2 frnd1.cpp

但是你想运行的 make 命令的 Makefile 文件保存在 ../make-dir/ 目录下,你可以这样做:

$ make -C ../make-dir/

make 命令首先切到特定的目录下,在那执行,然后再切换回来。

3、-B

make -B 会强制编译所有的目标文件以及最终的执行文件。

make的语法可以参看:https://blog.csdn.net/qq_35451572/article/details/81092902