前言

对于xilinx移位寄存器IP的使用而言,其内部为SLR16/SRL32实现。

当位深小于32时,其可变延迟是正确的。当大于32,其可变延迟为相同延迟加1。

可能是内部多个SLR32之间插入了一个寄存器导致多了一拍。

流程

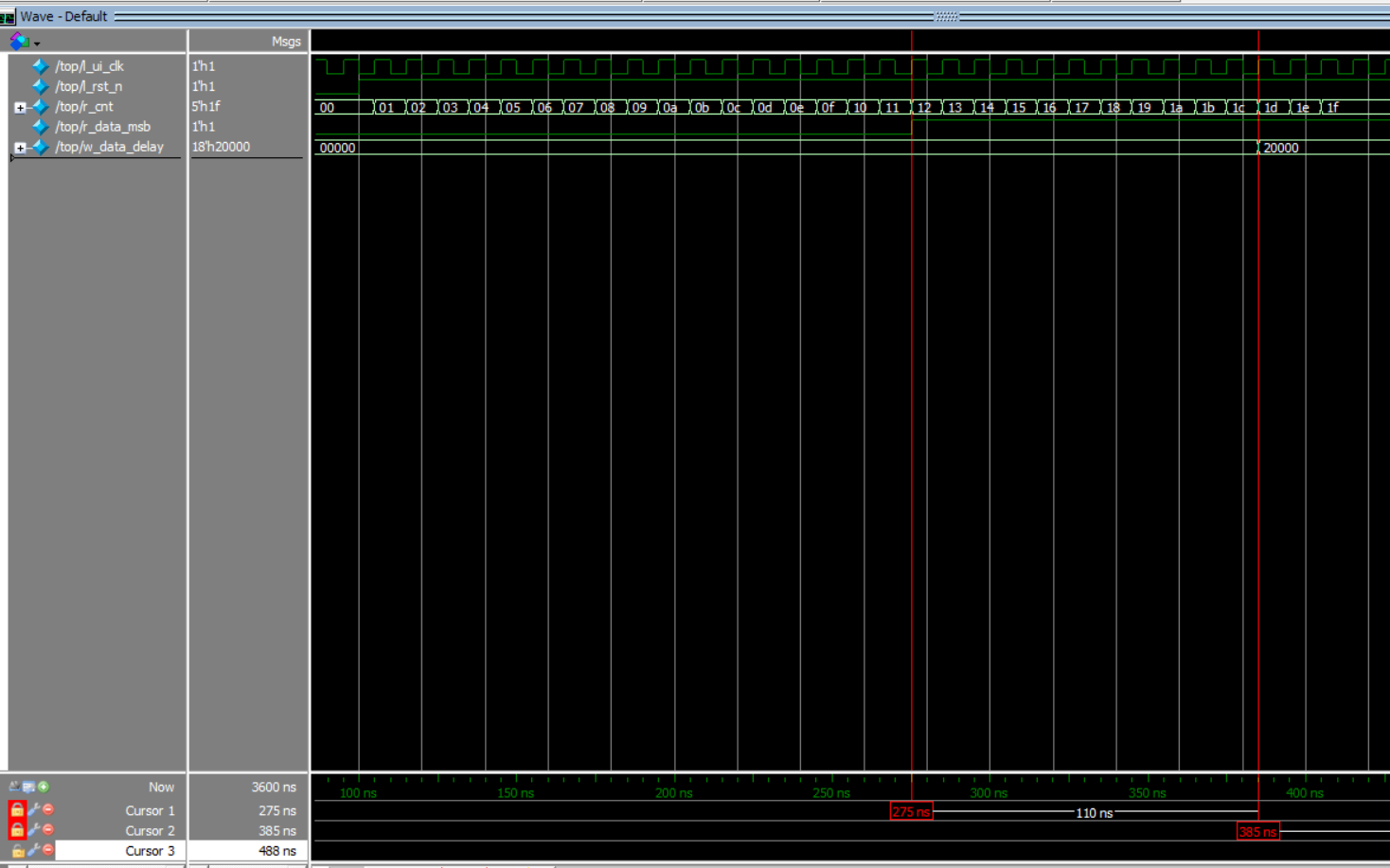

验证位深小于32和位深大于32的移位寄存器可变延迟关系。

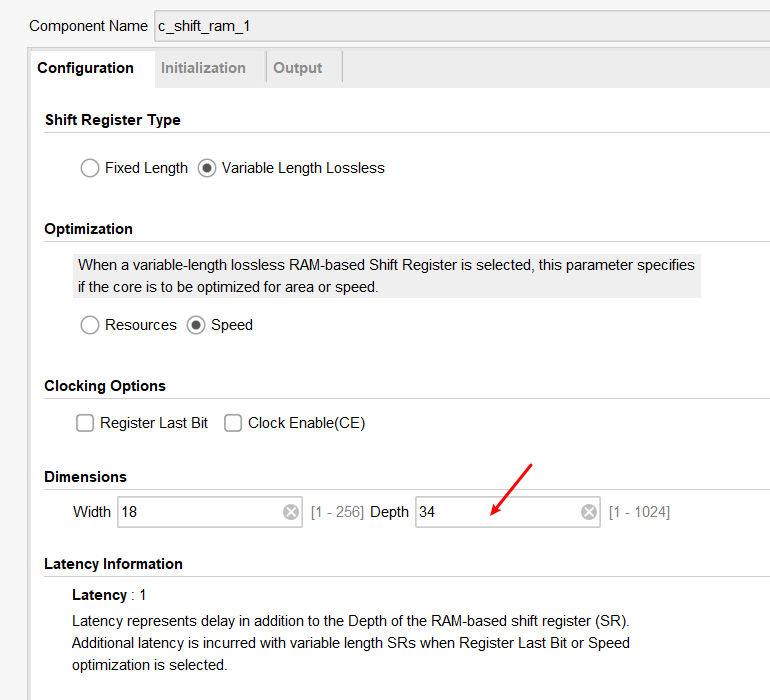

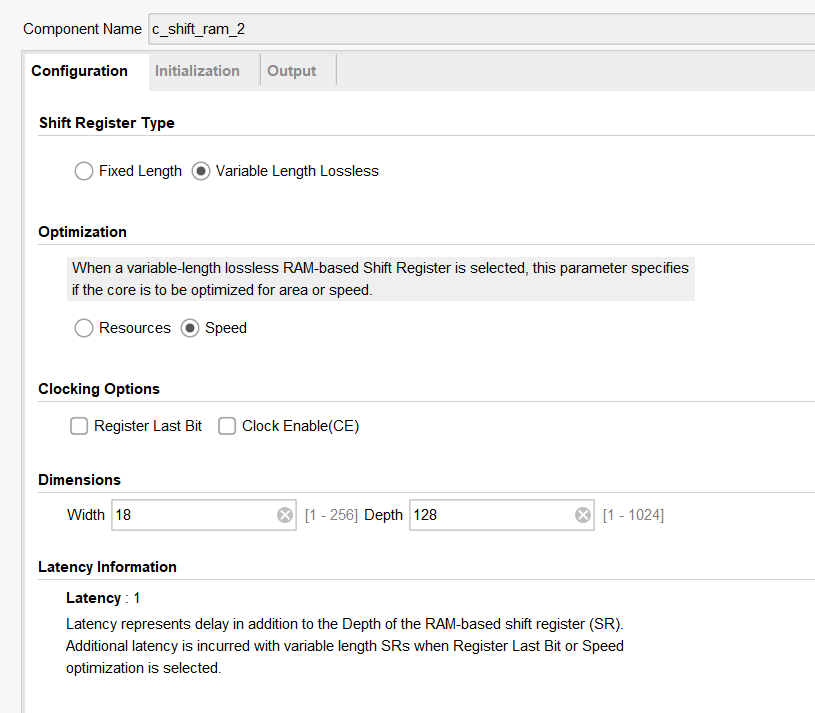

(1)配置两个不同位深的实例。

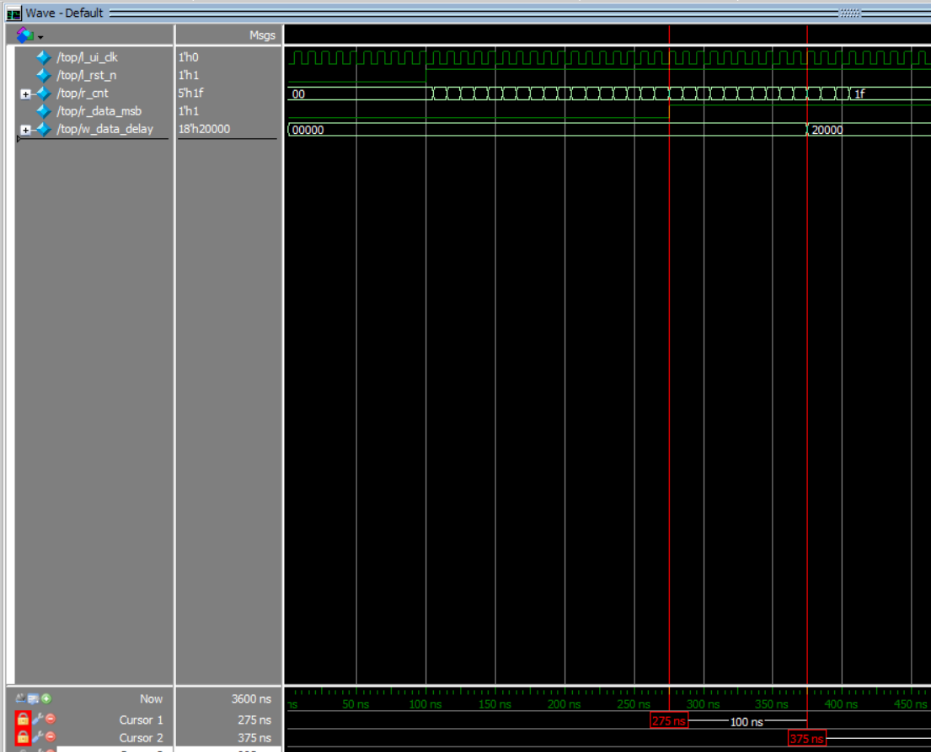

(2)使用相同的可变延迟配置。

(3)仿真看看。

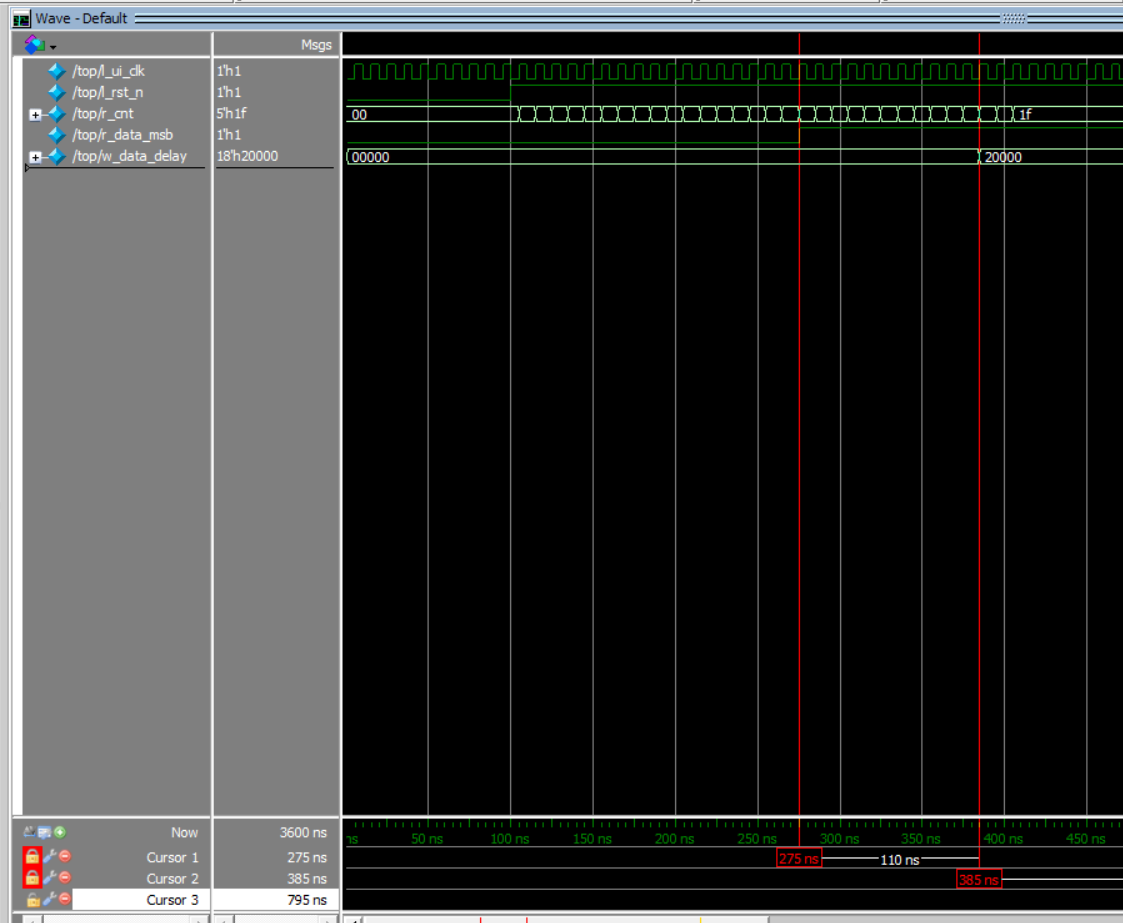

可以看到当位深大于32之后,端口中就不能再是减1,而是减2。否则不是想要的延迟。注意。

更进一步:如果是128位深的呢?结果还是一样的,并不是每个都插了一个寄存器。

所以,只要是位深大于32,那可变位宽就是需要延迟数-2。

以上。