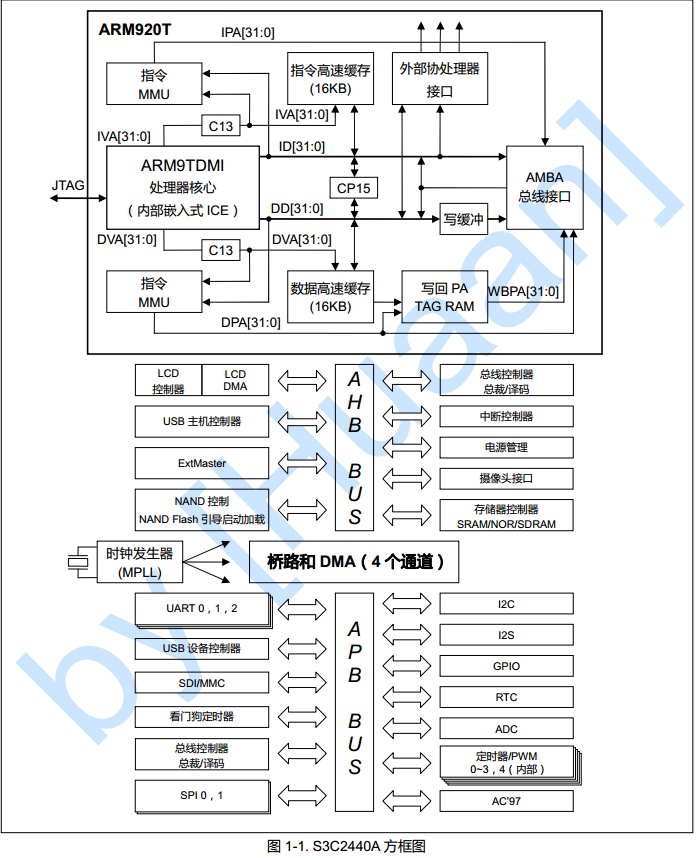

1.整体框图

系统框图

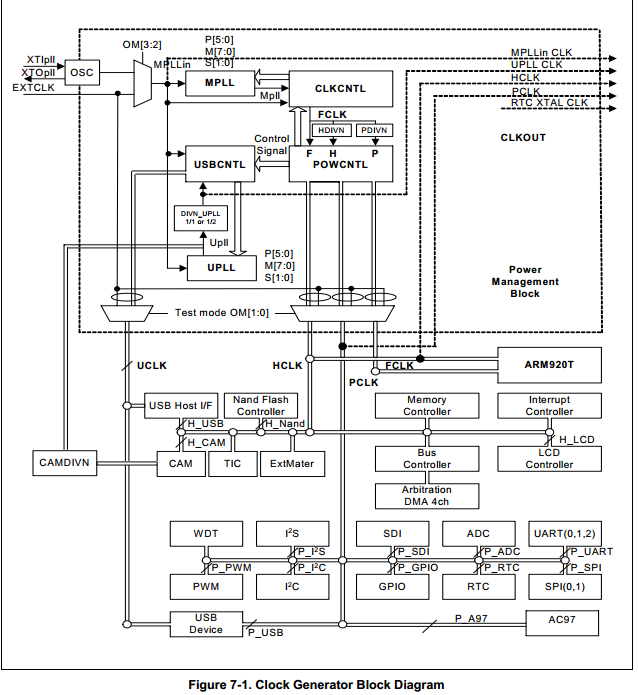

时钟框图

解析:

晶振(OSC)和输入时钟(EXTCLK)通过选择器(OM[3:2])选择时钟源

选择器把选出的频率传到MPLL和UPLL通过对PLL的设置选择输出多高的频率MPLL得到FCLK

FCLK被HDIV分频后得到HCLK;被PDIV分频后得到PCLK

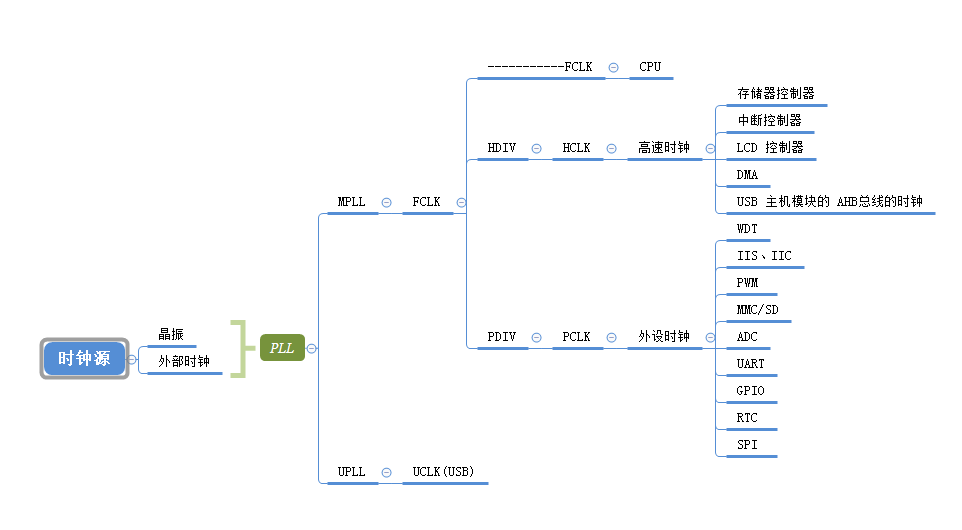

时钟框图简图

工作频率

2.一些概念

FCLK:用于CPU核

HCLK:用于AHB总线上设备。

PCLK:用于APB总线上设备

AHB: 主要用于高性能模块

APB: 主要用于低带宽的周边外设之间的连接

UPLL:专用于USB设备

本开发板上晶振为12MHz

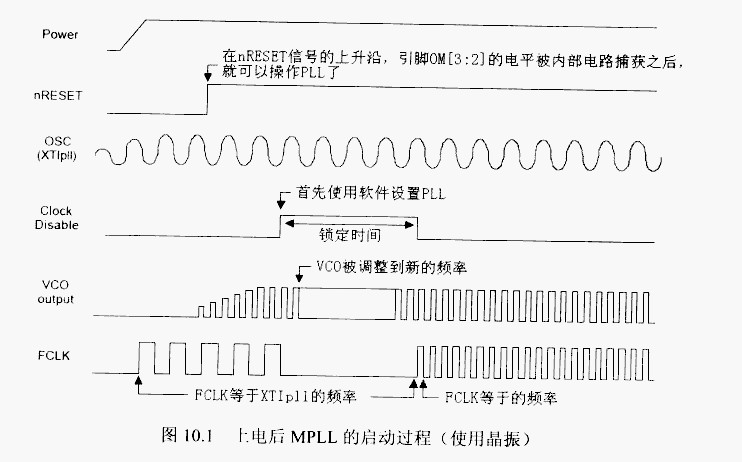

3.上电启动分析

过程分析

上电时,PLL没被启动。FCLK即等于外部输入的时钟,称为Fin。若要提高系统时钟,需要软件来启动PLL。

1).上电几毫秒后,晶振(OSC)输出稳定,FCLK = Fin(晶振频率),nRESET信号恢复高电平后,CPU开始执行指令

2).在nRESET信号的上升沿,引脚OM[3:2]的电平被内部电路捕获,根据OM[3:2]的值,设置FCLK

3).在程序开头启用MPLL,设置MPLL的几个寄存器后,需要等待一段时间(Lock Time),MPLL的输出才能稳定。在这段时间(Lock Time)内,FCLK停振,CPU停止工作。Lock Time的长短有寄存器LOCKTIME设定

4).Lock Time后MPLL输出正常,CPU工作在新的FCLK下

4.寄存器讲解

LOCKTIME

用于设置"Lock Time"的长度。位[31:16]用于UPLL,位[15:0]用于MPLL。一般而言,使用它的默认值即可

MPLLCON

用于设置FCLK和Fin(晶振频率)的倍数

位于[19:12]的值称为MDIV,位于[9:4]的值称为PDIV,位于[1:0]的值称为SDIV。

FCLK = (2 * m * Fin)/(p * 2^s)

m = MDIV + 8, p = PDIV + 2, s = SDIV

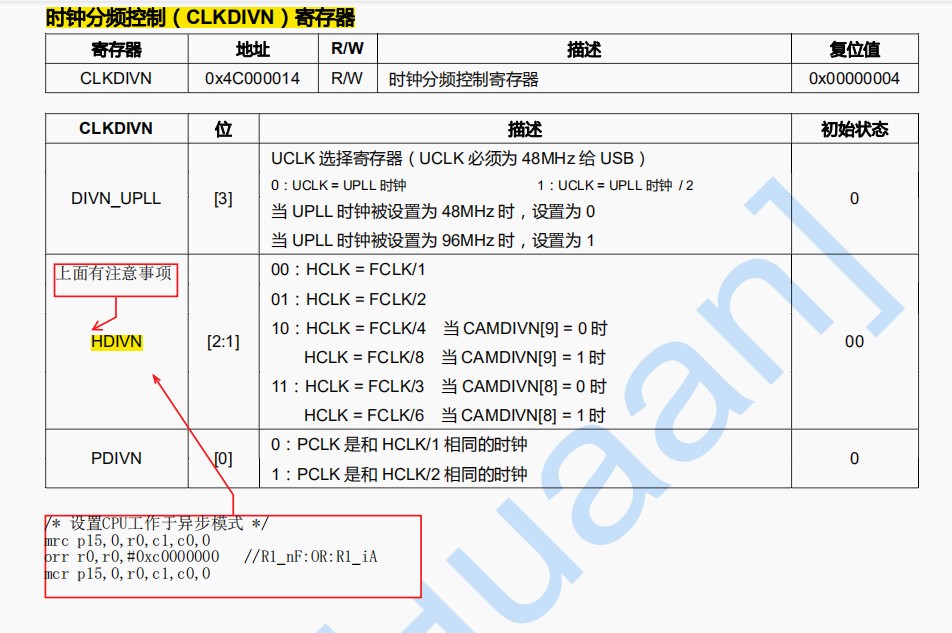

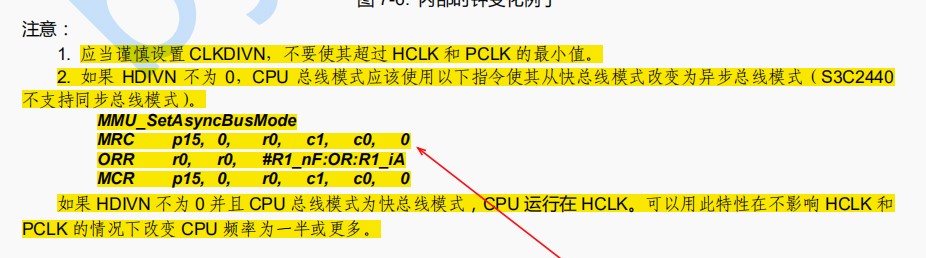

CLKDIVN

用于设置FCLK,HCLK,PCLK三者的比例

/* 设置CPU工作于异步模式 */

mrc p15,0,r0,c1,c0,0

orr r0,r0,#0xc0000000 //R1_nF:OR:R1_iA

mcr p15,0,r0,c1,c0,0

5.程序编写

设置MPLL,FCLK : HCLK : PCLK = 400M : 100M : 50M

/* 设置MPLL,FCLK : HCLK : PCLK = 400M : 100M : 50M */

/* LOCKTIME(0x4c000000) = 0xFFFFFFFF */

ldr r0, =0x4c000000

ldr r1, =0xFFFFFFFF

str r1, [r0]

/* CLKCON(0x4C000014) = 0x5

* tFCLK:tHCLK:tPCLK = 1:4:8

*/

ldr r0, =0x4C000014

ldr r1, =0x5

str r1, [r0]

/* 因为HDIVN不为0

* 所以设置CPU工作于异步模式

*/

mrc p15,0,r0,c1,c0,0

orr r0,r0,#0xc0000000 //R1_nF:OR:R1_iA

mcr p15,0,r0,c1,c0,0

/* 设置MPLLCON(0x4C000004) = ((92 << 12) | (1 << 4) | (1 << 0)) */

ldr r0, =0x4C000004

ldr r1, =(92 << 12) | (1 << 4) | (1 << 0)

str r1, [r0]

/* 一旦设置PLL,就会锁定Lock Time直到PL输出稳定

* 然后CPU工作与新的频率FCLK

*/