缘起

偶然,借到块DE2,开始学习Verilog HDL,也是从语法看起,照着书上敲代码,仿真,做lab,下载,貌似入门了,但总是不确定,总是觉得不能把握什么。偶然看到akuei2的《Verilog哪些事儿--建模篇》V4,觉得很好,遂想记录“打谱”的点滴--是为再笔记。

Lab 1 永远的流水灯

这名字是直接拿来的,起的太好了,不多言。

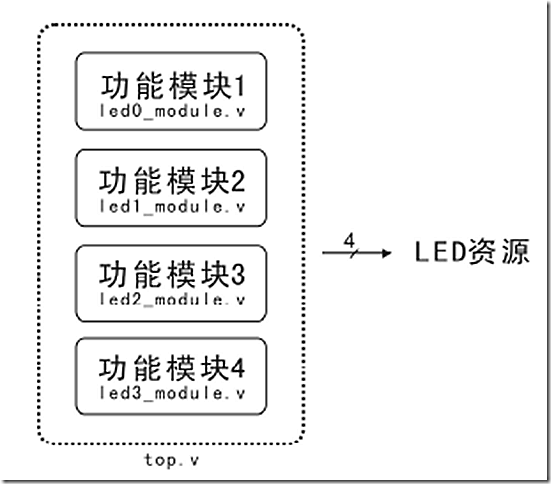

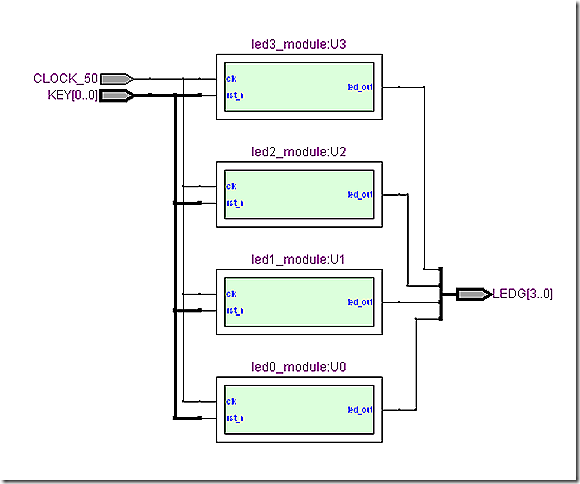

这个实验想阐述并行的思想,用4个类似的模块建立1个并行操作的流水灯模块。每隔100ms流动一下。

代码:

led0_module.v

1 /**

2 * File name: led0_mocule.v

3 *

4 */

5

6 module led0_module

7 (

8 clk, rst_n, led_out

9 );

10

11 input clk;

12 input rst_n;

13 output led_out;

14

15 parameter T10MS = 25'd20_000_000;

16

17 reg [24:0] count;

18

19 always @(posedge clk or negedge rst_n)

20 if (!rst_n)

21 count <= 25'd0;

22 else if (count == T10MS)

23 count <= 25'd0;

24 else

25 count <= count + 1'b1;

26

27 reg rled_out;

28

29 always @(posedge clk or negedge rst_n)

30 if (!rst_n)

31 rled_out <= 1'b0;

32 else if (count >= 25'd0 && count < 25'd5_000_000)

33 rled_out <= 1'b1;

34 else

35 rled_out <= 1'b0;

36

37 assign led_out = rled_out;

38

39 endmodule

40

led1_module.v

1 /**

2 * File name: led1_mocule.v

3 *

4 */

5

6 module led1_module

7 (

8 clk, rst_n, led_out

9 );

10

11 input clk;

12 input rst_n;

13 output led_out;

14

15 parameter T10MS = 25'd20_000_000;

16

17 reg [24:0] count;

18

19 always @(posedge clk or negedge rst_n)

20 if (!rst_n)

21 count <= 25'd0;

22 else if (count == T10MS)

23 count <= 25'd0;

24 else

25 count <= count + 1'b1;

26

27 reg rled_out;

28

29 always @(posedge clk or negedge rst_n)

30 if (!rst_n)

31 rled_out <= 1'b0;

32 else if (count >= 25'd5_000_000 && count < 25'd10_000_000)

33 rled_out <= 1'b1;

34 else

35 rled_out <= 1'b0;

36

37 assign led_out = rled_out;

38

39 endmodule

40

led2_module.v

1 /**

2 * File name: led2_mocule.v

3 *

4 */

5

6 module led2_module

7 (

8 clk, rst_n, led_out

9 );

10

11 input clk;

12 input rst_n;

13 output led_out;

14

15 parameter T10MS = 25'd20_000_000;

16

17 reg [24:0] count;

18

19 always @(posedge clk or negedge rst_n)

20 if (!rst_n)

21 count <= 25'd0;

22 else if (count == T10MS)

23 count <= 25'd0;

24 else

25 count <= count + 1'b1;

26

27 reg rled_out;

28

29 always @(posedge clk or negedge rst_n)

30 if (!rst_n)

31 rled_out <= 1'b0;

32 else if (count >= 25'd10_000_000 && count < 25'd15_000_000)

33 rled_out <= 1'b1;

34 else

35 rled_out <= 1'b0;

36

37 assign led_out = rled_out;

38

39 endmodule

40

led3_module.v

1 /**

2 * File name: led3_mocule.v

3 *

4 */

5

6 module led3_module

7 (

8 clk, rst_n, led_out

9 );

10

11 input clk;

12 input rst_n;

13 output led_out;

14

15 parameter T10MS = 25'd20_000_000;

16

17 reg [24:0] count;

18

19 always @(posedge clk or negedge rst_n)

20 if (!rst_n)

21 count <= 25'd0;

22 else if (count == T10MS)

23 count <= 25'd0;

24 else

25 count <= count + 1'b1;

26

27 reg rled_out;

28

29 always @(posedge clk or negedge rst_n)

30 if (!rst_n)

31 rled_out <= 1'b0;

32 else if (count >= 25'd15_000_000 && count < 25'd20_000_000)

33 rled_out <= 1'b1;

34 else

35 rled_out <= 1'b0;

36

37 assign led_out = rled_out;

38

39 endmodule

40

top_module.v

1 /**

2 * File name: top_module.v

3 * Function: moving lamp, time interval = 0.1s.

4 * Pins: KEY0-rst_n, LEDG3-0

5 * Target board: DE2.

6 * Software: Quartus II 9.1 sp1

7 * ----------------------------

8 * yf.x

9 * 7-11-2011

10 *

11 */

12

13 module top_module

14 (

15 CLOCK_50, KEY, LEDG

16 );

17

18 input CLOCK_50;

19 input [0:0] KEY;

20 output [3:0] LEDG;

21

22 wire led0_out;

23

24 led0_module U0

25 (

26 .clk (CLOCK_50),

27 .rst_n (KEY[0]),

28 .led_out (led0_out)

29 );

30

31 wire led1_out;

32

33 led1_module U1

34 (

35 .clk (CLOCK_50),

36 .rst_n (KEY[0]),

37 .led_out (led1_out)

38 );

39

40 wire led2_out;

41

42 led2_module U2

43 (

44 .clk (CLOCK_50),

45 .rst_n (KEY[0]),

46 .led_out (led2_out)

47 );

48

49 wire led3_out;

50

51 led3_module U3

52 (

53 .clk (CLOCK_50),

54 .rst_n (KEY[0]),

55 .led_out (led3_out)

56 );

57

58 assign LEDG[3:0] = {led3_out, led2_out, led1_out, led0_out};

59

60 endmodule

RTL图

小结

并行思维.